基于FPGA的数字信号相位控制方法的仿真与实现

2016-11-19陈薇

陈薇

[摘要]进行高精度的数字基带信号相位控制方法的研究在实际应用中有着重要的意义。本文介绍了两种不同的相位控制方法,分别是基于存储的相位控制方法和基于正交运算的相位控制方法。本文在建模与仿真的基础上对两种不同相位控制方法的优缺点进行了分析,并针对其算法性能和资源消耗进行了比较。本文在以FPGA为核心的软件无线电开发平台上对基于正交运算的相位控制方法进行了实现。

[关键词]数字基带 相位控制 FPGA

一、引言

随着软件无线电(Software Defined Radio,SDR)技术的不断发展,很多以往在射频或中频范围内需要通过硬件模块来实现的功能逐渐被基带的数字信号处理技术所取代。这不仅可以有效地减小系统的复杂度,还可以极大地提高系统精度和可靠性。相位控制技术被广泛地运用于信号合成、无线信道模拟、多输入多输出(Muhiple-input Multiple-output,MIMO)通信等领域。对高精度的数字基带信号相位控制方法的研究在实际应用中有着重要的意义。在硬件设备的开发过程中,几乎所有算法性能的提高都是以硬件资源的消耗为代价。因此,最大的困难就是在算法性能和资源消耗之间寻求平衡。对于数字信号的相位控制来说,一方面要尽可能地提高相位控制的精度和灵活性,另一方面则要努力将硬件资源的消耗控制在合理的范围之内。

二、相位控制方法的建模与仿真

2.1基于存储的相位控制

最简单的改变数字信号相位的方法是对信号进行存储后输出。基于存储的相位控制系统框图如图1所示。存储的作用是增加信号输出的时延,由于时延和相位的相关性,改变了信号的时延既改变了信号的相位。在这种方案中,只要改变存储深度就能够控制相位变化的范围。

这种方法虽然简单,但是在实际运用中存在两个问题。首先,由于时延只能为正,不能为负,所以相位只能单方向改变。其次,相位变化的最小值由系统采样率决定。设基带信号频率f0为3MHz,系统采样频率fs2为125MHz,则相位变化的最小值θ△可以表示为:(1)

由此可见,在信号频率f0固定的情况下,通过提高采样频率fs可以减小相位变化的最小值θ△,提高相位变化精度。但提高采样频率fs会大大增加系统的运算量,消耗大量硬件资源。事实上,在实际运用中,由于硬件资源的限制,很难将相位变化的最小值降到5°以下。因此,基于存储的相位控制方法无法被运用于对精度要求较高的环境。

2.2基于正交运算的相位控制

在基带处理过程中,一般先对单路数字信号进行数字下变频(DigitalDownConversion,DDC),转变为I、Q两路信号。如果把I、Q两路信号分别看作复信号的实部和虚部,那么改变信号的相位只需要乘上一个幅度为1、相位可变的单位相变因子。

设输入信号为SIF,则SIF可以表示为:(2)

由此可知相位变化值为θ△。

因为θ△可正可负,所以该算法可以实现相位的双向变化。且θ△的取值越小,相位变化的最小值也就越小,精度越高。由于θ△的取值几乎不受硬件条件限制,所以其精度可以轻松地达到1。以内。

使用Matlab软件对以上算法进行建模仿真。基带信号频率f0为3MHz,系统采样频率fs为125MHz。仿真结果如-图2所示,图a设置相位变化值θ△分别为-90°、0°、90°,可以看到仿真结果与设置一致。图b设定相位变化值θ△分别为-1°、0°、1°,并将局部放大,可以看到信号之间微小的相位变化,其结果与设置一致。

三、相位控制方案的设计与实现

本文采用SFF SDR小型软件无线电开发平台对基于正交运算的相位控制算法进行硬件实现。该开发平台由恒润科技有限公司代理进口。其数字基带处理模块的核心是一块Xilinx公司的Virtex4系列FPGA芯片。数据转换模块采用TI公司的ADS5500型号AD芯片和DAC5687型号DA芯片。中频输入信号频率30MHz,基带采样频率125MHz。

3.1基于FPGA的相位控制方案设计

考虑到相位值的有限性,可以将一个周期(通常是-180°-180°)的正弦值和余弦值预先存储在片上ROM中,其占用的存储空间并不大。假设以1。为步进,则只需要360*2个存储单元。通过改变相位控制字,可以选择不同的正弦值和余弦值输出。将正弦值和余弦值与数字下变频之后的I、Q两路信号进行复乘实现相变因子与信号的调制。最后通过数字上变频合成一路输出即可完成基于正交运算的相位控制。方案实现框图如图3所示。

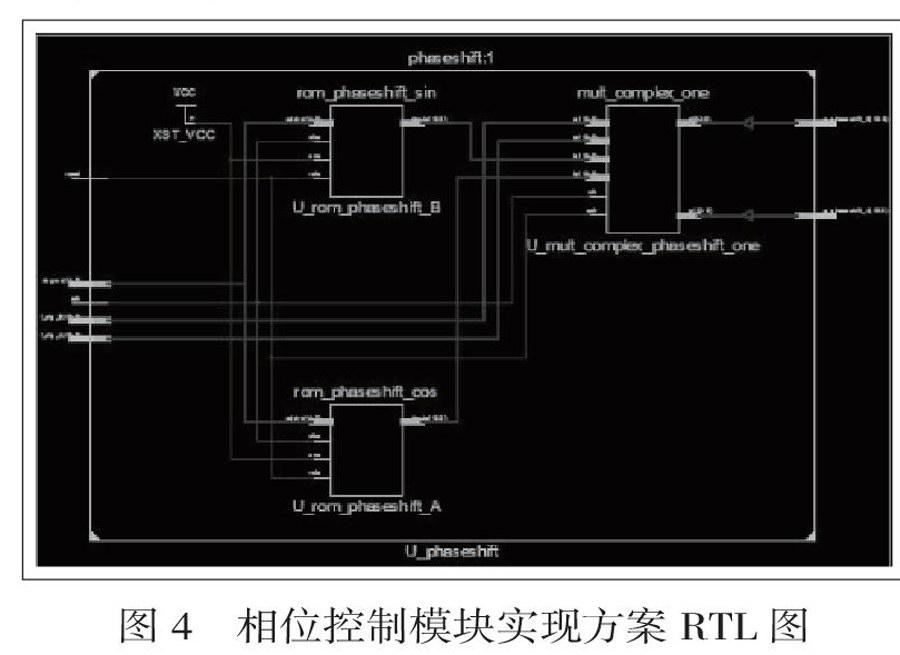

本文开发工具使用Xilinx公司的ISE10.1软件。复乘运算是本方案的核心,可以使用ISE自带的Mult ComplexIPcore方便地实现。相比于代码编写,IPcore有着集成度高、设置简单等优点,熟练掌握各种IPcore已经成为硬件开发的有效手段。

3.2基于FPGA的相位控制方案实现

本方案采样频率fs为125MHz,AD输入信号频移fθIT为30MHz,数字下变频之后的基带信号频率f0为3MHz。方案设计完成之后,ISE软件能够自动生成RTL图(寄存器传输级框图),以方便查看。本方案的RTL图如图4所示。

本文使用ModelSim6.5SE软件对方案进行行为级仿真,设定相位偏移值θ△为45°,仿真时序图如图5所示。图中上方波形为相位偏移之前的信号,下方波形为相位偏移之后的信号,两者相位差为45°,与设定一致。

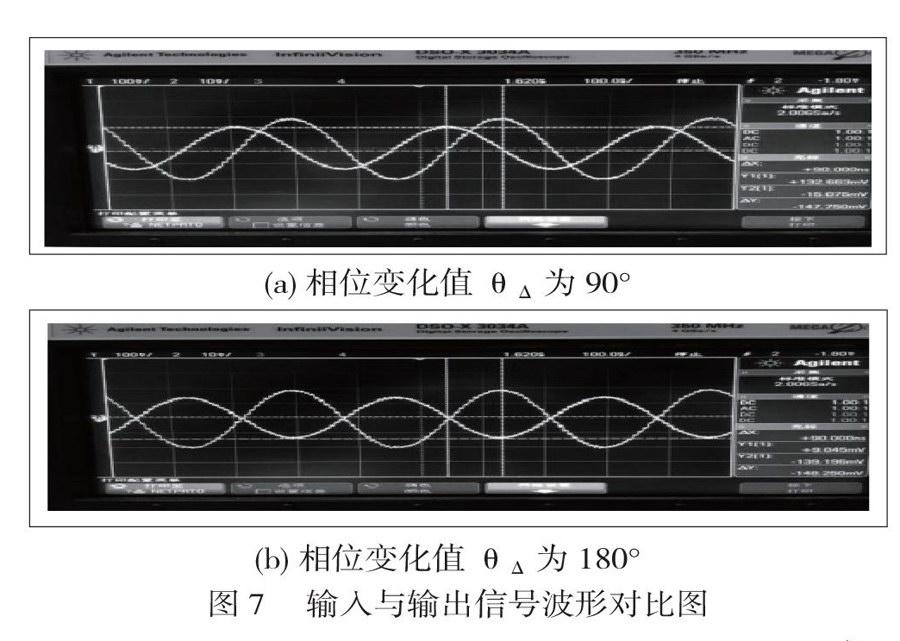

把生成的方案下载至开发平台,使用chipscope软件(在线逻辑分析仪)对方案运行结果进行验证。chipscope能够抓取FPGA芯片内部的数字信号,被广泛用于程序调试。图6为相位控制模块的基带实时波形图,图中两个信号的相位差分别30°、90°和135°。基带数字信号通过数模转换和上变频之后从开发平台射频输出口输出。将输入和输出信号同时接入示波器,可以对信号波形进行对比观察,如图7所示。图(a)设定相位偏移值θ△为90°,图(b)设定相位偏移值θ△为180°,显示结果与设定一致。

四、结束语

基于存储的相位控制方法有着结构简单、易于实现的优点,但其提高精度所带来的硬件资源消耗很大。基于正交运算的相位控制方法则能够以很小的硬件资源消耗达到很高的精度。以实现相同的相位控制精度为例,基于存储的相位控制方法要比基于正交运算的相位控制方法多消耗将近50%的存储资源和80%的运算资源。