一种新型无人机机载计算机同步策略研究

2016-11-17田心宇肖佳伟

田心宇,姚 英,肖佳伟

(1.西北工业大学 365所,西安 710065;2.西安邮电学院 电信系,西安 710121 )

一种新型无人机机载计算机同步策略研究

田心宇1,姚 英2,肖佳伟1

(1.西北工业大学 365所,西安 710065;2.西安邮电学院 电信系,西安 710121 )

机载计算机是无人机的核心部件,其可靠性高低直接决定了系统的安全;余度技术作为机载计算机可靠性设计的一项重要手段,对提高系统的应变能力,实现故障隐蔽以消除故障,改善系统性能有十分重要的作用;但是在余度技术中不同通道之间会存在一定的时钟误差,如果不进行处理将会使其无法达到无缝切换,从而影响系统的安全;在对机载计算机内部通道间不同步的原因进行详细分析的基础上,提出了一种软、硬件相结合的同步算法,并以三余度机载计算机为例进行了实际测试;测试结果证明该策略实现简单、同步效果好,异步度完全满足系统要求且付出的软、硬件代价小,显著提高了全系统的可靠性及可维护性。

余度;机载计算机;同步;可靠性;可维护性

0 引言

机载计算机是无人机航空电子系统的核心部件,是无人机控制与管理的中心。它完成无人机的稳定及控制,统一管理和调度机载电子设备,实现飞行控制与管理、定位与导航、任务规划与管理、飞行状态采集与处理、任务设备控制与管理等功能,机载计算机的可靠性的高低已成为飞机性能和作战效能的关键因素。在某种程度上,高可靠性的机载计算机系统己成为现代飞机的标志[1]。

提高机载计算机可靠性最常用的方法是余度技术,即机载计算机采用多套完全相同的软、硬件系统构成,多套系统同时工作,当出现故障时系统之间进行切换[1-3]。这种方式实质是利用多余的资源来换取整个系统可靠性的提高。但采用余度技术的同时带来了机载计算机内部多套系统之间的时间同步问题。针对上述情况,机载计算机内部各系统间的时间同步问题成为机载计算机系统重构的“焦点”。

本文以三余度机载计算机为例设计了一套结构简单、实现方便且异步度小于50 μs的通道间时间同步算法。

1 机载计算机同步策略设计

1.1 三余度机载计算机同步策略分析

三余度机载计算机是由3个通道构成,3个通道的软、硬件完全相同,一个通道在线运行,另两个通道处于“监控”状态,通道间同步运行。外部输入数据一起送入3个通道,在线运行的通道进行输出,通道间对各自的输入、输出结果进行交叉表决。如结果正常则系统正常输出;若有一个通道失效,则定位故障并成功切除,此时系统降级为双机热备份系统继续运行,若又有一个通道失效并被定位切除则系统运行在单机模式。同双余度计算机系统相比,它为输出结果表决提供了第3个计算值,对系统的故障判别提供了新的判据,具体的就是,在某两个通道之间计算结果不一致,同时各通道的监控均未发现本通道的故障时,将由第3个通道的计算结果决定哪一通道正确,即采用少数服从多数的原则[4-5]。

同构型三余度机载计算机体系结构如图2所示,机载计算机3个通道完全相同,每个通道由中央处理器(CPU)、模拟量处理模块(AIO)、串口收发模块(SIO)、数字量输入输出接口(DIO)、电源模块(PS) 以及其他功能模块构成。正常工作时通道A、通道B及通道C运行同一套软件,同时接收外部输入数据,将通道A的输出数据进行输出,通道B和通道C处于“监控”状态,当其中一个通道故障时,系统自动降为双余度系统。

图2 三余度机载计算机系统架构框图

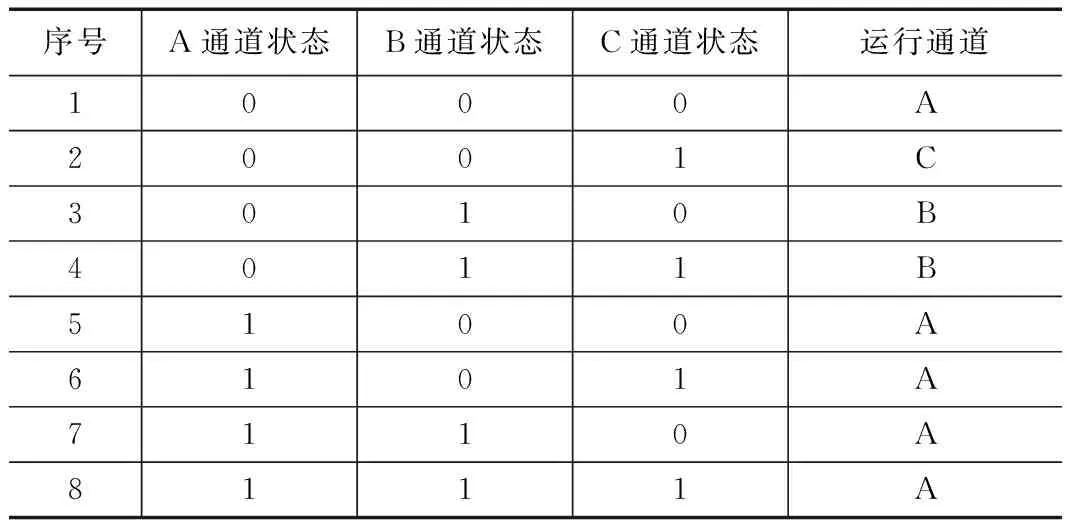

三余度机载计算机监控表决运行时要选取三通道中最健康的一个通道成为控制通道,这一选取过程就依赖于表决算法。 三余度机载计算机通道间表决逻辑状态表如表1所示。

如表1所示,A、B、C三通道的状态由自检测结果给出,通道健康为“1”,故障为“0”。表1给出了三通道各自的运行模态。三通道的优先级是:1、通道A,2、通道B,3、通道C。

表1 三余度机载计算机通道间表决逻辑状态表

三余度机载计算机通道间误差的产生原因主要有:

1) 通道间操作系统启动耗时差异;

2) 通道间处理器基准时钟的累积误差。

由于机载计算机通常使用嵌入式系统,处理器之间的差异造成使用同种操作系统的不同处理器之间的启动时间会有差异,其差异大小各有不同。

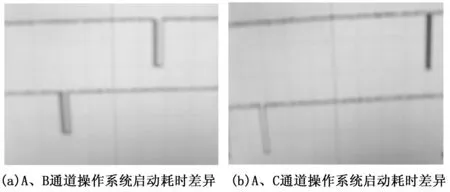

机载计算机上电后送出窄幅脉冲,采用示波器观测三通道之间的启动差异示波器采集步长为0.5 s,三余度机载计算机通道间操作系统启动耗时差异如图3、4所示。

如图3所示,A通道比B通道启动时间滞后约2 s,A通道比C通道启动时间滞后约3.5 s,这种差异导致三通道执行任务的时间无法统一。

图3 3通道操作系统启动耗时差异图

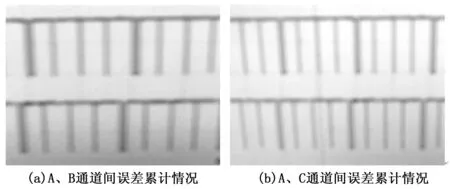

采用如下方法观察通道间的误差累计。机载计算机上电后并对3个通道进行开机同步后,三通道任务以10 ms为周期,周期性送出窄幅低电平脉冲。三通道间误差累计情况如图4所示。

图4 三通道间误差累计情况

观测到时钟误差不断累积,约20 min后三通道中,A通道比B通道滞后约8 ms, A通道比B通道滞后约5 ms,这种误差在飞行过程中是致命的,它会对全系统的飞行安全产生严重的威胁,因此通道间除了开机同步外, 还需要进行周期性同步。

为实现三台机载计算机间的同步,采用以软件为主,软/硬结合的双握手同步算法实现通道同步。实现同步算法,要求硬件上要有专用的同步信号传输总线,因此我们使用机载计算机的数字I/O接口来实现这个功能。为使通道同步工作软件上提出一套握手协议来实现同步。

如图5所示,每台机载计算机内有一个数字量输出口DO,用以输出同步握手信号给另一通道;并有两个数字量输入口DI,用于接收另两两台机载计算机的同步输入信号。

同步握手算法:机载计算机进入同步后,首先关中断,接着输出一个“逻辑高”同步DO信号,然后在限定时段内查询另两通道响应的“逻辑高”DI信号;在握手成功后,打开中断,三通道均将DO信号输出逻辑低。同步算法的周期与定时任务周期一致为10 ms,即每10 ms都要进行一次同步。

图5 三余度同步硬件设计示意图

1.2 三余度机载计算机同步算法设计

针对三台机载计算机间操作系统启动过程中的启动耗时差异,提出开机同步概念。软件流程如图6所示。

图6 开机同步软件流程图

开机同步实现算法: 系统加电后,处理器通过DO引脚向另一个处理器发出同步信号,同时采集另一台机载计算机所发出的同步信号,当机载计算机在发出同步信号并采集到另一个机载计算机的同步信号后,开机同步成功,并转入实时任务周期。若机载计算机发出同步信号后未采集到另一个机载计算机的同步信号,则等待;同时继续采集另一机载计算机的同步信号,如等待5 s后还没有采集到另一机载计算机的同步信号,则认为另一机载计算机故障,且置为永久故障,并将该机载计算机隔离,进入双机工作模式。

开机同步软件运行在系统加电后初始化过程中。将开机同步软件封装为一个函数:void Star Synchronization (void), 该函数只在开机后调用一次,以消除三台机载计算机启动耗时误差。

针对通道间处理器基准时钟的累积误差,提出了10 ms周期性同步概念。软件流程图如图7所示。

图7 10 ms周期性同步软件流程图

开机同步完成后,系统转入到10 ms任务周期,在执行10 ms周期性任务之前需进行10 ms周期同步,10 ms周期性同步实现算法: 函数首先禁止所有中断, 判断另一个通道是否可用,若不可用则进入单机工作模式,若可用,进入同步。通过DO向另一个处理器发出同步信号,同时采集另一个处理器发出的同步信号,若采集到同步信号后使能中断,进入10 ms定时任务。若未采集到同步信号则等待并继续采集,若50 μs内还没有采集到同步信号,使能中断,并将失步次数加1,如果连续10 次不能同步,则进入同步恢复阶段。将10 ms任务周期同步软件封装为一个函数: void Cycle Synchronization (void), 该函数在10 ms任务执行前执行,以消除两台机载计算机处理器晶振的累积误差。

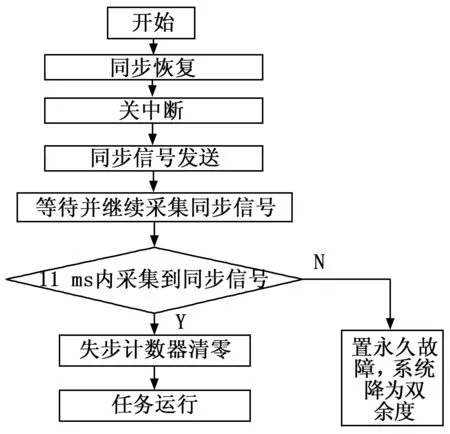

如10 ms同步任务执行失败则进入同步回复阶段,同步恢复算法软件流程图如图8所示。

图8 同步恢复算法软件流程图

同步恢复算法:如果如果连续10 次未能同步,则未同步上的通道屏蔽所有中断,采集同步信号,如果11 ms内都未能采集到同步信号,则认为同步恢复失败,该通道记为永久故障,系统进入双余度工作模式。由于此部分软件与10 ms同步任务密切相关,所以将其封装进10 ms任务周期同步软件中。

2 实例测试与分析

我们使用一台基于本文介绍的余度算法设计的三余度机载计算机进行测试。

三套系统以10 ms为周期,周期性送出窄幅低电平脉冲。机载计算机开机运行20分钟后,系统间误差累计情况如图9所示。

如图9所示,经过机载计算机开机及10 ms周期性同步执行后三余度机载计算机内的开机误差及累计误差消失,机载计算机间完成了同步,证明本算法切实可行,且解决了三余度机载计算机系统同步问题。

3 结论

本文设计的三余度机载计算机同步策略经实践验证表明,机载计算机通道间时间同步算法同步效果好,异步度完全满足要求。提高系统的可靠性及可维护性,而为此付出的软硬件代价较小。

[1] 张小林. 小型飞行器机载计算机的余度设计技术西北上业大学学报,2001, 19(2) : 274- 278.

[2] Chen P, Xu H C.Aviation electron system BIT summary [J]. China Water Transport(Academic Version), 2002,6(2):108-110.

[3] ATCS Jeffrey J. Application of trend analysis methodologies on built-in-test (BIT) (and non-BIT)systems in a operational U.S. navy fighter/attack squadron[A]. 2005 IMTC-Instrumentation and Measurement Technology Conference[C]. Ottawa, Canada, 2005.

[4] 曾天翔.电子设备测试性及诊断技术[M]北京:航空工业出版社,1996.

[5] 温熙森, 徐永成, 易晓山, 等. 智能机内测试理论及应用[M]. 北京:国防工业出版社,2001.

Research on a New Type Synchronization Design Technology of UAV Airborne Computer

Tian Xinyu1, Yao Ying2,Xiao Jiawei1

(1.No 365 Institute, Northwestern Polytechnical University, Xi′an 710065, China;2.Department of Electronic and Information Engineering, Xi′an University of Post and Telecommunications, Xi′an 710121, China)

The airborne computer is the core component of the UAV, the reliability of the airborne computer influences the survival ability of the whole system. Redundant technology is an important method in airborne computer reliability design. It can improve the adaptability of system, realize avoiding malfunction by error concealment, improve system performance. But there are clock error between different channels, the seamless switching can’t be realized and the system safety will be affected with it. Based on the analysis of non-synchronization between each channels in airborne computer, a synchronization method of software and hardware is put forward. A detailed algorithm design of the tri-redundancy structure in airborne computer is given. The method and strategy is effective to system synchronize, the system asynchronization is satisfied the requirement through actual test with low cost of software and hardware. The reliability and maintainability of system have been improved.

redundency; airborne; synchronization;reliability; maintainability

2015-12-03;

2016-01-06。

国家自然科学基金(60134010)。

田心宇(1977-),男,陕西汉中人,高级工程师,博士,主要从事无人机系统及机载计算机方向的研究。

1671-4598(2016)06-0185-04

10.16526/j.cnki.11-4762/tp.2016.06.051

TH873.7

A