一种高可靠宇航控制器设计及可靠性评估

2016-11-17程利甫

王 豪,程利甫,刘 博,刘 攀

(上海航天电子技术研究所,上海 201109)

一种高可靠宇航控制器设计及可靠性评估

王 豪,程利甫,刘 博,刘 攀

(上海航天电子技术研究所,上海 201109)

将8051、存储器等IP核集成在FPGA内部, 可实现宇航控制器高可靠、小型化的应用需求。但FPGA在空间环境中容易发生单粒子翻转事件(SEU),影响系统正常功能,常采用在FPGA内部进行三模冗余(TMR)设计;针对三模冗余系统无法纠正存储区中发生的SEU故障,提出了一种采用三模冗余架构并对FPGA配置区域进行刷新重载的解决方案,同时采用马尔可夫模型对该设计方案进行了可靠性评估和仿真;结果表明,采用该设计架构的宇航控制器具有较高的可靠性与安全性,可实现飞行器的长期稳定运行。

8051核;宇航FPGA;单粒子翻转;三模冗余;回读刷新;可靠性

0 引言

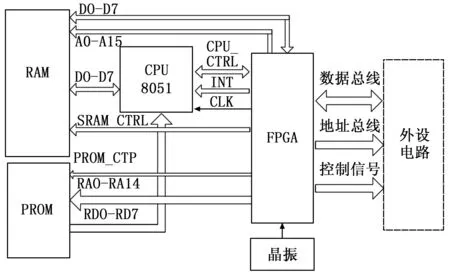

长期以来,8051单片机以其性价比高、体积小、功能灵活等方面的独特优点被广泛应用于宇航产品中。但受其内部资源的限制,8051单片机需要在片外扩展众多硬件资源以满足不同应用的需求[1],其功能如图1所示。

图1 典型8051宇航控制器功能框图

随着EDA(Electronic Design Automation,电子设计自动化)技术的发展,可重构的嵌入式CPU核—DW8051核、功能复杂的IP(Intellectual Property,知识产权)核及各种功能强大的EDA工具的出现,使得将CPU(Central Processing Unit,中央处理器)、存储器和一些外围电路集成到一个芯片——FPGA(Field Programmable Gate Array,现场可编程门阵列)中成为可能[2-3]。图2所示为集成后的原理框图,集成后的系统较之前体积大幅减小。

图2 FPGA内部嵌入IP核的控制器设计

采用FPGA进行系统集成可大幅缩减系统体积,但FPGA特别是可重构型静态存储器(static random access memory,SRAM)型FPGA应用于空间环境中存在抗空间辐射能力差,容易发生SEU(Single Event Upset,单粒子翻转)[4-5]故障,对卫星功能造成了不同程度的故障,因此必须采取一定的抗辐加固措施以提高其可靠性。

下文提出一种内嵌8051IP核并采取抗辐加固措施的宇航控制器设计方案并对其可靠性进行评估。

1 采用8051IP核的高可靠控制器设计

SRAM型FPGA内部的配置区——配置存储器,功能区——块存储器、触发器等都是单粒子反转的敏感区。当一个高能带电粒子穿过灵敏区时,将会使FPGA器件内部导通管截止、截止管导通,引起器件逻辑状态的翻转——即单粒子翻转[6]。

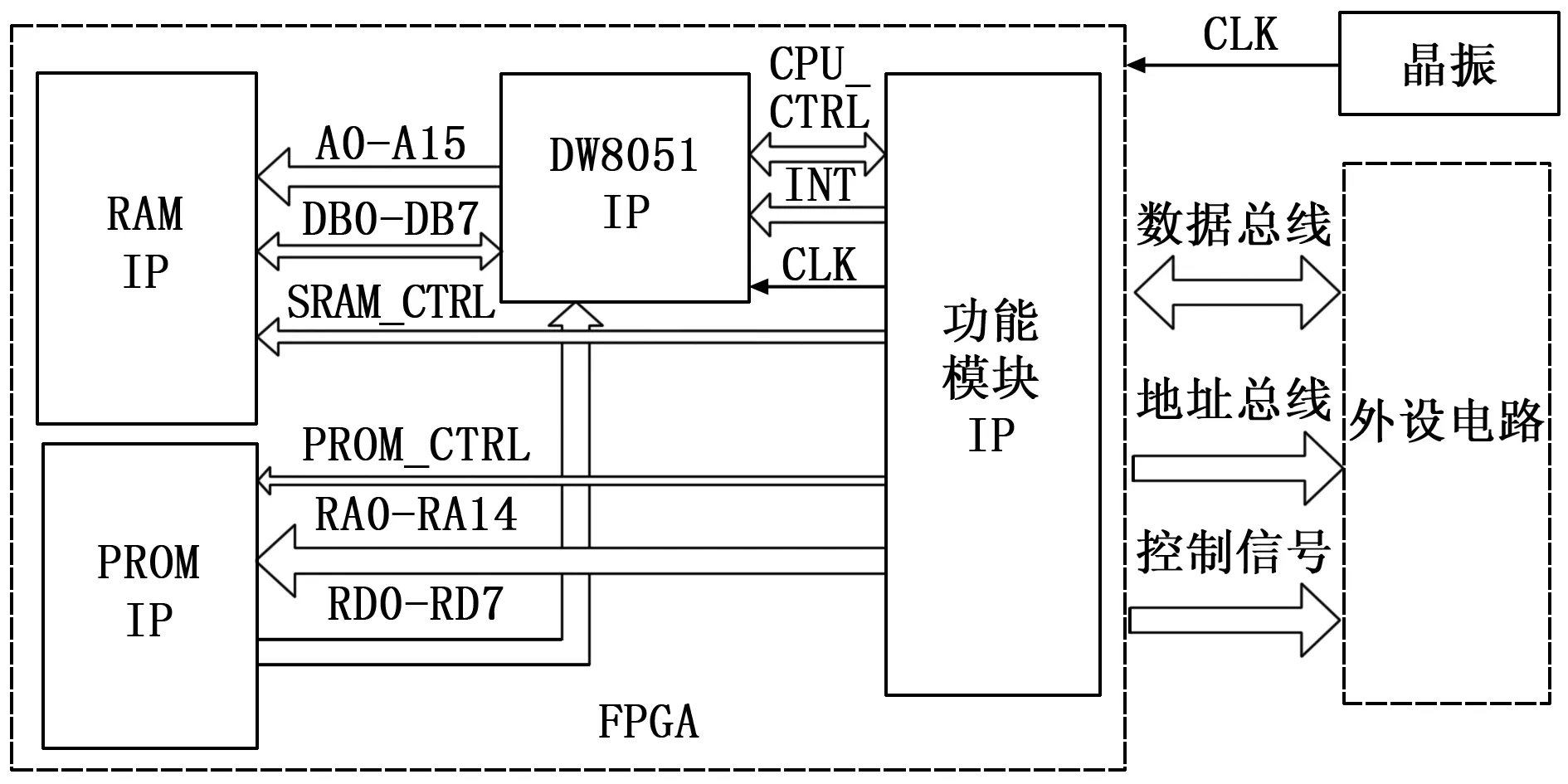

设计中常采用三模冗余(triple module redundancy,TMR)[7]技术对要在FPGA内实现的硬件设计进行保护。

图3 三模冗余系统原理框图

图3所示为采用三模冗余架构的FPGA系统原理框图,可以看出这种方法通过嵌入冗余处理机制到用户应用来屏蔽故障,从而获得正确的输出,本质上是一种利用硬件冗余或信息冗余进行故障屏蔽的容错方法。

然而,冗余容错方法无法改变FPGA的配置内容,对于发生在配置存储器中的SEU并无纠正能力[8],若SEU积累最终将使得TMR失效,导致故障发作。

针对三模冗余(TMR)系统无法纠正存储区中发生的SEU故障,本文提出一种三模冗余加回读刷新的解决方案,应对空间FPGA单粒子翻转。

图4 采用三模冗余与回读刷新架构FPGA功能框图

由于SRAM型FPGA配置信息存储于SRAM单元中,可对存储单元进行回读刷新操作纠正发生翻转的存储单元。回读刷新是通过回读刷新器件来实现的,有两种工作模式:回读和刷新。回读模式[9]下该器件读取FPGA内配置存储区的数据,并与存储在PROM中的原始配置数据进行比较,当发现数据不一致的情况时,就意味着配置存储器单元发生了SEU,进而将PROM中存储的原始配置文件重新写入FPGA。刷新模式[10]下不管FPGA有没有发生SEU均周期对配置存储区进行刷新。采用回读刷新加三模冗余架构的FPGA系统原理如图4所示。其中,PROM芯片内部存储FPGA的配置信息,该器件采用反熔丝工艺不会受空间SEU干扰;回读刷新器件亦采用反熔丝工艺对空间SEU免疫;FPGA内部电路采用TMR设计。

2 可靠性分析

系统可靠性是指系统在规定条件下和规定时间内完成规定功能的能力。由于系统是冗余系统,系统发生故障是余度性能降级的动态过程,利用马尔可夫过程理论能够对余度系统进行精确的可靠性建模分析,较为真实地描述系统的实际工作过程[11-12]。为方便讨论及建模,将图4所示的回读刷新加TMR的FPGA系统可简化为如图5所示的逻辑框图;回读刷新器件作为SEU故障修复模块,周期地对FPGA内部配置存储区进行刷新。

图5 简化后三冗余及回读刷新FPGA系统框图

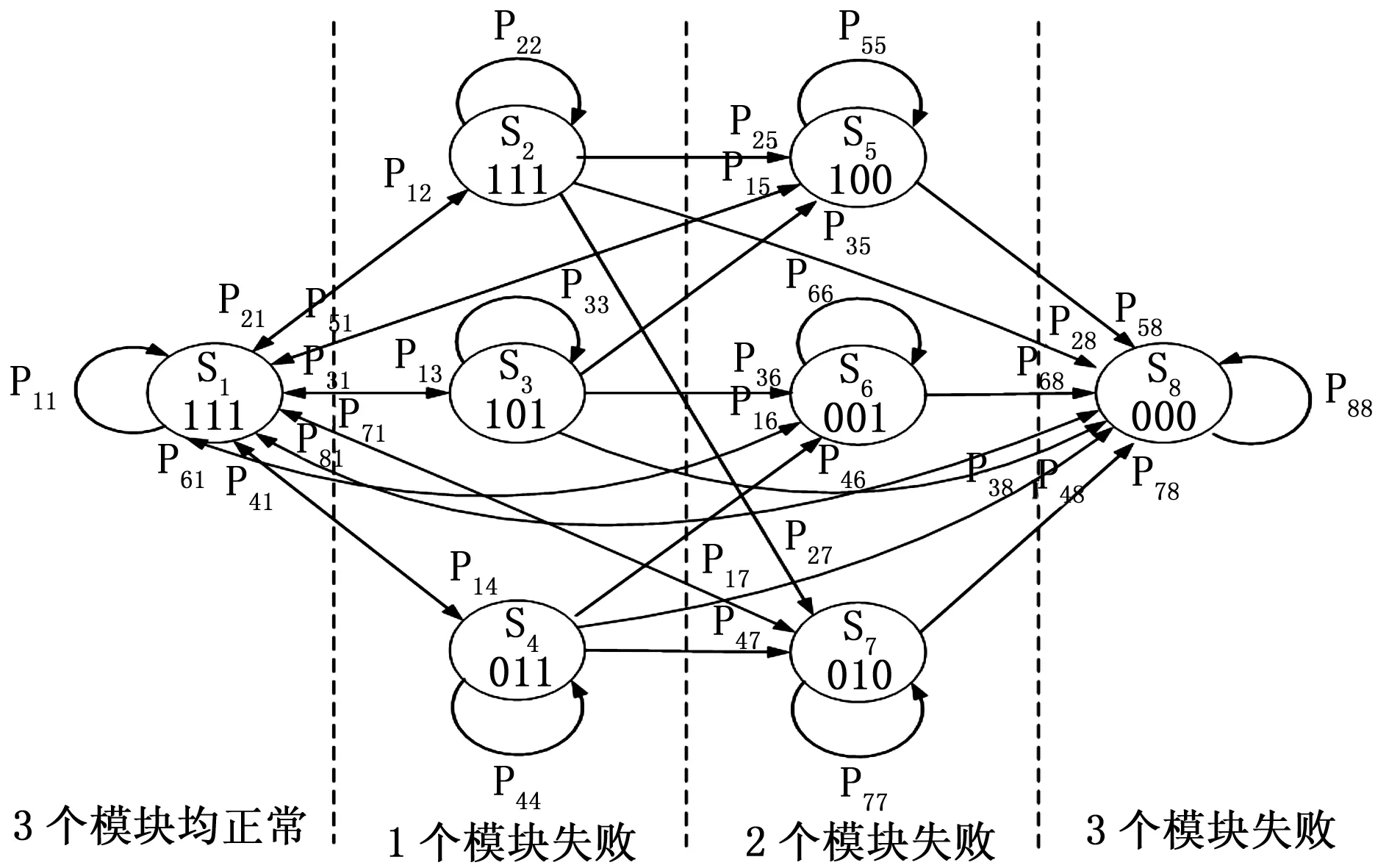

采用TMR的系统具有23=8种状态,当一个模块发生故障时,不会影响系统的正常工作,而当失效模块数≥2时,系统失效。这个状态可以视为马尔可夫吸收态。假设每个模块的失效率都相同均为λ,修复率为μ。

则根据可靠性分析理论[13],若某模块在时刻t正常工作,则在t+Δt时刻发生常规故障的概率为p=1-e-λΔt,当Δt→0该故障概率可简化为λΔt。

基于以上假设,在周期对FPGA配置区进行定时刷新且考虑共模故障影响下的三模冗余系统的马尔可夫模型状态转移如图4所示,其马尔可夫状态可描述如下:

1)状态S1—“111”表示A、B、C3个模块均未受到SEU影响、功能均正常;

2)状态S2—“110”表示某时刻C模块受到SEU影响,功能异常且翻转单元暂未得到刷新纠错。A、B模块正常,经三取二表决后系统仍能正常工作。

3)状态S3—“101”表示某时刻B模块受到SEU影响,功能异常且翻转单元暂未得到刷新纠错。A、C模块正常,经三取二表决后系统仍能正常工作。

4)状态S4—“011”表示某时刻A模块受到SEU影响,功能异常且翻转单元暂未得到刷新纠错。B、C模块正常,经三取二表决后系统仍能正常工作。

5)状态S5—“100”表示某时刻B、C模块受到SEU影响,功能异常而且翻转单元暂未得到刷新纠错,经三取二表决后系统功能失效。

6)状态S6—“001”表示某时刻A、B模块受到SEU影响,功能异常而且翻转单元暂未得

到刷新纠错,经三取二表决后系统功能失效。

7)状态S7—“010”表示某时刻A、C模块受到SEU影响,功能异常而且翻转单元暂未得到刷新纠错,经三取二表决后系统功能失效。

8)状态S8—“000”表示某时刻A、B、C模块均受到SEU影响,功能异常且翻转单元暂未得到刷新纠错,系统功能失效。

记Pi(t)=P(X(t)=i),表示t时刻系统处于状态i的概率,i∈{1,2,3...,8},令P(t)=[P1(t),P2(t),...,P8(t)],则P(t)满足状态方程:P′(t)=AP(t),其中,A为状态转移密度矩阵,有状态转移图可知:

图6 采用TMR和回读刷新的FPGA系统的马尔可夫状态转移图

(1)

并由此可得微分方程如下:

(2)

A和P(t)代入方程P′(t)=AP(t)中,并代入初始条件P(0)=[1,0,0,...,0],可得到t时刻各个状态的概率,从而求得该系统的可靠度R(t)和安全度S(t)[14]:

(3)

(4)

3 仿真结果分析

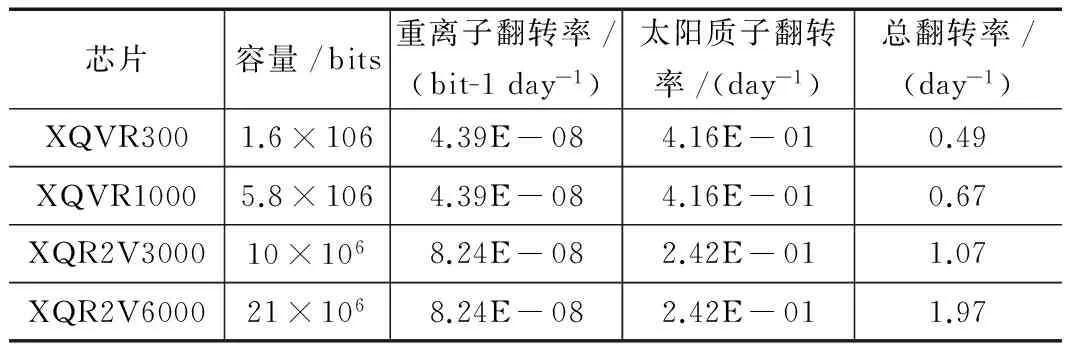

对于P(t)的状态方程P′(t)=AP(t),可以通过Laplace变换的方法求得其解析解,进而求得系统的可靠度和安全度,但其计算工作量相当庞大[15],为此,采用Matlab中的求解微分方程的Ode45指令进行仿真计算[8]。其中单粒子翻转故障率λ可参照表1所示Xilinx公司FPGA单粒子翻转率[16]。

表1 Xilinx公司FPGA单粒子翻转率

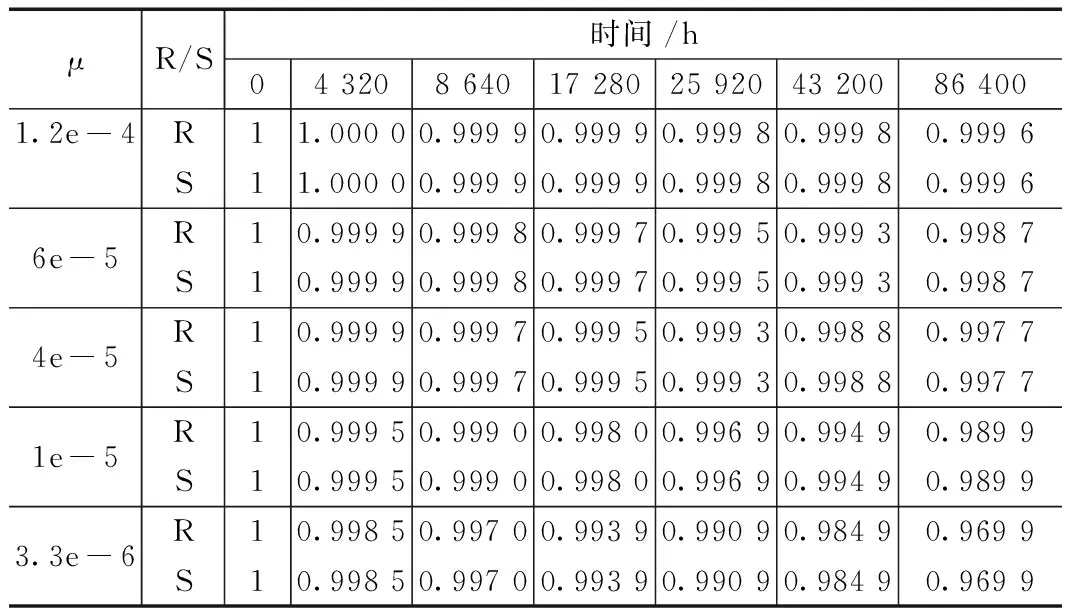

由表1可以看出随着FPGA容量的增加,单粒子翻转率也随之增加。系统修复率μ与回读刷新的频率有关,以5 s、10 s、15 s、1 min、3 min的刷新周期为例对采用Virtex2系列XQR2V3000型FPGA系统的可靠度、安全度进行分析。

表2 λ=1.07 day-1 时 参数μ对系统可靠性安全性影响

注:假设刷新周期为1 min、且存储容量为10×106时的修复率μ为1e-5。

从表2可以看出,随着参数μ的增加,三模冗余系统的可靠度和安全度均有所提高,初始时刻系统完好可靠度和安全度皆为1.000,随着运行时间的增加,系统可靠度和安全度均有所下降。图7所示的仿真波形为t=0-3.5×108s、λ=1.07 day-1时,三模冗余与回读刷新系统的可靠度和安全度随修复率μ的变化曲线。

图7 不同刷新周期系统可靠度r随时间t变化曲线

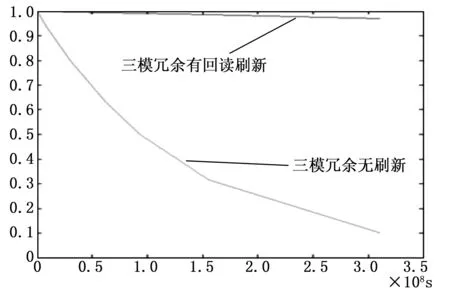

图8所示为t=0-3.5×108s、λ=1.07 day-1时,采用三模冗余有回读刷新设计的FPGA系统与三模冗余无刷新FPGA系统的可靠度比对。由图中可以看出,随时间的增加,两者的可靠度均有所下降,但采用三模冗余有回读刷新的FPGA系统可靠度明显优于无刷新系统。

图8 三模冗余有刷新系统与三模冗余无刷新系统的可靠度比对

4 结束语

为了提高宇航控制器的集成度、可靠性,本文提出一种在FPGA内部嵌入CPU(8051)、存储器等IP核的设计方案,但FPGA应用于空间环境中易受空间高能粒子干扰,产生单粒子翻转(SEU)风险,对飞行器功能造成影响。文章分析了常规三模冗余抗辐加固设计的不足后,提出了一种采用三模冗余架

构(TMR)并对FPGA配置区域进行刷新重载的解决方案,并对其可靠性进行了仿真分析,仿真数据证明该设计架构具有较高的可靠性,对小型化、高可靠宇航控制器设计具有较好的参考意义。

[1] 陈金恩,周赢武.基于FPGA与MC8051 IP核的可调窄脉冲激光泵浦源的研制[J].闽江学院学报,2011,32(5):23-27.

[2] 王 瑞,游志宇,杜 杨,等.MC8051单片机IP核的FPGA实现与应用[J].电子设计工程,2009,17(1):57-63.

[3] 丁 昊,庄贵敏,宋 杰,等.基于MC8051内核的便携幅频特性测试仪设计[J].嵌入式技术,2011,37(4):29-32.

[4] 邢克飞,杨 俊,王跃科,等.Xilinx SRAM型FPGA抗辐射设计技术研究[J].宇航学报,2007,28(1):123-129.

[5] 周秀娟,叶荣润.Virtex-II系列FPGA的回读与部分重配置[J]. 现代电子技术,2012,35(13):159-161.

[6] 邱金娟,徐宏杰,潘 雄,等. SRAM型FPGA单粒子翻转测试及加固技术研究[J]. 电光与控制,2011,18(8):84-85.

[7] 黄 伟,刘 涛,王 华,等.SRAM型FPGA的单粒子效应及TMR设计加固[J].航天返回与遥感,2012,33(2):49-53.

[8] 顾义坤,倪风雷,刘 宏.Xilinx FPGA自主配置管理容错设计研究[J].宇航学报,2012,33(10):1520-1521.

[9] 刘斐文,姚 睿.基于FPGA动态部分重构的D/TMR系统设计[J].计算机工程与应用.2010,46(35):55-57.

[10] Graham P,Caffrey M,Johnson D E,et al.SEU mitigation for half-latch in Xilinx Virtex FPGA[J].IEEE Transactions on Nuclear Science,2003,50(6):2139-2146.

[11] 邹见效,徐红兵,张正迁. 基于三重冗余的ETS控制系统设计及可靠性评估[J].电子科技大学学报,2010,39(5):793-799.

[12] 王丽华,徐志根,王长林.可维修三模冗余结构系统的可靠度与安全度分析[J].西南交通大学学报,2002,37(1):103-107.

[13] 曾声奎.系统可靠性设计分析教程[M].北京航空航天大学出版社,2004.

[14] 沈 洁,单 冬.三模冗余计算机联锁系统可靠性安全性分析[J].北方交通大学学报,1998,22(5):111-114.

[15] 靳红涛,焦宗夏,王少萍,等.高可靠三余度数字式作动器控制器设计与实现[J].北京航空航天大学学报,2006,32(5):548-552.

[16] Swift G M,et al.Dynamic testing of Xilinx Virtex-II field programmable gate array(FPGA)input/output blocks(IOBs)[J].IEEE Tran. on Nuclear Science,2004,51(6):3469-3474.

Design and Reliability Evaluation of Controller with High Reliability Used for Aerospace

Wang Hao, Cheng Lifu, Liu Bo, Liu Pan

(Shanghai Aerospace Electronic Technology Institute, Shanghai 201109,China)

In order to meet the high-dependability requirement of electronic equipment for aerospace, a new method which integrating 8051 IP core and storage IP core into FPGA is proposed. After analyzing the shortcoming of traditional Triple Module Redundancy (TMR) design aiming to migrate the SEU effect on FPGA, a fault tolerance method based on TMR and readback-scrubing the configuration-data of FPGA is used. Then the reliability of this architecture is achieved in detail by Matlab tool with Markov model. Simulation results show that this FPGA architecture has higher reliability, which can meet the requirement of Aerospace electronic controller.

8051 IP core; Aerospace FPGA;SEU; triple module redundancy; readback and scrub;reliability

2015-11-30;

2016-01-04。

王 豪(1989-),男,河南新安人,硕士,工程师,主要从事高可靠星载计算机方向的研究。

1671-4598(2016)06-0298-04

10.16526/j.cnki.11-4762/tp.2016.06.081

TP181

A