32位RlSC嵌入式微处理器流水线设计

2016-11-10王丽霞孙长秋

王丽霞,孙长秋

(1.青岛港湾职业技术学院,山东青岛,266404;2.青岛职业技术学院,山东青岛,266555)

32位RlSC嵌入式微处理器流水线设计

王丽霞1,孙长秋2

(1.青岛港湾职业技术学院,山东青岛,266404;2.青岛职业技术学院,山东青岛,266555)

介绍了一32位RISC嵌入式微处理器(取名为 MoonCore)的5级流水线的结构,即取指&译码(IF&ID)、读寄存器堆(RF)、执行(EXEC)、访存(DMEM)和写回(WB),详细介绍了各个流水级的主要部件的设计并分析了流水线相关问题及解决办法。

微处理器;精简指令集计算机;流水线

0 引言

由于嵌入式微处理器大多应用于便携式设备和通讯设备等用电池供电的设备中,因此要提高微处理器的速度和降低功耗设计对于嵌入式微处理器的设计尤为重要,而采用流水线技术是解决上面两个问题的很重要的方法。MoonCore是一32位RISC的嵌入式微处理器,本着节省资源,控制简单的原则,采用5级流水线结构,即取指&译码(IF&ID)、读寄存器堆(RF)、执行(EXEC),访存(DMEM),写回(WB)。数据通路就嵌入到这5级流水线之中。

1 MoonCore体系结构

MoonCore指令集共有49条指令,全部来自于MIPS I指令集,所有指令均为32位的定长指令,指令地址按字对齐。存贮器访问指令Load和Store指令都为立即数类型指令,用于在存储器和通用寄存器之间传递数据;计算类指令用于完成算术、逻辑、移位运算;跳转/转移控制指令用于改变程序的顺序执行次序;专用指令:用于执行一些特殊任务。

2 MoonCore流水线设计

图1 基本的地址形成逻辑图

MoonCore的5级流水线结构分别为取指&译码(IF&ID)、读寄存器堆(RF)、执行(EXEC),访存(DMEM),写回(WB)。

2.1IF&ID级设计

在这一级,程序计数器PC获得指令地址,从指令存储器取出指令,解码并产生各种控制信号。这一级主要部件有指令存储器,PC寄存器和解码器等。

PC寄存器的位宽为32位,因为每条指令的长度是4个字节。需要注意的是,PC寄存器和普通的寄存器不同,不能直接对其进行读写操作,在本设计中,各种控制信号均由有限状态机产生。

2.2RF级设计

RF级是MoonCore设计中结构最为复杂的一级。在这部分主要完成下面的几个操作:

(1)计算产生下一条指令的地址。

(2)取寄存器堆的操作数。

(3)对指令中的立即数进行扩展。

(4)产生目标寄存器地址。

RF级的主要部件有指令地址形成器PC_GEN,数据扩展器EXT,数据比较器CMP和目标寄存器地址形成器等。

2.2.1指令地址形成器PC_GEN的设计

在MoonCore结构中默认的下一条地址是PC+4,而转移指令将改变程序的顺序执行,因此必须在离IF近的流水级实现,因此将其放在RF级。因为编译器支持延迟转移,这要求必须是地址形成逻辑模块的输出接PC的输入,而PC寄存器的输出又直接接在地址生成器模块上。基本逻辑如图1所示。

2.2.2数据扩展器EXT的设计

MoonCore指令集的基本指令格式有三种:R-type、I-type和J-type。其中I、J类型都是在字的后16位带有立即数,其中J类型中的指令J(AL)后26位是立即数,以及R指令类型的移位指令SRLV、SLLV后5位是立即数。这些立即数要根据实际的指令扩展为32位的字。

2.2.3数据比较器CMP的设计

条件转移指令如BEQ,BLEZ等指令要根据寄存器的数据进行相关的比较,比较的结果给地址产生器PC_GEN以用来产生新的指令地址。因此需要有一个数据比较器CMP。CMP有两个32位数据输入,分别是RS_IN 和RT_IN和一条由解码器产生的经过指令流水线传输的控制信号CMP_CTL,输出端输出1位信号,指示转跳条件是否成立。

通常,比较器是放在和ALU同一级的流水段中,在本设计中如果也采用这种方式就会造成转移指令延迟多个时钟周期的浪费。结合存储部件的特征,加在RF段。

2.2.4目标寄存器地址形成器的设计

在R-type指令中,运算结果最终写回到RD(指令中的20-16位为目标寄存器索引)寄存器,而在I-type指令中运算结果写回到RT中(指令中的25-21位为目标寄存器索引),比较特别的是在JAL指令中把PC的数值通过ALU传递给R31号寄存器。因此这个选择器的输入需要RNS和RNT,以及一个控制信号。目的寄存器地址选择器的结构如如图2所示。

图2 目的寄存器地址选择器

由于0号寄存器件总是输出为常数0,因此可以将0号寄存器改为默认的寄存器地址。目的寄存器地址选择器件的模块实现代码如下:

2.3EXEC级设计

EXEC执行级主要完成以下的任务:

(1)使用ALU完成各种算术逻辑运算。

(2)把运算结果保存到寄存器中,供DMEM执行阶段使用。

主要部件有ALU和两个多路选择器。算术逻辑运算器ALU是微处理器的核心部件,所有的算术运算,如有符号数,无符号数的加减乘除,逻辑运算的与或以及移位运算都在这里完成。本设计中ALU分为三个并行的部分:

(1)基本算术逻辑运算部分;

(2)算术逻辑移位部分;

(3)乘除法部分。

这三部分的连接如图3所示。

图3 ALU的三部分

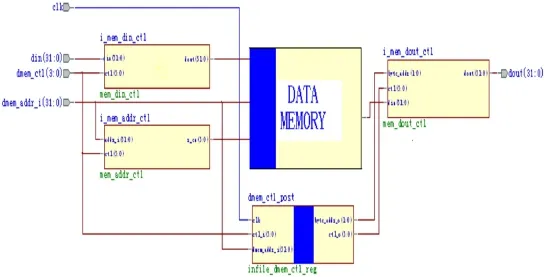

图4 存储控制器与存储器件连接

2.4DMEM级设计

DMEM数据存储器访问级专为Load/Store指令而设,要存储的数据来自寄存器堆,访问存储器的地址由ALU计算得出。Load指令读存储器,并把读出的数据写入流水线寄存器。Store指令把来自寄存器堆的数据写入存储器。DMEM级主要完成的任务有:

(1)给出各种存取存储器的控制信号,并完成存储器的存取任务。

(2)把从存储器中读入的数据保存到寄存器中,供WB写回阶段使用。

数据存储控制器包含三部分:数据输入控制和地址输入控制以及数据输出控制。

存储控制器与存储器件连接如图4所示。

由图可以清晰地看出数据和控制的前后逻辑,蓝色部分表示有寄存器的延迟,指令控制信号和地址信号要延迟一个周期后加在输出控制上,设计中通过加入一级D锁存器实现。

2.5WB级设计

在WB写回级主要完成的任务:

(1)指令执行结果写回到寄存器堆中。

(2)将乘法运算和除法运算的执行结果写入到寄存器HI和寄存器LO中。

这一级的主要部件就是一个写回的多路选择器,WB级把指令执行的结果写回到寄存器堆。

3 流水线相关问题及解决办法

相关是指指令流中的一条指令在指定的时钟周期内停止执行。相关的发生将会引起流水线的断流或延迟,降低微处理器的性能。存在下面三种相关:结构相关(Structural Hazards)、控制相关(Control Hazards)和数据相关(Data Hazards)。

采用指令存储器和数据存储器分离的结构,避免了结构相关的产生;采用数据旁路的技术解决了数据相关;采用延迟槽技术,由编译器负责向延迟槽填入指令,解决了控制相关。

4 小结

嵌入式微处理器多采用流水线技术。 MoonCore微处理器采用5级流水线的结构,取指&译码(IF&ID)、读寄存器堆(RF)、执行(EXEC)、访存(DMEM)和写回(WB),提高微处理器的速度和降低功耗。

[1] Dominic Sweetman.See MIPS Run(Second Edition). San Francisco,ca,USA:Morgan Kaufmann Publishers Inc.,2006

[2]M I P S 3 2 A r c h i t e c t u r e f o r P r o g r a m m e r s VolumeⅠ:Introduction to the MIPS32 Architecture

[3]易建勋.微处理器(CPU)的结构与性能.北京:清华大学出版社,2003

[4] 张奕.32位5级流水线嵌入式处理器设计:[硕士学位论文].成都:电子科技大学, 2007

[5]吕睿.HOPE-MIPS流水线功能段的设计:[硕士学位论文].西安:西安电子科技大学,2007

[6]朱子玉,利亚民.CPU芯片逻辑设计技术.北京:清华大学出版社,2005

Pipeline Design of 32-bit RISC Embedded Microprocessor

Wang Lixia1,Sun Changqiu2

(1.Qingdao Harbour Vocational&Technical College,Shandong Qingdao,266404;2.Qingdao Technical College,Shandong Qingdao,266555)

The Project introduced five-stage pipeline design of a 32 bit RISC mMicroProcessor (named MoonCore) which includes IF&ID(Instruction Fetch &Instructions Decode)、RF(Register Fetch)、EXEC(Execute),DMEM(Data MEMory access)and WB(Write Back) and introduced the design of main modules of microprocessor in detail, analyzed three kinds of hazards of pipeline and solutions.

Microprocessor;RISC;Pipeline