基于VHDL的FIR低通数字滤波器设计与仿真

2016-11-09王建彬李响何东钢

王建彬 李响 何东钢

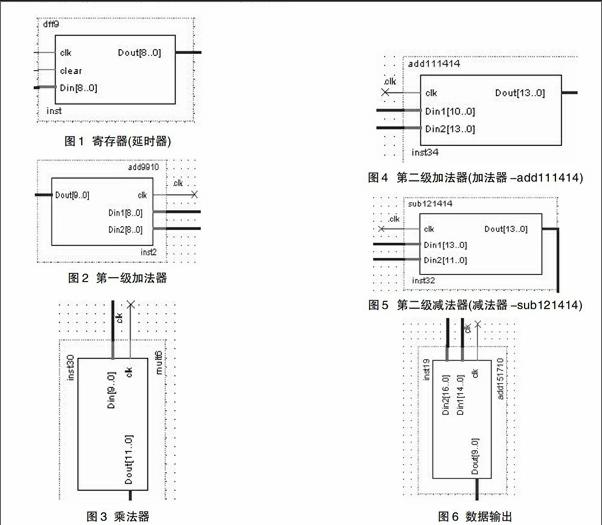

摘要:以FIR数字滤波器的基本理论为依据,程序设计部分设计滤波器电路中的寄存器(延时器)、第一级加法器、乘法器、第二级加减法器、输出等多个单元器件模块。采用模块化的自顶向下的设计思想,对各个功能模块采用VHDL语言的描述方法,VHDL程序设计代码在Quartus II 的集成开发环境下使用,并且利用其内部的仿真器对设计进行了仿真和验证。

关键词:FIR 数字滤波器 VHDL语言 Quartus

中图分类号:TN713.7 文献标识码:A 文章编号:1007-9416(2016)09-0195-02

信号处理广泛应用在通信、控制等领域,对电子、信息科学等的发展有巨大的影响。信号处理分为模拟信号和数字信号处理系统。数字信号处理中一个非常重要的应用技术就是数字滤波[1]。数字滤波器是根据实验设计好的程序,将一组数字序列输入通过运算后,转变为另一组数字序列的输出,信号形式和内容的改变,达到符合技术指标的信号加工或滤波要求。由于VHDL语言是一种标准硬件描述语言,具有设计方式多样、强大的硬件描述能力、很强的移植能力、设计描述与器件无关等很多其他硬件描述语言所不具备的优点[2]。以FIR低通数字滤波器的设计为例,按照设计原理,在数字逻辑设计的过程和方法中使用VHDL硬件描述语言,编写相应代码在Quartus II的集成开发环境下运行,并利用其内部的仿真器对设计做脉冲响应仿真和验证。

1 FIR数字滤波器的设计原理

FIR数字滤波器是一个线性时的不变系统,长度为M阶因果有限冲激响应滤波器可以用传输函数H(W)描述:

H(W)=

有限冲激响应滤波器在时域中的输入输出关系:

y[n]=x[n]*h[W]=

其中x[n]和y[n]分别是输入和输出序列[3]。

2 FIR数字滤波器的设计原理

设计一个线性相应的FIR 16阶初始h(0)=0的低通数字滤波器,采样频率为100 khz,截至频率为10khz,序列位宽为输入输出10位。整个设计分为程序设计和原理设计两部分。其中程序设计部分设计滤波器电路中的寄存器(延时器)、第一级加法器、乘法器、第二级加减法器、输出等单元器件模块[4]。

2.1 寄存器(延时器)

如图1所示,设计中用输入9位数据,通过dff9的触发寄存器实现寄存一组9位的二进制数据,VHDL语言实现寄存功能。

设计中用D触发器组成寄存器,实现寄存功能。这里用来寄存一组9位的二进制数据。

2.2 第一级加法器

如图2所示,9位数字输入和10位数字输出数据通过add9910构成加法器,实现两个二进制数字的相加运算。

2.3 乘法器

如图3所示,乘法器用来将数据乘以由Matlab计算得到的滤波系数,总共有8个乘法器。在乘法器设计时暂时没有考虑符号,符号问题由下面的减法器实现。

2.4 第二级加减法器

对于乘了滤波系数的数据,进行第二次的加,如图4所示。由于上面有的滤波系数是负的,所以这里用减法器对上一面的负系数做减法运算,如图5所示。

2.5 输出

如图6所示,输出通过一个加法器add151710完成10位数据的输出,通过一个15位与一个17位数据相加得到的数据取高10为作为最终结果。

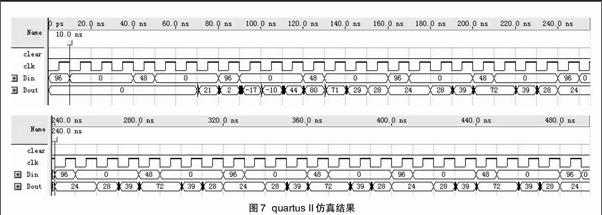

3 仿真结果

用VHDL语言实现的单元器件在仿真实验中构成元器件,按照原理图连接的滤波器件电路在Quartus II 的集成开发环境下完成[5]。

4 仿真结果验证

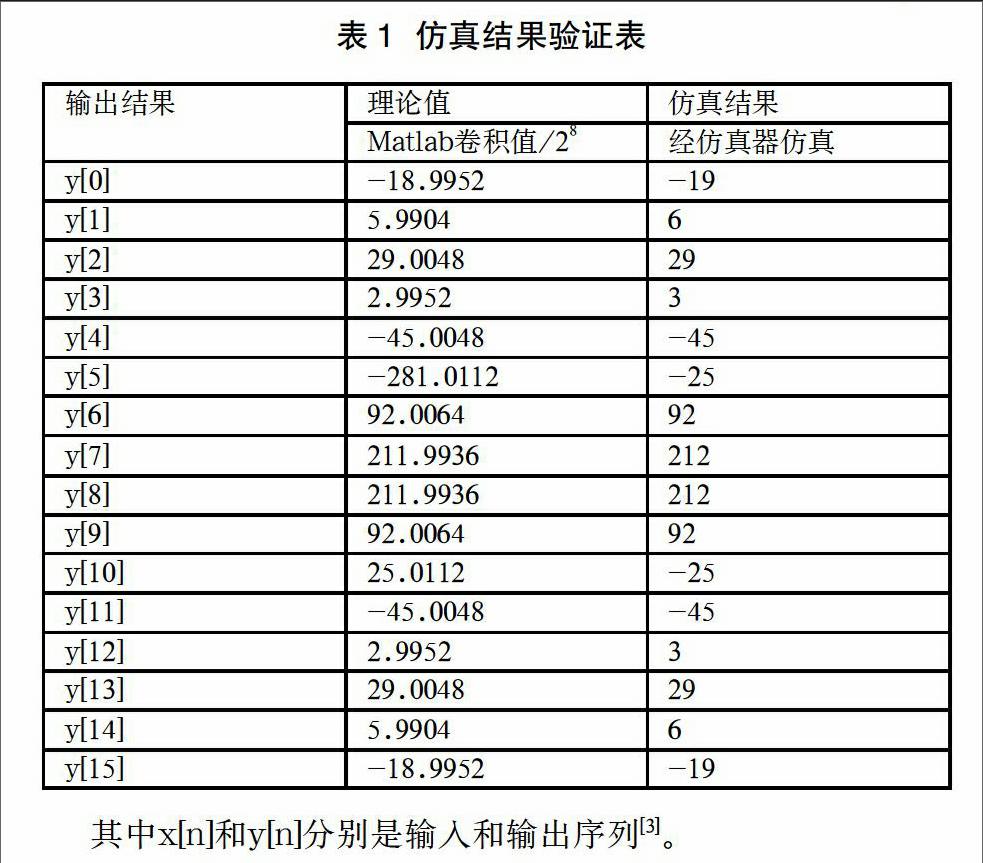

由FIR数字滤波器的公式[6]:

y(m)==

利用Matlab计算出FIR数字滤波器的卷积y[m]的理论值和仿真器仿真得到输出结果y[m]对比,见表1所示。

FIR数字滤波器的卷积y[m]的理论值和仿真器仿真得到输出结果y[m]比较,结果完全吻合。数字滤波器设计符合设计要求。

5 结语

基于VHDL的FIR低通数字滤波器的性能优劣对信号处理的结果有重要的影响。本文对FIR数字低通滤波器进行了研究,利用VHDL对FIR数字滤波器划分的多个模块进行模块的设计,并完成系统设计。按照设计原理,在数字逻辑设计的过程和方法中使用VHDL硬件描述语言,编写相应代码在Quartus II的集成开发环境下运行,并利用其内部的仿真器对设计做脉冲响应仿真和验证。

参考文献

[1]胡广书.数字信号处理理论算法与实现[M].清华大学出版社,2003.

[2]佩德罗尼.VHDL数字电路设计教程[M].电子工业出版社,2005.

[3]程佩青.数字信号处理教程[M].清华大学出版社,2007.

[4]张学敏.基于MATLAB的FIR带通滤波器的设计与仿真[J].长春工程学院学报(自然科学版),2007(08).

[5]蔡楠.基于VHDL语言的fir滤波器软件设计[J].科技信息,2010(34).

[6]罗时书.基于VHDL语言的16阶FIR滤波器设计[J].电脑知识与技术,2010(36).