基于ARM和FPGA的新型电能质量分析仪研究设计

2016-10-25周平殳国华陈敏捷丁君武

周平, 殳国华, 陈敏捷, 丁君武

(上海交通大学 电子信息与电气工程学院,上海 200240)

基于ARM和FPGA的新型电能质量分析仪研究设计

周平, 殳国华, 陈敏捷, 丁君武

(上海交通大学 电子信息与电气工程学院,上海200240)

电能质量分析仪是应用于电网电能质量监测和分析的重要工具,对提升电网供电质量有着重要意义。采用ARM/FPGA作为 主协处理器,通过硬件锁相环对频率进行同步跟踪,并且对电网信号同步采样,结合FFT变换以及基于FIR滤波器的Hilbert变换等,实现基本电力参数测量、谐波分析等功能。同时开发了基于ARM和WINCE6.0操作系统的人机界面软件,试验系统具备友好的人机交互、实时测量和显示功能。实验表明研制的分析仪功能全面、性能可靠、测量精准。

电能质量;ARM;FPGA;FFT变换;WINCE6.0

0 引 言

随着电力电子技术的快速发展,大量非线性、冲击性负载的投入使用,谐波干扰、电压波动和闪变等电能质量问题明显加剧,电能质量问题也不可避免进入人们的视线,研究和开发一种能实时精确计算和显示电能质量参数的仪器显得尤为必要。

传统的电能质量分析仪大多采用定点DSP来实现,DSP具有强大的数据处理能力,但DSP程序串行运行,当涉及到大批量数据计算任务时,DSP的劣势就显现出来了,在实时计算方面略显不足[1]。本文运用ARM和FPGA作为主协处理器来实现电能质量分析,更快速精准地实现对电能质量监测分析。

1 系统整体设计

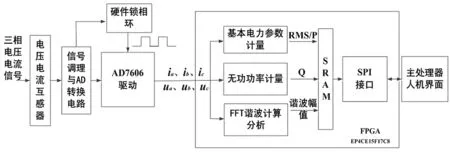

本文的系统总体结构如图1所示,主要包括前端的信号调理部分、AD信号同步采样部分(包括PLL)、FPGA逻辑计算部分以及ARM主处理器人机界面显示部分。

图1 系统总体结构框图

信号调理部分对输入的模拟电压电流信号滤波,电压值调整;AD信号同步采样部分将输入的模拟电压电流信号转为数字信号,同时实现对电网信号频率的同步跟踪以及电信号的同步采样;FPGA逻辑计算部分负责完成对基本电力参数、谐波等参量的计算分析;主处理器人机界面负责显示分析结果。

2 系统硬件设计

2.1主协处理器选型

本设计中数据计算部分尤为重要,Hilbert算法和FFT算法中涉及了大量的乘积累加和运算,需要耗费大量的时钟周期。FPGA是最符合本设计计算要求的器件,其有硬件乘法器,具有很强的数据并行计算能力,同时FPGA的最短窄脉冲捕获能力是最强的。

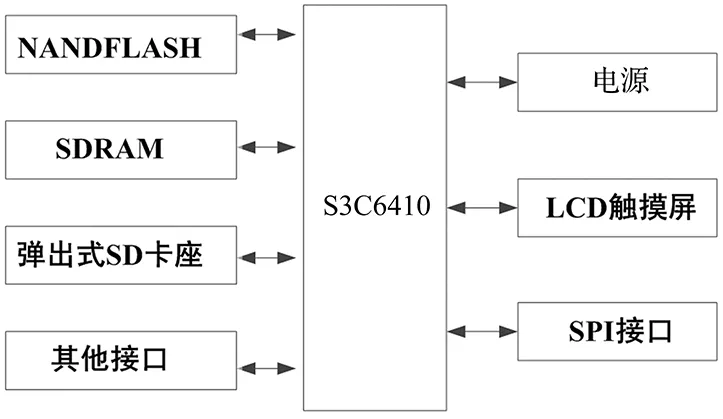

FPGA芯片选择Altera的EP4CE15F17C8,容量为15 408个逻辑单元(logic elements,LEs),504 Kbits的片内RAM,56个18×18 bit硬件乘法器,系统可靠性高,满足实验要求。实现人机界面的主处理器选择三星公司的S3C6410。

2.2信号调理与AD转换电路

ADI公司的AD7606为8通道16位ADC系统,采用了逐次逼近型(SAR)内核。支持±10 V/±5 V双极性信号输入、5 V单电源供电、200 kSPS的采样速率和高达95.5 dB的信噪比(SNR)。AD7606还集成了高输入阻抗的信号调理电路,包括输入箝位保护、二阶抗混叠滤波器以及等效输入阻抗固定为1 MΩ的输入缓冲电路。这大大简化了ADC的前端设计,二次互感器(PT/CT)输出的信号无需经过运放电路就可以直接输入AD7606。其典型的设计方案如图2所示。

图2 AD7606典型的设计方案

2.3锁相环电路

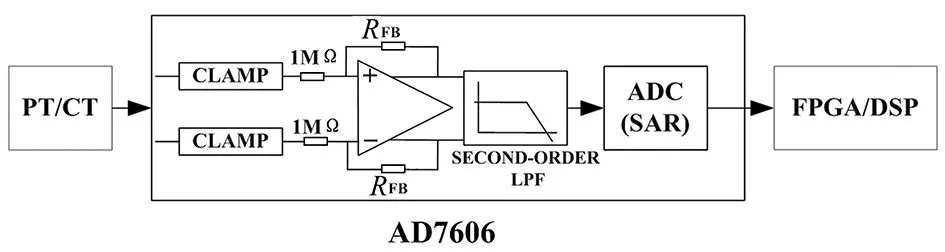

电力系统的频率会随着电力负荷的变化产生微小的变化,额定信号频率为50 Hz,容许频率误差分为±0.2 Hz和±0.5 Hz两种。为了确保后续无功功率和谐波计算的准确性,减少频谱泄露和栅栏效应,需要对电压信号的频率进行跟踪,达到频率同步[2]。频率同步的实现方法主要有软件同步和硬件同步两种,本设计选择硬件锁相环同步技术。通过对锁相环倍频电路产生的倍频脉冲计数的方法,获得信号周期及频率,同时将倍频脉冲作为同步采样脉冲,解决同步采样的问题。

锁相环芯片选型最重要的参数就是频率带宽,现在一般数字锁相环芯片支持的都是10 MHz及以上,如74HC4046芯片。本设计锁相环输入信号是50 Hz,经过256倍频,实现芯片的中心频率为12.8 kHz,选用与74HC4046引脚完全兼容的CD4046完全能满足要求。CD4046电源电压范围宽,输入阻抗高,功耗小,在中心频率f0为10 kHz下功耗仅为600 μW,特别适用于测量系统中使用[3]。

CD4046外围电路参数确定主要分为三个部分:倍频系数设定、中心频率确定和频率范围的确定。综合考虑采样率、AD的数据宽度和锁相环运行稳定性等因素,最后确定倍频系数N=256。本设计中,中心频率f0=12.8 kHz,电源电压5 V,结合电容的常用容值,选取C1=4.7 nF,R1=10 k。实际测试时发现在VCO的输入端输入Vcc/2时锁相环中心频率在12.8 kHz附近,故设计参数满足要求。锁相环的工作频率范围是由R1,R2和C1共同决定的,计算公式如下:

(1)

(2)

式中C0是寄生电容,约32 pF。设计中没有设定fmin,故R2引脚空置。将R1,R2,C1代入计算得VCO的振荡频率范围为0 Hz~21.2 kHz,应用电路如图3所示。

图3 锁相环应用电路

图3左侧是CD4046核心电路部分,其中引脚1是用来显示CD4046的工作状态,如果锁相环对输入信号处于锁定状态,该引脚为高电平,否则为低电平。右侧是由CD4046构成的分频器,即对应锁相环中1/N反馈部分。

2.4人机界面设计

2.4.1ARM11硬件系统

ARM11最小系统框图如图4所示。S3C6410可稳定运行在667 MHz主频以上,在图形、视频的处理和显示有强大的硬件加速性能,具有优化的存储器接口和外设接口,包括SDIO、LCD控制器等,非常适合作为人机界面。SD卡用于操作系统的烧写与数据存储,NAND-Flash用于操作系统的加载(见表1)。

图4 ARM11最小系统框图如图

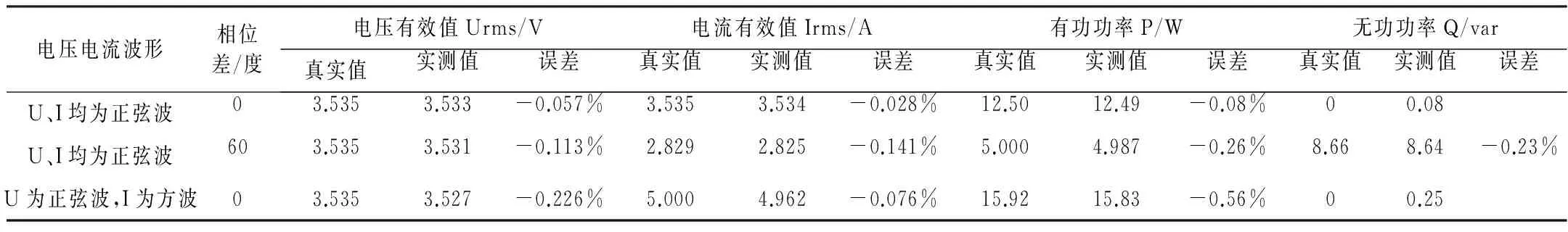

电压电流波形相位差/度电压有效值Urms/V电流有效值Irms/A有功功率P/W无功功率Q/var真实值实测值误差真实值实测值误差真实值实测值误差真实值实测值误差U、I均为正弦波03.5353.533-0.057%3.5353.534-0.028%12.5012.49-0.08%00.08U、I均为正弦波603.5353.531-0.113%2.8292.825-0.141%5.0004.987-0.26%8.668.64-0.23%U为正弦波,I为方波03.5353.527-0.226%5.0004.962-0.076%15.9215.83-0.56%00.25

2.4.2WINCE6.0操作系统与应用软件设计

微软公司的Windows Embedded CE 6.0(简称WINCE 6.0) 是一个实时的模块化多线程操作系统,支持抢占式多任务,能在多种微处理器下运行[4]。

WINCE 6.0的应用软件开发环境选择Microsoft Visual Studio 2005,使用C/C++的图形化界面语言MFC(Microsoft Foundation Classes)。应用软件设计包括应用程序和SPI驱动程序。三星公司生产S3C6410芯片为SPI驱动提供了三种工作模式,分别为轮询模式、中断模式和DMA(Direct Memory Access)模式,为加快数据传输速度,提高CPU利用效率,系统中使用的是DMA模式。

3 系统软件实现与测试结果

编写AD7606驱动程序,同时将锁相环的倍频脉冲作为同步采样脉冲,实现模拟量的正确采样和数据的精确读取。结合FFT变换以及Hilbert变换等,计算得到基本电力参数、无功功率及谐波的结果,再通过人机界面将结果显示给用户。

3.1电压、电流有效值和有功功率计量

在本系统中把电压有效值(Urms)、电流有效值(Irms),有功功率(P)归属为基本电力参数,根据电路理论中物理量的定义就可以算出结果,不需要采用复杂的算法,下面具体介绍其计算:

(3)

(4)

(5)

式中rms下标表示有效值,u(t),i(t)分别为电压信号和电流信号的瞬时值,T为信号周期。

由于电网的电压信号u(t),电流信号i(t)都是时间连续的模拟量,本文的设计思路是用逻辑器件(FPGA)来计算电力参数,由于采集到的电压、电流序列在时间上都是离散的,所以需要离散化的计算方法。通过对上述电力参数计算过程离散化得到计算公式如下:

(6)

(7)

(8)

式中的N指一个周期或整数个周期内采样的点数。计算结果的精度和ADC的分辨率和N的取值有关系。

在16位并行数据线上依次读取三相的电压和电流的采样数据,然后计算有效值和有功功率。在同一个采样周期内基本电力参数的计算可以直接进行,不需要额外创建缓存去保存中间数据。每个采样周期内同时进行N计数,当N=256则表示一个信号周期的计算完成,同时把计算结果保存到SRAM中。

3.2无功功率计量

无功功率的定义目前没有统一的标准,无功功率的测量也没有统一的算法,其中被IEEE标准采用且应用广泛的一种定义为:

(9)

式中Un,In分别为N次谐波对应的电压和电流有效值,Φn是N次谐波电压和电流的相位差。在不考虑计算精度的前提下,目前存在的计算方法主要有:均方根算法、傅里叶测量算法以及移相算法。本设计采用移相算法,Hilbert算法是数字移相算法中有代表性的算法。该算法计算量适中,并且对于非周期信号的分析也广泛使用,通过把电压信号移相-90°的方法,把无功功率计算转化成有功功率计算类似的过程(如表2所示)。

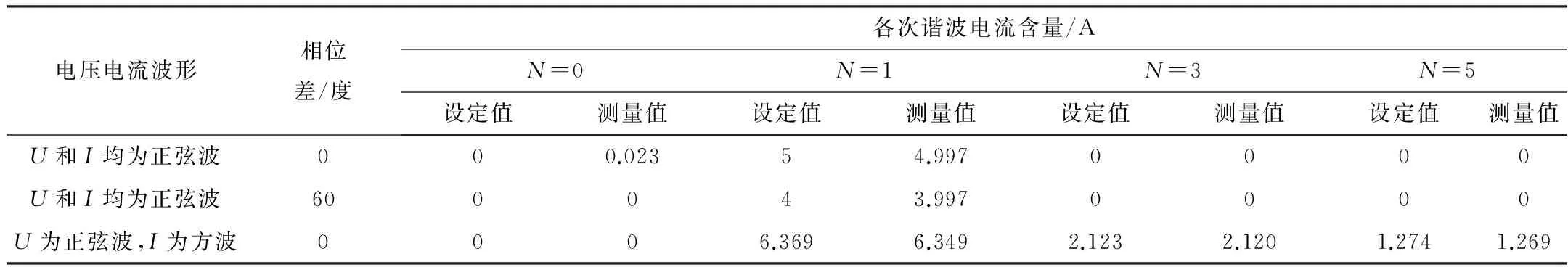

表2 电流通道设定谐波含量与系统测量谐波含量对比结果

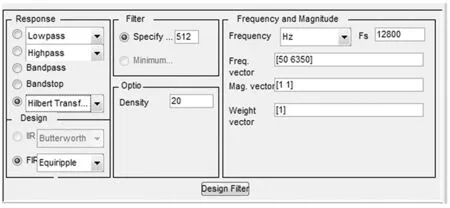

Hilbert算法本质上是一个数字滤波器,FIR(Finite Impulse Response)型数字滤波器能保证精确和严格的线性相位[5]。该系统不仅稳定而且具有线性相位,因而无相位失真。借助MATLAB的Fdatool(Filter Design and Analysis Tool),来获得滤波器的系数,再将系数量化后导入到FIR IP核中[6]。 Hilbert滤波器具体设置参数如图5所示。

图5 滤波器设计

3.3谐波计量

谐波计算采用FFT算法,该算法本身结构复杂,为此,Altera公司提供了专门的FFT IP核,开发人员只需要根据自己的设计要求定制参数就能得到一个功能优化的FFT模块[7]。

进入FFT配置界面后,首先需要配置的是Transform Length、Data Precision、Twiddle Precision,本设计这三个配置量分别设置为256、16、16。

其次需要设置FFT的架构,有Streaming,Buffered Burst,Variable Streaming和Burst四种架构可供选择。本设计中周期约为78 μs,并不需要浪费很多资源来换取速度,选择Burst架构。输出选择有Single Output和Quad Output两种选择,根据本设计需求可知选择Single Output。

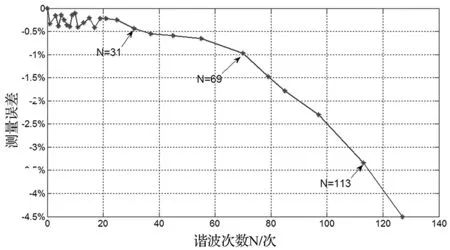

测量时,我们在幅值为5 V的基波上叠加幅值为0.125 V的N次谐波。可以看出次数增大,谐波测量误差也增大,并且当谐波次数达到70左右时误差接近1%。测量误差曲线如图6所示。

图6 谐波测量误差曲线

3.4系统测试结果分析

本系统计算参数有信号有效值,有功功率和无功功率,谐波含量等。数据源是电压和电流,为了测试方便,测试时采用双通道信号源模拟两个互感器的输出,其中一个通道表征电压互感器输出信号,另一路表征由电流互感器输出转化的电压信号,且假设该路电压信号和表征的电流信号之间数值转换比是1∶1。

为了有针对性的验证不同电力参数计算的准确性,在测试环节,本文采用了三组有代表性的输入,不同组输入信号在幅值、相位和波形方面有差别。

第一组为电压幅值5 V,电流幅值5 A,均为正弦信号,电压和电流信号同相位。第二组为电压幅值5 V,电流幅值4 A,均为正弦波,电压相位超前电流60°。第三组为电压为幅值5 V的正弦波,电流幅值5 A的方波,电压和电流同相位。其电压、电流有效值、有功功率以及无功功率的测量结果如表1所示,选择电流通道,其各次谐波电流含量设定值与测量值如表2所示。

由上述表格可知,基波的基本电力参数及无功功率的误差基本上可以保证在±0.5%以下。其次通过比较各次谐波含量的测量值和理论值,经过验证,理论计算的各次谐波含量和测量显示的谐波含量完全相符,误差小于±1%。通过上述三组实验,可以确定本系统对基本电力参数的测量计算和谐波信号分析都很准确。

3.5人机界面显示

基于WINCE6.0操作系统的MFC人机界面为电能质量参数显示界面,其内容包括频率、三相基本电力参数(电流电压有效值、有功功率及无功功率等)、谐波分析三部分的参数,显示结果如图7所示。

图7 电能质量参数显示界面

4 结束语

本系统选用ARM/FPGA作为主协处理器,通过硬件锁相环技术实现对电网频率同步跟踪,结合对FFT算法、Hilbert算法分析研究,成功实现基本电力参数测量、谐波分析等功能,同时开发了基于ARM和WINCE6.0操作系统的人机界面软件。该新型电能质量分析仪功能全面、实时性强、性能可靠、测量精准、升级潜力大、体积小、成本低,既可用于家用电表的计量,也可用于电网端实时在线监控,具有广泛的应用空间及市场空间。

[1] 柏玉峰. 基于DSP的高精度电能质量分析仪的研究[D]. 四川:西华大学, 2006.

[2] 张瑛,牟龙华,刘军. 电力系统频率测量及跟踪[J]. 电力系统及其自动化学报, 2003,15(3):35-36.

[3] 宋吉江,牛轶霞. 锁相环技术及CD4046的结构和应用[J].半导体技术,2000,25(3):60-63.

[4] PHUNG S. Professional microsoft windows embedded CE 6.0[M]. John Wiley & Sons, 2008.

[5] 吴思聪,赵威威,陈燕红. Hilbert变换在无功电能计量中的应用研究[J]. 电测与仪表,2009,46(6):35-38.

[6] 聂仙娥,许爱国,赵河明,等. 基于MATLAB的FIR型希尔伯特变换器设计[J]. 现代电子技术,2011,34(7):113-116.

[7] 孙桂玲,纪永鑫,张潺潺. 高速高精度FFT IP核的设计与仿真研究[J]. 系统仿真学报, 2010, 22(8):2018-2022.

Research Design of a New Power Quality Analyzer Based on ARM and FPGA

ZHOU Ping, SHU Guo-hua, CHEN Min-jie, DING Jun-wu

(School of Electronic Information and Electrical Engineering, Shanghai Jiao Tong University, Shanghai 200240, China)

As an important tool for grid power quality monitoring and analysis, the power quality analyzer is of great significance for the improvement of the quality of grid power supply. ARM/FPGA as main co-processor, synchronous frequency tracking through hardware PLL, synchronous sampling of grid signal, as well as FFT and Hilbert transformation based on FIR filter, are used to realize basic power parameter measurement. harmonic analysis and other functions. In the meantime, an HMI software is developed on the basis of ARM and WINCE6.0 operating system. The testing system has friendly man-machine interaction, real-time measurement and display functions. Experimental results indicate that the analyzer is a full-featured one with reliable performance and accurate measurement.

power quality;ARM;FPGA; FFT transformation;WINCE6.0

国家电网公司科技项目资助(SGZJ0000BGJS1400211)

10.3969/j.issn.1000-3886.2016.02.034

TM933

A

1000-3886(2016)02-0111-04

周平(1990-),男,硕士生,江西赣州人,研究方向为电力电子技术、开关电源以及嵌入式应用。殳国华(1969-),男,硕士,副教授,浙江海宁人,上海交通大学电工中心副主任,研究方向为电力电子、计算机控制技术及嵌入式系统应用。陈敏捷(1991-),男,硕士,江苏人,研究方向为开关电源、电力电子技术。 丁君武(1990-),男,硕士,安徽人,研究方向为嵌入式应用。

定稿日期: 2015-10-20