SATA硬盘控制器的FPGA实现

2016-10-18贾效玲张刚张博

贾效玲,张刚,张博

(太原理工大学信息工程学院,太原030024)

SATA硬盘控制器的FPGA实现

贾效玲,张刚,张博

(太原理工大学信息工程学院,太原030024)

设计一款高性能的SATA硬盘控制器IP核。基于Xilinx公司的Virtex-5系列FPGA,参考SATA2.5协议,运用VHDL硬件描述语言,采用模块化的设计理念,完成IP核的设计。搭建了验证平台,对IP核的性能进行了测试,经测试该控制器IP核能正确地完成读、写、设备复位、设备识别等操作,且稳定性良好。同时编写了PetaLinux操作系统下的驱动程序,便于嵌入式系统的应用。

SATA2.5,控制器,FPGA,VHDL

0 引言

随着嵌入式技术的发展,嵌入式系统对存储器容量的要求越来越高,特别是图像采集、视屏监控等系统。硬盘容量大、价格便宜非常适合需要大容量存储的嵌入式系统,而目前很少有成熟的硬盘嵌入式接入方案。本文详细分析了SATA协议结构,设计了相应的SATA控制器,并在FPGA上进行了验证,基于PetaLinux设计实现了文件系统接口,为硬盘的嵌入式系统应用提供了良好解决方案。

1 SATA简介

2001年Intel等厂商组成的Serial ATA委员会提出速度为150MB/s的SATA总线接口,高于并行ATA的最高理论速度133 MB/s,SATA2.0和SATA3.0更是分别达到了300MB/s和600MB/s[1]。

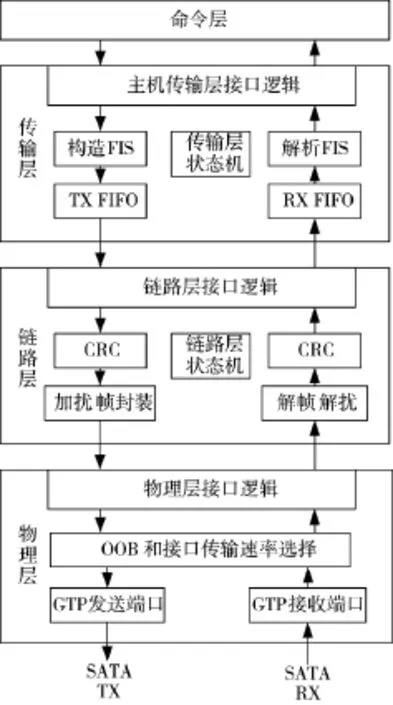

SATA接口由电源和上行、下行两个数据通道组成,数据通道由3根地线将两对差分信号线隔开,形成SATA独占通道带宽的点对点连接方式[2]。按功能SATA协议分为物理层、链路层、传输层和命令层,协议的层次结构如图1所示。主机和设备之间,除了物理层,其他各层均通过消息虚拟连接。物理层是协议的最底层主要负责码流的收发及串并并串转换;链路层主要负责消息的无差错传输,包括8B/10B编解码、加解扰、CRC校验等;传输层主要负责生成与解析帧信息结构(Frame Information Structures,FIS);命令层主要负责生成和解析访问SATA硬盘的操作命令[3]。

2 SATA控制器

2.1总体设计

设计按照SATA协议分为4层,各层内部通过控制模块和数据通路实现相应功能,各层之间相对独立,发生错误时只需修改该层的模块,而不会对其他层造成影响。

控制模块通过有限状态机实现协议的时序控制功能,相邻层的状态机相互配合实现数据的传输控制。状态机用VHDL硬件语言描述,控制各层有条不紊地处理数据。数据通路分为发送和接收两个通道,采用FIFO方式存储。

发送数据时,命令层将传来的数据和命令按照SATA协议要求传给传输层,传输层接收数据并封装成FIS,存放于FIFO中;数据链路层对接收到的FIS进行CRC校验和加扰,并且加上帧头帧尾送到物理层;物理层由RocketIOGTP来实现,由于GTP具有8B/10B编解码功能,所以链路层的8B/10B编解码功能可以省略[4]。物理层的OOB信号用于完成初始化,速度协调模块自动识别硬盘速率。GTP能够对接收到的消息帧进行8B/10B编码,然后经过并串转换按照差分的方式发送出去。接收过程正好相反。物理层差分信号RX和TX分别与硬盘的差分收发信号线相接。系统结构框图如图2所示。

2.2物理层

主机与设备之间的通信基础是物理层,通过SATA接口连接。其主要功能包括:①接收高速串行差分信号并转换成并行数据;②将并行数据转换成高速串行差分信号发送;③实现主机与设备的初始化连接。

Xilinx Virtex5芯片内嵌RocketIO GTP高速串行收发器可直接来实现SATA物理层[5]。接收数据时它将3Gb/s的串行码流转换成并行数据流,发送时把并行数据串行化发送[6],同时还能产生用于初始化的带外信号(OutOfBand,OOB)。物理层协议定义了COMRESET、

COMINIT、COMWAKE 3种带外信号,均表现为在连续的Align原语簇间插入时间长度不同的空闲[7]。

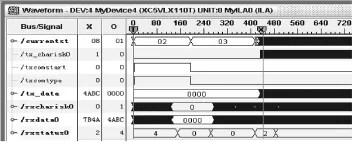

初始化连接的目的是建立链路层数据传输的通路,其过程为:首先主机发送信号COMRESET,设备检测到COMRESET信号后发送信号COMINIT响应,主机确认收到信号COMINIT后发送信号COMWAKE确认,然后设备以信号COMWAKE响应,接着主机与设备进行速率匹配,匹配成功后主机发送SYNC原语,当主机端接收3个连续的非ALIGN原语时表示连接建立成功。物理层的测试结果如图3所示,rxstatus0表示的是接收到OOB信号的类型,‘4’表示COMINIT信号,‘2’表示COMWAKE信号。

图2 系统架构图

图3 物理层测试结果

2.3链路层

链路层接收传输层的FIS,插入原语封装成帧后交给物理层发送,并从物理层得到的数据中提取出FIS后送到传输层,同时进行CRC值的计算和对除原语以外的所有数据(包括CRC值)进行加解扰操作[8]。扰码的目的是减少数据中连续‘0’或‘1’的长度,以便于提取定时信息,使码流更适合基带传输[9]。扰码建立在线性反馈移位寄存器的基础之上,其特征方程为:

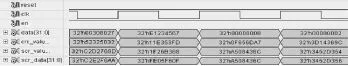

SATA协议采用CRC32校验作为差错检测,并规定初始的CRC值为0X52325032。扰码和CRC值计算的仿真结果如图4所示,由图可知第1个原始数据是0X00308027,计算的CRC值为0X11E353FD,扰码器的输出为0XC2D2768D,加扰后数据输出0XC2E2F6AA。

图4 扰码和CRC仿真

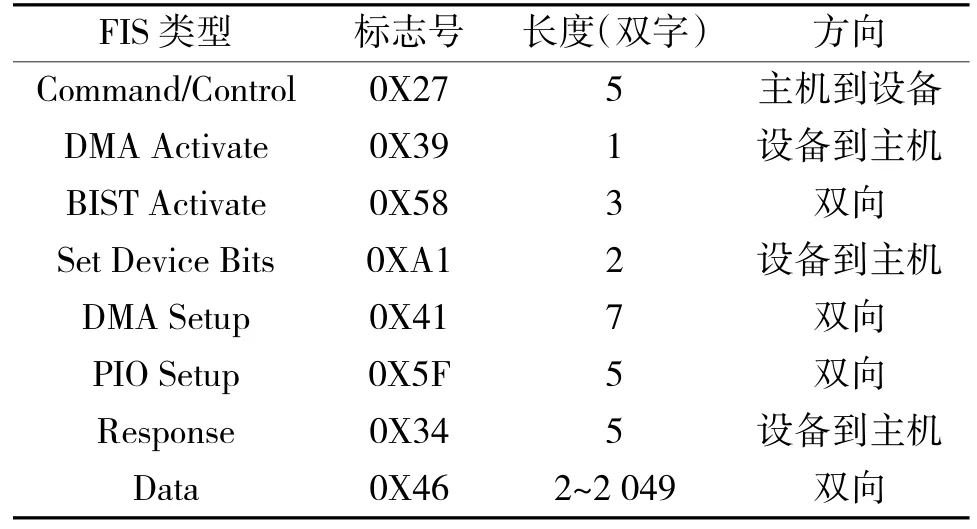

2.4传输层

传输层的核心是FIS,它只需生成与解析帧信息的结构,而不关心帧数据接收和发送过程。协议定义了8种FIS,它们长度不等但结构类似,第一个双字的低8位标志了类型号,各种FIS的基本信息列在表1。常用的3种FIS:Command/Control FIS,用于主机向设备发送命令、参数等;Response FIS,用于设备向主机返回状态;Data FIS,用于数据传送。

用缓存7个双字(非数据FIS的最大长度)实现非数据FIS的封装,根据FIS的类型决定缓存的内容和长度,然后由链路层发送。对于数据FIS,先发送用于表示类型的第1个双字后,直接将命令层的消息交给链路层发送[10]。

表1 帧信息结构

2.5命令层

命令层主要解析命令,SATA协议完全兼容传统ATA命令。协议定义了两组操作寄存器实现命令操作,分别为命令寄存器组和控制寄存器组。命令寄存器组包括命令和参数寄存器,错误寄存器等;控制寄存器组主要用于对设备的控制,包括控制寄存器和辅助状态寄存器。

3 设计验证

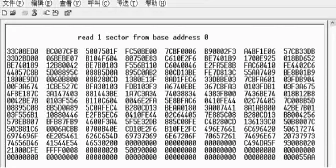

在XILINX的EDK环境下,把设计当作一个定制IP核,挂载到PLB总线上来对IP核进行测试。如图5所示是读取SATA硬盘的主引导扇区(硬盘的0号扇区)中的数据,从超级终端打印的结果。主引导扇区的最后两个字节是其签名值55AA,图中读出的数据的后两个字节也是55AA,说明控制器能够正确地完成读硬盘操作。同时对写硬盘、设备识别、硬盘复位等功能进行了测试,结果证明控制器能很好地完成这些操作。

图5 读操作测试结果

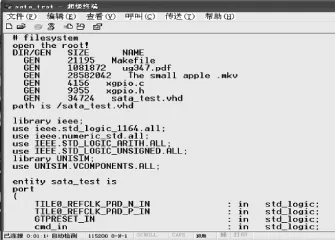

为了方便嵌入式的应用,并进一步测试硬盘控制器的性能,在XILINX公司的EDK环境下,把所设计的SATA硬盘控制器封装成一个定制IP核,挂载到FPGA内嵌MicroBlaze处理器的PLB总线上,当作处理器的一个设备,移植Petalinux操作系统到MicroB-laze,在Petalinux操作系统下设计独立的FAT32文件系统,通过文件系统来实现控制器IP核的通信测试。测试中文件系统能很好地调用设计控制器完成读,写,删除等文件操作,说明硬盘控制器性能良好。图6是读取硬盘根目录下一个文件并显示的结果,由图可知硬盘的根目录下一共有6个文件,当前读取的文件路径为/sata_test.vhd,其大小为34724个字节。

图6 控制器测试结果

4 结论

本文设计了一个集成度高、可扩展性强、运用灵活方便的SATA硬盘控制器,同时基于Xilinx公司的软硬件协同设计平台,开发了控制器的文件系统接口程序,特别适合需要大容量存储(如视屏采集)的嵌入式系统,具有良好嵌入式应用前景。

[1]陈杰,张伟,张顺生.SATA2.0控制器的设计与实现[J].计算机应用,2011,31(2):25-26+32.

[2]申济菘.SATA IP的设计与优化[D].南京:南京大学,2013.

[3]Serial ATA Revision 2.5[S].USA:Serial ATA International Organization,2005.

[4]JOSE S.Virtex-5 FPGA RocketIO GTP Transceiver User Guide[R].Xilinx Coporation,2008.

[5]SAWYERN.Source-Synchronous Serialization and Deserialization[R].Xilinx Corporation:Application Note XAPP1064(v1.1),2010.

[6]孙志雄,谢海霞.基于FPGA的高速串并/并串转换器设计[J].现代电子技术,2014,37(8):151-152.

[7]杨佳朋,张刚,郝敏.基于RocketIO的SATA物理层实现[J].电视技术,2013,37(3):70-72.

[8]王超,刘伟,张德聪.基于SATA的嵌入式直接存储系统[J].计算机工程,2012,38(12):232-235.

[9]璩泽旭.高速大容量存储系统关键技术研究与实现[D].西安:西安电子科技大学,2013.

[10]荆旭.基于FPGA的SATA协议分析及收发控制器设计[D].西安:西安电子科技大学,2014.

FPGA Im p lementation of SATA Hard Disk Controller

JIA Xiao-ling,ZHANGGang,ZHANGBo

(School of Information Engineering,Taiyuan University of Technology,Taiyuan 030024,China)

The paper designs a high-performance SATA controller IP core.It takes SATA 2.5 protocol for reference and is implemented on the basis of FPGA of Virtex-5 family of Xilinx with modular design concept in VHDL language.A platform for IP core performance verification is built. The test results indicate that the controller IP can realize many operations,such as reading,writing,device reset,identification and so on.And it has good stability.Meanwhile,it also finishes the operating system drivers of PetaLinux.It can facilitate the application of embedded systems.

SATA2.5,controller,FPGA,VHDL

TP333.2

A

1002-0640(2016)09-0182-03

2015-07-05

2015-08-07

贾效玲(1990-),女,山西汾阳人,硕士研究生。研究方向:嵌入式。