消除状态机毛刺策略探讨

2016-09-24陈梦婷卫津逸张怡昕张立

陈梦婷 卫津逸 张怡昕 张立

摘要 状态机简写为FSM(Finite State Machine),是数字系统的重要组成部分。本文结合AD9822的工作特点,以AD9822的序列发生器的采样控制过程为例,分析了状态机产生毛刺的原因,讨论并比较了三种消除毛刺的方案,分别给出了调整编码消除毛刺和状态码直接输出消除毛刺这两种方案的VHDL源程序,利用Quartus Ⅱ仿真,成功消除毛刺。

关键词 AD9822 序列发生器 状态码

中图分类号:TN911.7 文献标识码:A DOI:10.16400/j.cnki.kjdkx.2016.07.071

状态机是一种重要的数字控制系统设计方法,它的速度和效率,以及在执行时表现出的很强的可靠性和安全性,都是设计时的重要优势。除此以外,与其他方法相比,用VHDL描述状态机的表达更加多元丰富,结构清晰、易读,容易理解;VHDL语句在调试修改和移植模块方面也有其独特的特点。

1 AD9822介绍

AD9822是一种CCD视频信号处理的低功耗处理器,因其具有高速数据传输能力和准确性,被广泛用于研究、过程控制等。

AD9822包括3路采样电路,即VING、VINR、VINB,分别是绿色、红色、蓝色通道信号输入。每一路由相关双采样器CDS,一个嵌位开关,可编程增益放大器PGA,数模转换器DAC,通过多路选择器选择把信号送给模数转换器ADC,通过位宽为8的总线的输出。这样由CCD输入的模拟视频信号便被合理地调整,进而转换成数字信号,最后交由上层处理。

AD9822是通過三线双向串行接口来进行控制其工作模式和状态的,三路信号分别是SCLK、SLOAD、SDATA。外部控制器(如FPGA)给出合理的时钟信号SCLK,在该时钟下数据通过SDATA传输到AD9822的内部寄存器中。

2应用VHDL设计状态机

设计状态机的传统方法需要大量且繁琐的状态分配、状态表绘制和化简。但利用VHDL硬件语言可以最大程度地跳过这些,直接用状态图描述,且涉及到的任意状态都可表达为CASE WHEN中的CASE语句。

具体步骤如下:

(1)根据系统特定要求,确定不同状态的数量、状态相互转移的条件及每个状态输出的信号值,进而画出状态转移图;(2)根据状态转移图来编写相应的VHDL程序;(3)对功能进行仿真及验证。

本实验的主要目的就是基于己选定的芯片AD9822,设计一个产生序列的计数型信号驱动电路。

3毛刺产生原因

状态机在硬件上通常由主控时序电路、主控组合电路及辅助电路这三个部分构成。其中,主控组合电路的功能是由当前的状态值和外部控制信号来确定下一状态的转移方向,并且确定内部其他电路输出的信号内容。一方面,由于存在组合逻辑电路,整个电路的输出信号会出现毛刺现象,换句话说,即竞争冒险现象;另一方面,当状态信号是多位值时,在此电路中有多路信号对应于该信号。因为传输延迟,每路信号的值发生的改变存在先后,令状态迁移时在初始状态和目的状态之间会出现临时状态“毛刺”。

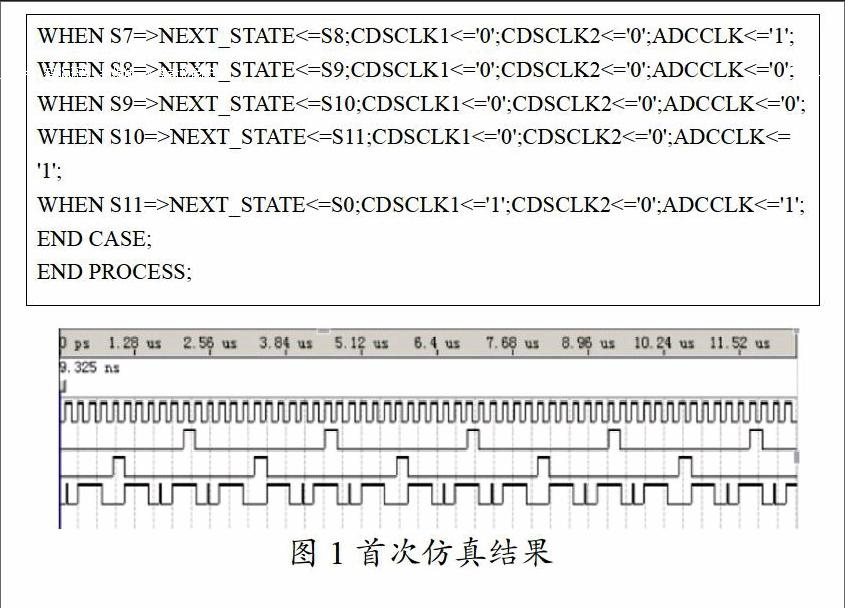

如,根据AD9822的Datasheet,时钟信号SCLK含CDSCLK1、CDSCLK2和ADCCLK三个外部控制端口,用十二个状态描述其变化。首次采用状态机编写程序的主要代码如下:

将每个状态的维持时间设为10ns,其仿真结果为(图1):

如图1所示,其中在整个周期中的第一个时钟和第二个时钟之间会产生毛刺。

4毛刺的消除方案

“毛刺”只会发生在时钟两个有效边沿之间,因此一般情况下,“毛刺”在同步电路中不会产生严重影响。但当输出信号是其他功能电路的控制信号时,便会让受控电路发生错误动作,产生故障,继而导致整个系统的混乱,比如作为异步控制、三态使能控制或时钟信号使用时。所以,当作为控制信号时,必须修改程序消除毛刺。消除“毛刺”通常有以下三种方法:

(1)对状态的编码进行调整,以使相邻的状态转移只有一个信号码变化,从而去除了竞争冒险的可能。一般采用格雷码来编码。

(2)采用时钟同步,即向组合逻辑电路引入时钟信号。状态机每次输出都会在时钟信号的同步下经过一个附加的寄存器,故可保证输出无毛刺。但这种方法存在一定的缺点:由于增加了寄存器,直接增大了硬件开销,这对本身寄存器资源比较少的芯片是有很大弊端的;从状态位到达输出必须经过两级组合逻辑电路,这对系统时钟的最大工作频率有一定限制:输出信号需要在时钟节拍下加载到附加寄存器上,所以实际得到的输出信号会比状态转移延迟一个时钟周期。

(3)直接把状态码作为输出信号。状态和输出信号同步,可以优化译码电路,因此不会出现竞争冒险。该方法占用芯片资源少,同步变化速度很快,所以为较好的方法。但在编码过程中,可能会增加状态位,出现多余状态。虽然在控制状态转移的时候可以使用WHEN OTHERS来处理,但是有的时候并不能有效地控制多余状态,故适用于输出信号数量比较小的情况。

因为本实验涉及的状态机编码较为简单,输出状态较少,故采用第一种和第二种方法来解决毛刺现象。

4.1调整编码消除毛刺

因本状态机不是顺序迁移,并不采用格雷码编码方式,但进一步考虑到毛刺只出现在第一个状态和第二个状态之间,且若未指明输出信号改变,其输出不会改变,故将多余的信号输出语句删除,其主要程序如下:

毛刺成功消除,故在时序较简单时,若出现毛刺,应首先考虑该种方式。

4.2状态码直接输出消除毛刺

该方法将先将状态码以常数表示,输出时将状态码的某位对应输出,故其状态码的设置是最首要的问题,需要设置识别码将相同的输出码分别开来,具体实现如下:

写出输出的应正确输出的输出码,从左至右分别对应ADCCLK、CDSCLK2、CDSCLK1,将其相同的输出码归类为一组,按组别的最大大小确定识别码的位数(本例最大为5个,故为3位),每组的识别码从0开始递增直至编码完毕,如表1所示:

按表1调整后主要程序如下:

仿真之后成功消除毛刺,在输出信号不多的情况下,若尝试过调整编码的方法仍不能成功的话,这种方法也是一种简单易行的方法。但是输出信号个数过多的话,状态码位数过多,会产生很多多余状态,导致输出不可控。

其仿真图如图2:

5结束语

在数字控制系统设计中状态机灵活易用,但是由于VHDL编码的状态机输出信号有可能产生竞争冒险,所以为了避免系统工作状态混乱,必须对症下药来消除毛刺。若使用有限状态机编码遇到毛刺问题,首先采用调整编码的办法,若无法解决再采用状态码直接输出的办法,最后采用时钟同步的方法。本文作为实例,为之后状态机毛刺的解决提供了良好的参考。