一种采用标准数字单元实现的5bit 100MS/s全数字闪烁型模数转换器

2016-09-21薛香艳周雪荣任俊彦

薛香艳,周雪荣,叶 凡,任俊彦

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

一种采用标准数字单元实现的5bit 100MS/s全数字闪烁型模数转换器

薛香艳,周雪荣,叶凡,任俊彦

(复旦大学 专用集成电路与系统国家重点实验室,上海 201203)

设计了一种全数字实现的5bit闪烁型模数转换器,该设计的核心思想是通过差分延时链对,将输入的差分模拟信号转换为延时信号,再经过锁存器得到与相应参考电压的比较结果.该数字比较器的参考电压内置于差分延时链对,无需从外部输入.采样保持电路的开关和保持电容也使用数字库中的合适器件代替.该模数转换器完全采用标准数字单元库中的单元搭建而成,与传统实现方法相比,在功耗、面积及设计复杂度上均有了较大程度的改善.电路采用TSMC 65nm工艺设计,核心面积为0.02mm2,在采样频率为100MS/s的情况下,后仿真功耗低达0.6mW,SFDR为37.89dB,ENOB为4.55bit.

闪烁型模数转换器; 全数字模数转换器; 内置参考电压

随着半导体工艺节点的不断降低,由于短沟道效应、漏电流增加等影响,模拟电路在较小尺寸下的工作性能下降明显,相比较而言,因为处理的信号是离散的“0”和“1”,数字电路更能充分利用工艺进步的优势.此外,由于对噪声的不敏感,数字电路相对于模拟电路设计效率更高.传统的模数转换器(Analog-Digital Converter, ADC)主要由模拟电路构成,在功耗、面积及设计复杂度上存在颇多问题,所以全数字模数转换器的研究显得尤为重要.

全数字ADC的设计难点主要在于比较器.一种思路是利用输入信号控制同一个延时单元组成的延时链,在延时与控制信号呈反比例的假设条件下,一定时钟的触发后对各个延时单元输出的上升沿进行计数,作为低位数字信号的输出.而高位信号则采用计数器来完成[1-2].这种方法由于用到位数较高的计数,无法实现高速信号的处理.另一种是利用统计学的思路,利用比较器本身参考电压由于器件不匹配而产生偏差,并且呈高斯分布的规律.输入信号输入比较器后,由于每个比较器的参考电压偏差各异,比较结果可能为“0”或者“1”.输入信号越大,输出结果为“1”的可能性越大.如果比较器数目达到一定规模,所有比较结果相加之和与输入信号呈正相关关系[3-4].这种方法用到较多的比较器和较为复杂的逆高斯变换计算.

本论文基于数字标准单元库设计了一个全数字的闪烁型模数转换器(Flash ADC),该电路从采样保持电路到比较器和输出电路全部采用数字标准单元搭建而成.其基本比较单元为内置差分参考电压的延时比较器(Embedded Differential Reference Time Delay Comparator, EDR TDC).每个EDR TDC由一对针对不同特定参考电压设计的电压延时转换器(Voltage to Time Converter, VTC)组成,由于参考电压内置于EDR TDC中,故而无需从外部输入.采样保持电路中的开关用数字库中的三态门代替.这种全数字的Flash ADC可以明显改善传统Flash ADC的面积、功耗以及设计复杂度.

1 工作原理及电路结构

在常见的几种ADC结构,比如逐次逼近型ADC、流水线型ADC、Flash ADC、Δ-∑ ADC中,Flash ADC的结构最为简单,适合进行数字实现.典型的差分Flash ADC结构如图1所示.图1的实现思路是先通过分压产生比较所需的各个参考电压,每个参考电压通过相应的比较器与输入信号并行比较得到温度计码输出结果.为了保证参考电压精度,必须增加阻值提高电阻之间的匹配度,由于电阻所占面积与阻值存在正相关关系,这样将会带来较大的面积成本.传统比较器采用开环运放设计,为了保证足够的精度,需要开环比较器有尽可能大的增益,随之而来的是管子尺寸的增加,因此带来面积和功耗的浪费.

如果要全部使用数字电路实现,参考电压的产生不能够再使用电阻来分压得到;同时,传统开环运放比较器也不再适用.如果能够将参考电压内置于数字实现的比较器中,则可以同时解决这两个问题.数字比较器常用的思路是先将模拟信号通过VTC转化为延时信号,再通过锁存器锁存得到比较结果.但并没有一个系统的方法将特定参考电压内置于这种比较器中.为了解决这个问题,本设计详细探究了内置参考电压比较器(EDR TDC)的设计方法,下面详细阐述EDR TDC的工作原理.

图2表示两个完全相同的VTC组成的比较器的工作原理.图3显示VTC的延时随输入电压增加而减小,Vip,Vin分别控制两个VTC,二者共用相同的输入时钟Clock.图4是全数字Flash ADC的时序图.由图2可知,可以通过比较输出信号上升沿(或下降沿)的到来先后得到Vip和Vin的比较结果.

从另一个角度来看,这两个VTC实现了(Vip-Vin)和0的比较.假设Vip和Vin为一对共模电压为Vcm的差分信号,两个相同的VTC组成的比较器内置了(Vcm,Vcm)这一对差分参考电压,也就是说,此处的差分参考电压Vrefp,Vrefn此时恰好重叠在Vcm处.进一步可以得到一个结论: 如果两个VTC不同,那么相应的内置等效差分参考电压Vrefp,Vrefn将会离开Vcm,向相反的方向移动.具体来说,假设有分别受Vip和Vin控制的VTC A和VTC B,当且仅当Vip,Vin分别等于Vrefp,Vrefn时,两个VTC的输出信号上升沿同时到达,如图5(a)所示.这样,假如Vip,Vin改变,两个VTC输出的上升沿将会分开.如果Vip大于Vrefp,Vin小于Vrefn,VTC A的延时将小于VTC B,锁存可得数字输出“1”,如图5(b)所示;如果Vip小于Vrefp,Vin大于Vrefn,VTC A的延时将大于VTC B,锁存可得数字输出“0”,如图5(c)所示.这样,VTC A和VTC B组成的比较器实现了(Vip-Vin)和(Vrefp-Vrefn)的比较.以上就是所谓EDR TDC的工作原理.

对于5 bit的Flash ADC,需要31个内置不同参考电压的比较器.每个EDR TDC基于一对特定参考电压,根据图5(a)原则进行设计.事实上,只有16个EDR TDC需要精细设计.因为是差分实现,每个EDR TDC中两个VTC交换位置之后,会产生和原来相对应的另一对参考电压.例如,内置参考电压对为(Vrefp,Vrefn)的EDR TDC在两个VTC交换之后会变为(Vrefn,Vrefp).

图6是本设计的基本结构.Clock控制信号的采样保持电路,在信号保持期间,Pulse在保持后的差分信号的控制下,通过31个不同的EDR TDC,并在随后的latch的控制下得到相应的温度计码比较结果,比较结果最后在OUTPUT的控制下得到同步,并最终转换为二进制码输出.其中Latch只在RST为高电平时工作,从而避免在采样阶段发生无意义的锁存,以节省功耗.

2 电路实现

2.1采样保持电路

最基本的采样开关是由采样MOS管和保持电容组成,如图7所示.其中MOS管开关可以等效为阻抗为RON的导通电阻,而漏极寄生电容Cp和后面的电容CH构成了一个低通滤波器.本设计的关键是分别寻找可以替代采样开关和保持电容的数字单元模块.

采样开关是采样保持电路的关键部分,这里问题主要在于如何选取合适的模块来行使开关的功能.因为在标准CMOS工艺中,NMOS的P衬底总是与地连接的,而PMOS的N阱则未必在一个固定电位上,所以模块中执行开关功能的一定是PMOS.为了让PMOS能够在不受干扰的情况下独立进行采样,最终选定了三态门作为基本的采样单元,如图8所示.

输入I接高电压VDD,这样图中虚线部分一直为低电平,从而使灰色部分的管子全部关断.使能端OE输入时钟,经过反向后加在虚线框中的PMOS管MS的栅极,输入待采样信号Vin从源级通过MS在OE的控制下被周期性地采样.这样合理地设置输入信号,可以保证晶体管MS在不受干扰的情况下作为采样开关正常工作,并且输入输出信号均为模块本身的输入输出,无需额外引出端口.

保持电容用数字标准单元库中的去耦合电容实现.去耦合电容电路结构如图9(见第414页)所示,它是由PMOS和NMOS管组成,二者的栅极输入分别由对方的漏极提供.本设计采用最大尺寸的去耦合电容作为基本的保持单元.通过仿真估算,单个去耦合电容的电容约为240fF.为了减小保持过程中的信号波动,取12个相同的去耦合电容并联作为采样开关的保持电容.

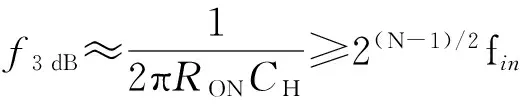

为了保证足够的驱动能力,本设计选用最大尺寸的三态门作为采样管.通过估算,由单个三态门在完全导通时的平均导通电阻约为1.5kΩ,由于本设计是一个5bit 100MS/s Flash ADC,前端采样保持电路在最大输入频率时的有效位数需要达到为8~9bit,对3dB带宽的要求如式(1),其中fin为输入频率,N为ADC位数:

(1)

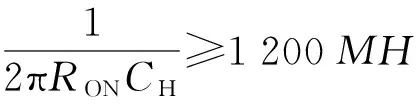

由式(1)可知,f3 dB至少为1 200MHz,由于保持电容CH=12×240fF=2.88pF,则对采样管电阻RON的要求如下:

(2)

由式子(2),采样导通电阻不能大于45Ω.为了满足这个要求,需要采用多个三态门并联组成采样阵列,以减小导通电阻,进一步增加采样保持电路的带宽,提高驱动能力.至少需要1500/45=34个三态门并联才能实现.这里的估算未考虑采样管输出处寄生电容以及比较器部分的负载电容,故而实际使用的采样单元个数需要比估算略大一些,本设计取40个相同的三态门进行并联.

2.2比较器

根据第一部分所述比较器EDR TDC的原理,针对每一对差分参考电压,需要两个VTC,满足输入控制信号分别处于参考电压对应的电平时,二者延时恰好相同.根据以上原则,VTC延时链的延时需要能够进行较为精确的调节.这里采用粗调和微调相结合的方法设计延时链.

对于延时的粗调,EDR TDC采用一对由基本延时单元串联而成的延时链,基本延时单元在延时链中的个数可调,如图10(a)所示,这种思路也简化了设计过程.对于一对预设的参考电压(Vrefp,Vrefn),两个参考电压分别对应一个延时链.假如Vrefp大于Vrefn,那么一般来说,前者对应的延时链较后者更长.也就是说,参考电压对中更大的电压对应的延时链更长.图10(b)是基本延时单元的工作原理示意图,它由一个与非门和非门串联而成,In为输入信号,而Clock则为待延时的时钟信号,In保持在较高电平变化,M2因此始终保持关断,主要由M4的导通电流大小控制Pulse的延时(这里取上升沿),In电平越高,Pulse延时越小,反之亦然.反相器是为了保证输入和输出时钟同相.

为了进一步提高EDR TDC的精度,每个延时链后可以接合适的去耦合电容来对延时进行微调.延时单元采用高阈值电压库是为了增加单元延时,并加快单元延时随输入控制电压的变化速度,使延时链延时差更易被锁存器识别.由延时链基本单元的特点可知,输入信号不能太小,这里输入信号取(900±240)mV,LSB为30mV.输入差分信号从(1.125V,0.675V),(1.11V,0.69V),…,(0.69V,1.11V),(0.675V,1.125V)均匀取值,共31组.

3 内置参考电压浮动问题

EDR TDC组成的比较器的工作受工作环境的影响.图11模拟了基本延时单元在不同corner仿真下输入控制电压对延时的影响.从图中可以看出,不管在哪种工作环境下,输入控制电压较小时,模块的延时快速降低,随着控制电压的增加,模块延时减小的速度减缓.换句话说,输入控制电压在较小的水平时,其对应延时链受工作环境的影响更加明显.在温度和电源电压较低(即ss corner下)时,模块延时随控制电压增加而降低的速度更快.而温度和电源电压较高(即ff corner下)时,这种区别变得不那么明显.

为了简化分析,图12以4 bit Flash ADC为例,从理论上表示EDR TDC在不同工作环境下的实际参考电压相对设计参考电压的偏差规律.各个EDR TDC是在标准工作条件下进行设计,那么在输入电压不变的情况下,当温度或电源电压降低时(ss corner),EDR TDC对应参考电压较小(也相对更短)的一个延时链的延时增加较另一个延时链更大,故而导致实际参考电压较预设的发生偏差,偏差的结果是各个EDR TDC的实际参考电压向0偏移(0即中间参考电压,对应Vrefp,Vrefn都为0.9V),如图12(a)所示.而对于温度或电源电压增加的情况(ff corner),同样是对应参考电压较低的延时链所受影响更大.也就是说,这个延时链在ff corner下延时降低的幅度更加明显,故而直接导致各个EDR TDC的实际参考电压向背离0的方向偏移,如图12(b)所示.

对于由于工作环境发生变化造成的参考电压偏离,一个比较简单的校正方法是调整输入信号的共模电压.因为这种参考电压偏离的方向是单向的(对于5 bit Flash ADC来说,由于前后15个EDR TDC所用模块是相同的,只不过输入控制信号做了对调,所以其对应的参考电压的偏离是对称的,这里所说的单向是指对前面一半的EDR TDC来说),将输入信号的共模电压向相应的方向调整,会一定程度上降低参考电压偏差对转换输出结果的影响.例如,在ss corner下,实际参考电压的偏离是向零靠拢的(单向来说),如果适当降低共模电压,比较器中的两个延时链延时都明显增加,但由于较长延时链包含更多延时单元,其总的延时增加相对更多,所以需要提高较长延时链的电压输入才能抵消这种由于共模电压降低引起的失调,对于参考电压为正的比较器来说,相当于增加了参考电压,对于参考电压为负的比较器则减小了参考电压,总的效果是将参考电压向背离零的方向移动,正好补偿了由于工作环境变化引起的参考电压偏差向零靠拢的偏差.当然,同时需要适当降低输入信号幅度,以符合满幅条件.ff corner下则正好相反,即适当增加共模电压,较长延时链总延时减小量更小,需要适当增加较短延时链的输入电压才能达到新的平衡,效果就是将参考电压向靠近零的方向移动,以校正参考电压背离“0”产生的误差.相应地,此时的输入信号幅度需要适当增加.

4 后仿真结果

本设计采用TSMC 65nm工艺.采样保持电路的设计好坏会决定比较器输入信号的质量,对整个ADC的运行至关重要.对采样保持电路提取寄生参数进行后仿真,图13是采样输出信号的频谱图.在100MS/s采样频率下,输入信号幅度为240mV时,采样保持电路的输出精度可达9.3bit.

整个ADC的有源部分面积为0.02mm2,其版图如图14所示.在100MS/s的采样频率下,SFDR达到37.89dB,ENOB为4.55bit.图15是在100MS/s采样频率下对数字输出信号的傅里叶分析结果.

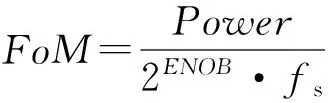

(3)

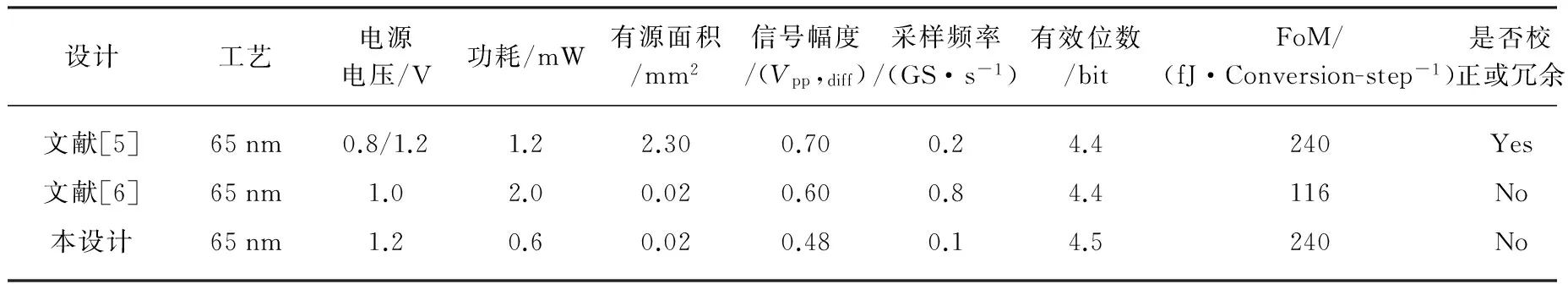

通过式子(3),此设计的FoM值约为240fJ/conversion-step.与相似的模拟实现的设计[5-6]的比较结果如表1所示.从表中可以看出,在实现相似精度的情况下,全数字Flash ADC的面积和功耗都得到了较大的改善.并且由于是全数字实现,如果工艺尺寸更小,可以预见的是,其性能可能得到更明显的提升.

表1 本设计与相关参考文献的结果比较

5 总 结

本论文提出了一种全数字Flash ADC的结构,完全使用65nm工艺的数字标准单元库,从电路层面进行验证.最终的5bit Flash ADC在100MS/s采样频率下,后仿真的SFDR达37.89dB,ENOB达4.55bit,FOM值为240fJ/conversion-step.相对于传统模数混合ADC来说,面积和功耗得到了较大的改善.

不同于传统Flash ADC先通过电阻分压产生参考电压再进行比较的方法,本文提出的全数字ADC将参考电压内置于比较器中,从而避免了使用无源器件进行参考电压的产生.内置差分参考电压延时比较器EDR TDC,由两个VTC延时链组成,VTC延时链的设计原则是当输入信号分别为相应差分电压时,延时链的延时恰好相等,由于VTC延时随输入电压单调变化的特性,这两个延时链可以对输入信号和内置的参考电压进行准确的比较.EDR TDC中延时链的设计采用基本延时单元叠加的方法,并辅以去耦合电容进行精细调节,从而在保证精度的情况下,简化比较器的设计.除比较器之外,采样保持电路也选取了数字单元库中的合适模块进行替代,从而完全实现全数字设计.由于采用内置参考电压的方法,随着工作环境的变化,内置参考电压可能产生变化,这种变化是可以预测的,可以通过调整输入共模电压实现部分校正.

[1]WATANABE T, MIZUNO T, MAKINO Y. An all-digital analog-to-digital converter with 12-μV/LSB using moving-average filtering [J].IEEEJournalofSolid-StateCircuits, 2003,38(1): 120-125.

[2]FARKHANI H, MEYMANDI-NEJAD M, Sachdev M. A fully digital ADC using a new delay element with enhanced linearity[C]∥IEEE International Symposium on Circuits and Systems. Washington, USA: IEEE Press, 2008: 2406-2409.

[3]WEAVERr S, HERSHBERG B, MOON U K. Digitally synthesized stochastic flash ADC using only standard digital cells[C]∥IEEE Symposium on VLSI Circuits. Kyoto, Japan: IEEE Press, 2011: 266-267.

[4]WEAVER S, KNIERIM D, WAZENRIED R,etal. Design Considerations for Stochastic Analog-to-Digital Conversion[C]∥IEEE International Conference on Electronics, Circuits and Systems. Marrakech, Morocco: IEEE Press, 2007: 234-237.

[5]GINSBURG B P, CHANDRAKASAN A P. Highly interleaved 5-bit, 250-MSample/s, 1.2-mW ADC with redundant channels in 65-nm CMOS [J].IEEEJournalofSolid-StateCircuits, 2008,43(12): 1264-2650.

[6]LIN Y Z, CHANG S J, LIU Y T,etal. A 5b 800MS/s 2mW asynchronous binary-search ADC in 65nm CMOS[C]∥IEEE International Solid-State Circuits Conference Digest of Technical Papers. San Francisco, USA: IEEE Press, 2009: 80-81.

A 100 MS/s 5 bit Fully Digital Flash ADC with Standard Cells

XUE Xiangyan, ZHOU Xuerong, YE Fan, REN Junyan

(StateKeyLaboratoryofASIC&System,FudanUniversity,Shanghai201203,China)

A fully digital 5bit Flash ADC is presented here. In this design, differential input analog signals are converted to time delays by a pair of voltage to time converters and the two delay signals are eventually latched to corresponding digit. A series of reference voltages are embedded in a series of voltage to time converter pairs and no reference is needed from the outside. The sample and hold circuit is also implemented with only digital cells. By using standard units from the digital library, this flash ADC is improved a lot in power, area and design complexity compared to conventional analog ADC. This chip is implemented in TSMC 65nm CMOS technology with the core area of 0.02mm2. It consumes as low as 0.6mW and achieves an SFDR of 37.89dB, ENOB of 4.55bit under sampling rate of 100MS/s.

flash ADC; fully digital ADC; embedded reference

0427-7104(2016)04-0410-08

2015-12-08

国家科技重大专项(2012ZX03001020)

薛香艳(1990—),女,硕士研究生;叶凡,男,副研究员,通讯联系人,E-mail: fanye@fudan.edu.cn.

TN 402

A