基于Verilog的DDS设计及仿真

2016-09-16四川信息职业技术学院

四川信息职业技术学院 许 斌

基于Verilog的DDS设计及仿真

四川信息职业技术学院许斌

介绍了直接数字频率合成器的组成及工作原理。采用了Verilog语言在Xilinx公司的XC3S400系列器件上实现该系统,并通过ISE和Matlab软件对设计进行联合仿真,验证设计的正确性。模块中的相位累加器使该系统具有较高的频率分辨率,可实现快速频率切换,有广泛的应用价值。

数字频率合成器;Verilog;ISE;Matlab

直接数字频率合成器(Digital Direct Synthesizer,DDS)是以数字信号处理理论为基础,从信号的幅度相位关系出发进行频率合成的。与传统的频率合成器相比,DDS具有极高的分辨率,快速的频率转换时间,很宽的相对带宽、任意波形的输出能力等优点。本文研究的是正、余弦波,方波以及三角波输出的DDS技术,这类直接数字合成技术最具价值,应用也最为广泛。

1 DDS工作原理

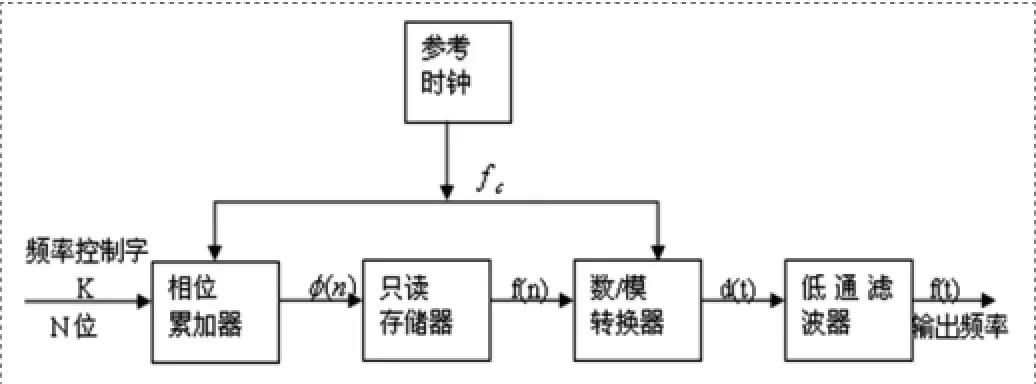

DDS主要由相位累加器、函数表ROM存储器、D/A转换器及低通滤波器组成,其基本原理如图1所示。

图1 直接数字频率合成器原理框图

波形的信号幅值以数据表的形式存储在ROM存储器中。相位累加器在时钟的作用下以频率控制字为步进进行相位累加,累加结果依次作为ROM存储器的地址,取出相应的幅值数据送D/A转换器,以产生阶梯波形,阶梯波形经低通滤波器滤波后得到相应的正弦波形。

若累加器的宽度为N位,查询表ROM的输出位数为M,则2N就相当于Trad;N位中的最低有效位相当于,即最小的相位增量;对应的相位为;完成一个周期的正弦波输出需要个参考时钟周期,所以一个参考时钟周期Tc内输出频率的周期为:。

输出频率与查询表ROM的输出位数M无关。在一定的时钟频率fc下,相位增量决定了合成信号的频率,故被称为频率控制字,习惯上用K表示。因此合成信号的频率为:。

当时钟频率fc固定时,改变频率控制字,可以改变合成信号的频率f0;当K=1时,输出频率最低即:。

2 系统设计

系统设计采用美国Xilinx公司的xc4vsx35实现频率为4M的四路波形分别为:正、余弦,方波以及三角波波形,时钟为100M。

2.1系统Verilog 源程序

输入的控制字为32bit(经计算为171798690),输出20bit四路信号分别为:正、余弦,方波以及三角波波形,以及reset,cein,wein控制输入的信号。

module DDS(datain,wein,clkin,cein,reset,cosin,sin,rect,trip);

input [31:0] datain; //频率控制字

input wein;

input clkin;

input cein;

input reset;

output [19:0] cosein; //余弦输出

output [19:0] sin; //正弦输出

output [19:0] trip; //三角波输出

output [19:0] rect; //方波输出

reg[31:0] ADD_A;

reg[31:0] ADD_B;

reg[19:0] cose_DR;

reg[19:0] sine_DR;

reg[19:0] rect_DR;

reg[19:0] trip_DR;

wire[9:0] ROM_A;

wire[19:0] cose_D;

wire[19:0] sine_D;

wire[19:0] rect_D;

wire[19:0] trip_D;

assign cose=cose_DR;

assign sine=sine_DR;

assign trip=trip_DR;

assign rect=rect_DR;

assign ROM_A=ADD_B[31:22];

…………

rom_cose cose1( .addr(ROM_A),

.clk(clk),.dout(cose_D));

rom_sine sine1(.addr(ROM_A),

.clk(clk),.dout(sine_D));

rom_rectt rect1(.addr(ROM_A),

.clk(clk),.dout(rect_D));

rom_tripp trip1(.addr(ROM_A),

.clk(clk),.dout(trip_D));

endmodule

2.2ROM定制

在编译源程序前,必须首先完成存放波形数据ROM的定制。利用MATLAB计算出波形幅度的浮点值,并量化16比特的定点波形数值。产生波形采样点数据的matlab程序如下:

x=linspace(0,2*pi,1024);

y1=cos(x); y2=sin(x);

y1=(y1+1)*32678; y2=(y2+1)*32678; %cose,sine wave

fid=fopen(‘c:/cos_coe.txt’,’wt’);

fprintf(fid,’%16.0f, ’,y1);

fclose(fid);

fid=fopen(‘c:/sin_coe.txt’,’wt’);

fprintf(fid,’%16.0f, ’,y2);

fclose(fid);

x=linspace(-3,3,1024);

y3=tripuls(x,3);

y3=32678*y3; %trip wave

fid=fopen(‘c:/tri.txt’,’wt’);

fprintf(fid,’%16.0f, ’,y3);

fclose(fid);

x4=linspace(-5,5,1024);

y4=rectpuls(x,5);

y4=32678*y4; %rect wave

fid=fopen(‘c:/rect.txt’,’wt’);

fprintf(fid,’%16.0f, ’,y4);

fclose(fid);

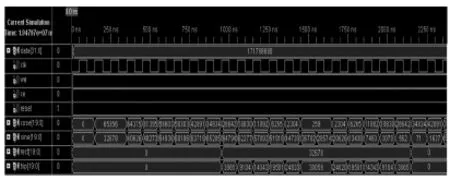

图2 时序仿真图

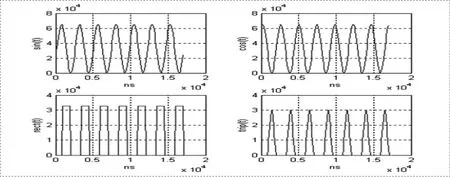

图3 Matlab波形仿真图

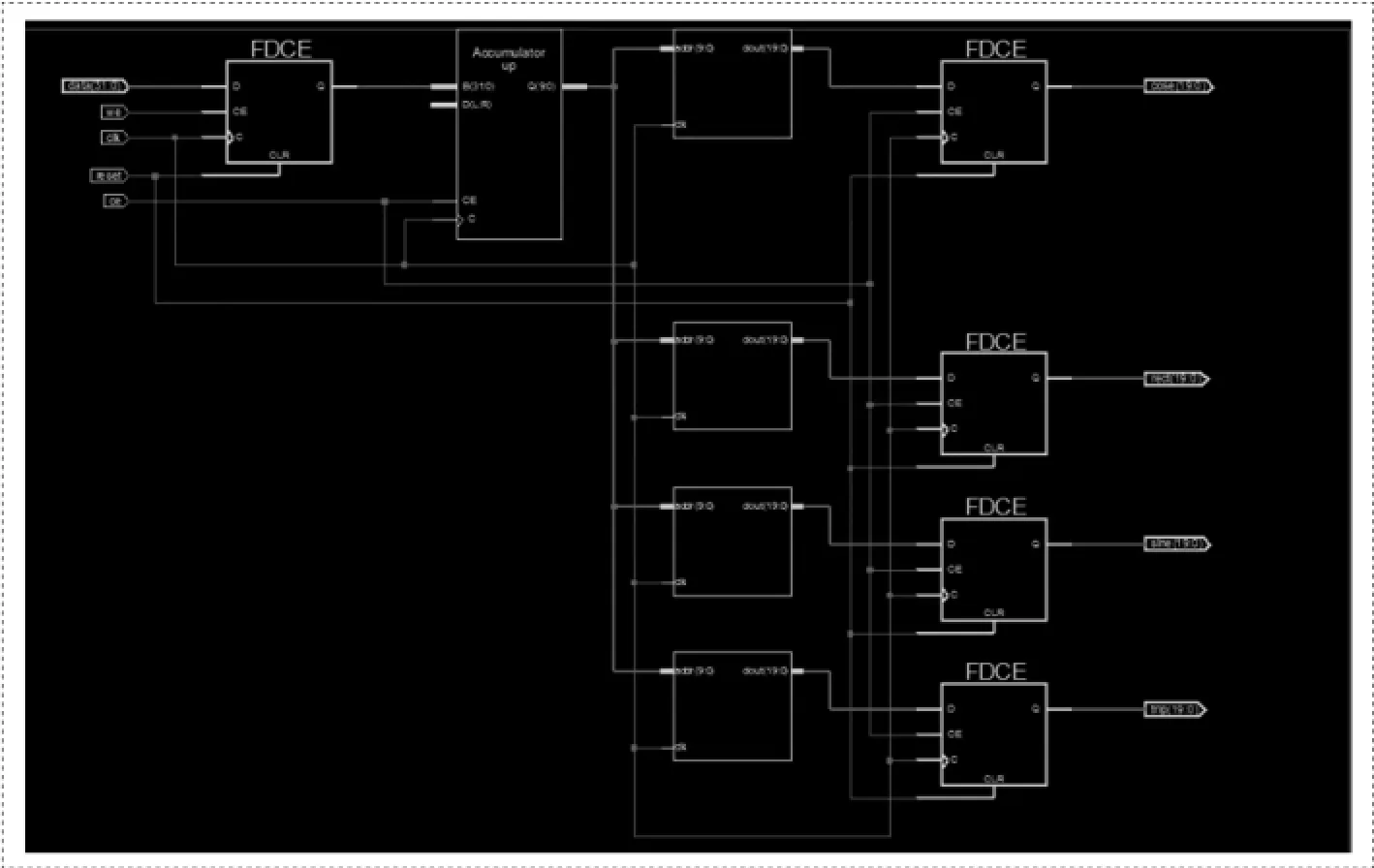

图4 DDS模块的RTL级结构图

将产生的波形数据导入到ISE中调出的单端口ROM的IP核里。

2.3ISE与Matlab联合仿真

在将设计文件加进行综合之前必须对设计进行全面充分的仿真。Xilinx公司提供的ISE软件除了具有强大的编译综合功能外,还提供一定的时序仿真功能。

编写的测试程序如下:

module test_dds;

reg [31:0] data;

reg we;

reg clk;

reg ce;

reg reset;

wire [19:0] cose;

wire [19:0] sine;

wire [19:0] rect;

wire [19:0] trip;

DDS uut (.data(data), .we(we), .clk(clk),

.ce(ce), .reset(reset), .cose(cose),

.sine(sine), .rect(rect), .trip(trip) );

initial begin

data = 0; we = 0; clk = 0; ce = 0; reset = 1;

#10

data=171798690; we=1; ce=1; reset=0;

end

always #50 clk=~clk;

endmodule由测试程序得到时序仿真图如图2所示。将时序仿真的波形数值导入Matlab中,进行波形仿真验证,得到如图3所示波形。

经过综合后,得到如图4的结构图。

3 结束语

根据仿真波形可以看到,DDS系统的输出波形平滑,满足一般系统的要求。DDS 已广泛应用于接收机本振、信号发生器、通信系统、雷达系统。未来的DDS不仅应用于传统上需要使用信号源的领域,而且必将开拓许多新的应用领域。同时利用ISE与Matlab联合仿真,在开发FPGA过程中对增强电子设计自动化功能、提高FPGA设计效率具有普遍意义。

[1]朱正伟.EDA技术及应用[M].北京:清华大学出版社,2005.

[2]张春荣等.DDS/PLL快速调频频率合成器研究[J].西部电子,1993(4):35-39.

[3]唐颖等.直接数字频率合成器的FPGA实现[A].2005年全国单片机与嵌入式系统学术交流会论文集[C].深圳,2005.

[4][美]帕尔尼卡,夏雨闻 译.VerilogHDL数字设计与综合[M].北京:电子工业出版社,2004.

[5]汤家华等.基于FPGA设计的采用DDS技术的任波形发生器[J].电子测量技术,2007,30(4):129-131.

许斌(1982—),男,陕西西安人,硕士,工程师,研究方向:通信技术。