基于FPGA和HI6110的多通道1553B MT设计及实现

2016-09-09唐建邓涵

唐建,邓涵

(1.中国兵器工业第58研究所 四川 绵阳621000;2.西南科技大学 四川 绵阳621000)

计算机技术与应用

基于FPGA和HI6110的多通道1553B MT设计及实现

唐建1,邓涵2

(1.中国兵器工业第58研究所 四川 绵阳621000;2.西南科技大学 四川 绵阳621000)

针对传统MIL-STD-1553B总线体积大、成本高的缺点,提出了一种基于FPGA和HI6110的多通道1553B MT设计方案。该方案将数据打包缓存在SDRAM中,外部设备通过PCI总线读取SDRAM中的总线监视数据,并通过PCI接口对模块进行配置,实现监视的启动、停止、RT地址设置等。文中首先介绍了HI6110芯片功能特点,然后详细描述了总线译码与转换、HI6110接口逻辑与访问仲裁、HI6110状态监控与总线切换、信息帧获取与缓存、内部功能寄存器等FPGA内部功能模块及实现方法。应用结果表明:该方案具有低成本、集成高、方便扩展等优点。

1553B;HI6110;FPGA;总线监控器

MIL-STD-1553B总线已广泛应用于航空航天等领域中,实现火力控制、雷达、导航等设备之间高可靠的互联通信[1]。1553B总线有BC、RT、MT 3种功能节点。MT(Monitor Terminal,总线监控节点)可以对总线上所有的通讯行为及数据进行监视,可有效地获得总线的工作状态,以保证总线可靠运行,是总线搭建中必不可少的功能节点。在通常的设计方案中,MT节点一般都是由BU-61580模块实现[2-3],无论是DDC还是国产兼容产品(XX-61580),该类模块体积大、成本较高的缺点。

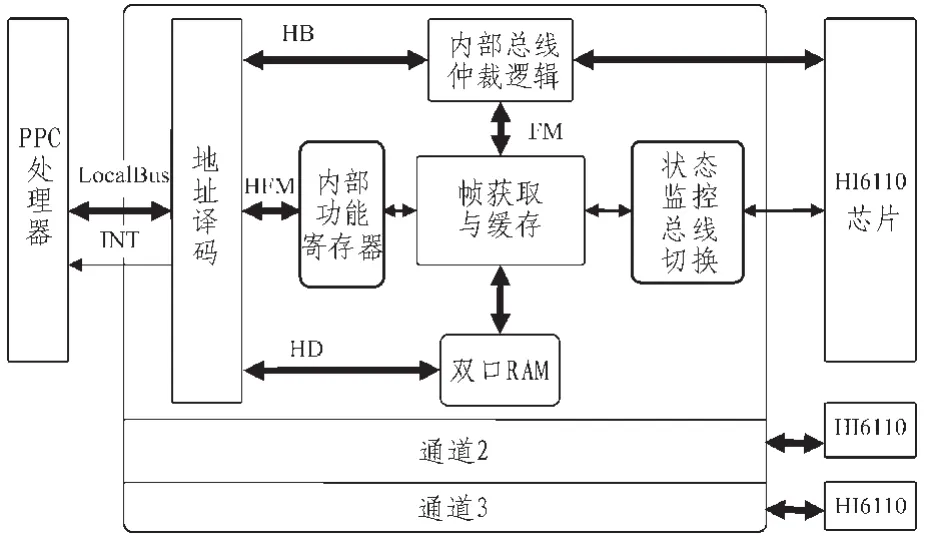

图1 3通道1553B总线MT模块

1 总线MT模块介绍

MT模块将消息帧加上时间戳、总线通道标识等数据打包缓存在SDRAM中。外部设备通过PCI总线读取SDRAM中的总线监视数据,并通过PCI接口实现监视的启动、停止、RT地址设置等模块配置。MT模块功能框图如图1所示。

HI6110完成1553B总线信号的解码、协议解析,将正确的消息帧缓存在芯片内部,并通知FPGA。FPGA根据HI6110发送的信号,进行BUS A/B切换、帧缓冲读取等操作,将消息帧、当前HI6110芯片的寄存器状态信息、时间戳等存储在内部RAM缓冲队列中,并通知处理器PPC405EP。PPC405EP读取RAM中的数据包队列,并解析数据包中的寄存器值,对消息帧进行分类、标记、错误指示等处理,最后将消息帧存储到容量更大的SDRAM中,等待PCI总线上的Master设备读取。

2 HI6110芯片特点

HI6110芯片是HOLT公司生产的一款MIL-STD-1553B协议芯片芯片。采用CMOS工艺,单3.3 V供电,典型功耗仅为1 W[4]。其基本功能为:

1)可配置为BC/RT/MT模式。

2)芯片内部集成消息缓冲器(32字);

3)双通道差分收发器,具备曼彻斯特编解码及变压器驱动功能;

4)兼容MIL-STD-1553B Notice 2和MIL-STD-1760标准。

5)有军档产品,工作温度为-55~+125℃。

与BU-61580模块相比,该芯片具有体积小、功耗低、价格便宜等的优点。但芯片唯一不足是芯片内部仅有1个消息帧缓冲器[5]。为保证信息处理的及时性,需要在HI6110外接一颗专用的处理器对芯片输出的信号及时响应,当芯片配置为MT模式且总线活动频繁时,芯片内部的消息缓冲如果不能及时处理,就会造成监控信息的丢失。本方案使用FPGA代替专用处理器,及时读取消息帧并缓存在FPGA内部RAM中,有效地避免了HI6110帧缓冲的溢出。

3 FPGA功能设计

FPGA采用 Xilinx公司的 Spartan3芯片 XC3S400-5FT256I[6],采用3.3 V和1.8 V电源供电,BGA256封装,外形尺寸为17×17 mm。

为了保证每片HI6110能被及时响应,将每一片HI6110 与FPGA单独连接,这样还可以减少总线复用逻辑,也能保证内部功能逻辑的相对独立性。FPGA内部逻辑按照模块化设计,采用VHDL/Verilog描述语言,整个设计采用自顶而下的设计方法,使用ISE+ModelSim软件进行设计与仿真[7-10]。其逻辑功能框图如图2所示。

图2 FPGA逻辑功能框图

3.1总线译码与转换

PPC405处理器带有并行局部总线LocalBus,该部分逻辑对LocalBus总线的地址进行译码分配,为每个通道分配一定的寻址空间,并且又把每个通道访问空间分为3个区域,对应着内部的3条总线,分别是对内部双口RAM缓存的访问总线HDM,对内部功能寄存器的访问总线HFM,以及对HI6110寄存器的访问总线HB。

另外,为了便于FPGA内部控制及访问仲裁,将处理器的LocalBus总线[11]进行了转换,将读写数据分离,并将总线实现为请求/应答模式。内部总线仅有 ADDR,RDATA,WDATA,BUSREQ,ACK,RW信号。

3.2HI6110接口逻辑与访问仲裁

HI6110芯片的主机接口为16位并行总线接口,使用CSn, RnW,STRn,RA[2:0]和D[15:0]信号来实现外部对HI6110功能寄存器的访问。与内部总RnW,STRn,RA[2:0]和D[15:0]信号来实现外部对HI6110功能寄存器的访问。与内部总线信号并不完全一致,而且总线读写访问的时序也有较大差异,需要进行接口访问逻辑的转换。

图3 总线译码转换时序图

图4 HI6110接口逻辑及仲裁访问时序图

另外,当HI6110监视到有效的消息帧时,FPGA逻辑中的帧获取与缓存模块需要占用HI6110的总线接口,对寄存器进行访问。因此需要将PPC处理器的访问与帧获取模块的访问进行仲裁。仲裁原则为:当访问BUSREQ同时发起时,PPC处理器访问具有优先仅,此时帧获取模块的总线请求会被挂起,直到PPC处理器的访问完成后才能被处理响应。

3.3HI6110状态监控与总线切换

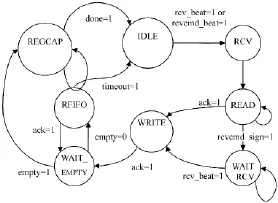

依照HI6110芯片的工作特点,当1553B总线上出现了有效的帧信号时,芯片会通过有效信号RCVA/B或RCVCMDA/B来表示是AB通道中哪个通道中有信息帧,并指出该帧信号为数据帧还是命令帧。此时,主机应根据RCV 和RCVCMD信号的状态,对HI6110的控制寄存器操作,写入正确的控制字,配置好工作通道,才能保证总线上的信号被正确的获取并解码。本设计中,主机的角色由FPGA来充当,内部采用状态机来实现。其工作状态图如图5所示。

图5 总线监视与A/B冗余切换逻辑状态图

当FPGA监控到RCV或者RCVCMD信号发生了变化,状态机由IDLE状态迁移到RCV后再转变为READ状态,发起对HI6110的读操作,将控制寄存器值读出,若当前收到的是命令帧,那么还需要迁移到WAIT_RCV状态中等待控制器发出有效的RCV信号,然后将读回的控制寄存器值的总线选择位置为正确的值,发起对HI6110控制寄存器的写操作,从而完成AB总线的切换工作。接下来,状态机判断FFEMPTY信号,该信号表示HI6110内部的帧缓存是否有数据。若不为空,则进入RFIFO状态将缓存中的数据一一读出,直到缓存被读空 (FFEMPTY=1)为止,然后状态机转变为REGCAP状态,等待done=1并回到IDLE状态,done信号为1表示当前总线活动中所有HI6110寄存器的值已经全部被读取并保存完毕。

3.4信息帧获取与缓存

在FPGA内部使用BRAM块实现了一个512x16bit的双口RAM[12],用于完成信息帧的缓存以及PPC主机与内部帧获取模块之间的数据交换。为了防止双口RAM数据访问的冲突,避免数据出错,将整个RAM分为8个数据块,形成一个环形的缓冲区,循环写入。每个块共64字,其数据格式定义如表1所示:

帧获取模块在监测到总线上的每一次总线活动后,将当前时间、当前HI6110寄存器的值以及数据FIFO中的数据按上述格式写入到数据块中,然后将FLAG标识置为0x55AA,表示一个信息已准备好,PPC处理器通过HDM总线把数据块读取后,将FLAG标识置为0x0000,表示该数据块可被再次写入。内部逻辑仍采用有限状态机来实现,状态图如图如示。

表1 环形缓存存储块数据定义与分配

图6 帧获取模块功能状态图

如图6所示,rcvint信号是工作在MT模式的HI6110芯片监测到总线上有帧时产生的,同时该信号还将内部的计数器值记录下来做为时间戳。内部逻辑在 rcvint=1后进入CHK_FLG状态,检查双口RAM中是否有可用的空闲数据块。若有的话首先将时间戳写入,然后是写入控制字CW,接下来是读取HI6110的数据FIFO,当FIFO中有数据时就读出并写入RAM中,直到当valmess=1或者error=1时,才表示总线上信息帧已完成。接下来是读取其它寄存器,包括状态寄存器、错误寄存器、信息帧寄存器、子地址寄存器等。最后是写入HI6110控制器的FIFO中数据个数,然后将FLAG置为有效。这样就完成了一个信息的处理。在对HI6110进行寄存器的读取时,有一点需要注意,读取的地址顺序最好是按照0x00,0x01,0x02,0x06进行,模拟主机软件的处理流程进行,否则可能会造成读取的寄存器不正确。

3.5内部功能寄存器

该功能模块实现了几个功能寄存器,主要用于完成时间戳的初始化,读取中断状态、复位HI6110以及对HI6110输出的信号如RCV、VALMESS、ERROR等信号变化进行统计计数,配合PPC405上的软件完成双口RAM中数据的读取,并进行一定的比对和检查。

3.6中断产生及数据传输

FPGA逻辑产生了2类中断,第1种是RCV中断,也即是当1553B总线上一旦有了数据帧时就产生中断。第2种是VALMESS或ERROR中断,这种中断是在1553B总线上一帧数据传送完毕后才产生。

图7 VALMESS及ERROR信号产生示意图

从图7可以清楚的了解到这2种中断的差异[3]。在实际应用中,响应RCV中断来操作双口RAM,以保证有空余的缓冲块供内部帧获取逻辑使用。而使用VALMESS中断来读取最新的帧数据。

3.7资源占用

使用Xilinx 9.1进行综合、布局布线,各项设置为默认值default。3通道实现占用资源如表2所示。

表2 FPGA资源占用情况

4 软件工作流程

PPC405EP处理器运行vxWorks 5.5多任务实时操作系统[13-15]。上电进入操作系统后,首先进行初始化工作,完成如下工作:

1)初始化HI6110,使其工作在MT模式下。

2)对FPGA初始化,对内部双口RAM进行初始化;

3)根据系统时间,设置时间戳;

4)初始化处理器中断控制器,挂接中断服务函数;

5)初始化PCI接口,完成PCI空间内存映射等工作;

6)创建并启动上位机命令处理任务;主要实现对上位机命令的解析,完成对总线监控的启动、停止、状态报告、时间同步等功能;

7)创建数据帧处理任务;主要实现对从双口RAM读取数据帧,对数据帧进行处理,打包,传输等功能。

初始化工作完成后,上位机会通过PCI总线与PPC405处理器交换信息,完成内部计时器的初始化,然后启动总线监控。当所监控的总线有总线活动时,FPGA会自动完成信息帧的读取并缓存在内部双口RAM中,然后向PPC处理器发起中断。中断服务程序响应中断,读取双口RAM中的数据,经过数据帧处理任务的再次处理,将数据包存放在处理器的SDRAM中,然后再通知上位机,利用PCI总线的高速性能将多个通道的1553B监控数据传输到上位机中。

5 结 论

文中实现了一个CPCI 3U的板卡,PPC405EP处理器运行频率为300 MHz,内存容量128 MB,对3路1553B总线同时进行了长时间的监控,未出现掉帧,错帧的现象。实践证明,使用FPGA和HI6110芯片组建的1553B总线MT模块,具有成本较低,体积小的特点。另外,利用FPGA内部逻辑自动完成总线切换、数据缓存等功能,还极大地降低了对处理器性能的要求。

[1]MIL-STD-1553 Designer's Guide.sixth edition[DB/OL]. ILC Data Device Corporation(DDC).1998.http://www.ddcweb.com.

[2]邓林,戎蒙恬.基于BU-61580的MIL-STD-1553B总线设计[J].信息技术,2014(2):194-197.

[3]周远林,吴忠,丑武胜.基于BU-61580的1553B总线接口设计[J].计算机工程与应用,2010,46(35):65-68.

[4]HI6110 MIL-STD-1553/MIL-STD-1760 BC/RT/MT Message Processor.Rev.S[DB/OL].HOLT Integrated Circuits Inc.2013. 09.http://www.holtic.com.

[5]陈伟,严发宝,张京,等.一种基于HI6110的1553B BM板卡设计方法[J].兵工自动化,2011,30(9):81-82.

[6]Spartan-3 FPGA Family Data Sheet.Xilinx[DB/OL].2013.7. http://www.xilinx.com.

[7]王诚,薛小刚,钟信潮.FPGA/CPLD设计工具—Xilinx ISE 5.x使用详解[M].北京:人民邮电出版社,2003.

[8]边计年,薛宠熙.用VHDL设计电子线路[M].北京:清华大学出版社,2001.

[9]MiChael D.Ciletti,等.Verilog VHDL高级数字设计[M].张雅绮,李锵等,译.北京:电子工业出版社,2005.

[10]ModelSim SE User's Manual,v10.2[DB/OL].Mentor Graphics Corporation.2013.2.http://www.mentor.com.

[11]PPC405EP PowerPC 405EP Embedded Processor Data Sheet [DB/OL].AMCC.2007.9.http://www.apm.com.

[12]LogiCORE FIFO Generator v3.2 User Guide[DB/OL].Xilinx. 2006.9.http://www.xilinx.com.

[13]朱江,王耀南,许海霞.PPC405EP在电力监测系统中的应用[J].电子设计工程,2007(10):29-33.

[14]师于杰.基于vxWorks实时系统的CompactPCI平台高可用系统研究[D].西安电子科技大学,2006.

[15]武华,刘军伟.基于VxWorks的多任务程序设计[J].计算机技术与发展,2011,21(9):88-91.

Design and implementation of multi-channel 1553B MT based on FPGA and HI6110

TANG Jian1,DENG Han2

(1.No.58 Research Institute of China Ordnance Industries,Mianyang 621000,China;2.Southwest University of Science and Technology,Mianyang 621000,China)

According to the traditional MIL-STD-1553B with large volume,high cost of shortcomings,a multi-channel 1553B MT based on FPGA and HI6110 is proposed.The data is cached in SDRAM;external devices read the data in SDRAM,and configuration the module through PCI BUS,which realize monitoring start,stop,RT ID Settings,etc.This paper first introduces the HI6110 chip function characteristics,and then describes in detail BUS decoding and transformation,HI6110 interface logic and access to the arbitration,HI6110 condition monitoring and bus switching,information acquisition and caching,internal function registers such as the FPGA function module and realization method.The application shows that the design has the advantages of low cost,high integration and easy to extend,etc.

1553B;HI6110;FPGA;Monitor Terminal(MT)

TN02

A

1674-6236(2016)16-0001-04

2016-05-08稿件编号:201605065

国家自然科学基金项目(61133016)

唐 建(1978—),男,四川射洪人,硕士,高级工程师。研究方向:嵌入式计算机应用。