基于FPGA的高斯白噪声信道模拟器设计

2016-08-31晏慧强王冬冬上海船舶电子设备研究所上海201108

晏慧强,王冬冬(上海船舶电子设备研究所,上海,201108)

设计与研发

基于FPGA的高斯白噪声信道模拟器设计

晏慧强,王冬冬

(上海船舶电子设备研究所,上海,201108)

信道模拟器在无线和水声通信领域中的应用具有非常重要的意义。对信道模拟器进行不同程序的配置,在物理上可以直接模拟不同环境下信号的传播过程。本文对高斯白噪声的理论进行了推导,给出其产生的方法和步骤,在此基础上设计出基于FPGA的信号处理流程。通过对不同SNR条件下输出信号的对比,验证了该方法的可行性。

信道模拟器;高斯白噪声;FPGA

0 引言

在真实的物理环境中,模拟信号的信道模型种类很多。在加性噪声中,高斯白噪声是最典型的一种信道环境。其中产生高斯白噪声的理论方法和数学模型非常多,本文介绍了基于Box-Muller的数学模型,利用FPGA产生高斯白噪声的方法,设计了基于高斯白噪声的信道模拟器。

1 产生高斯白噪声的理论方法

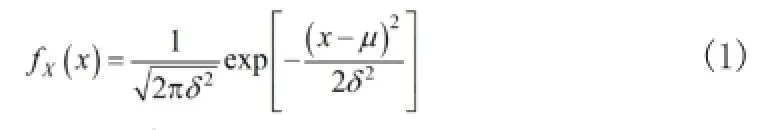

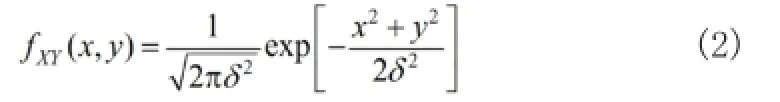

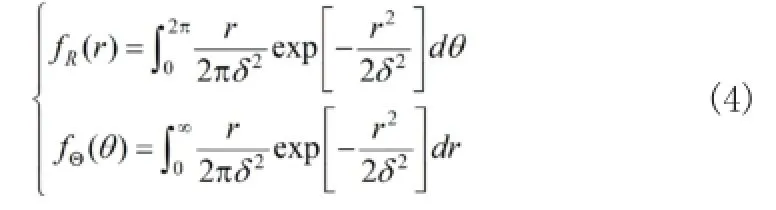

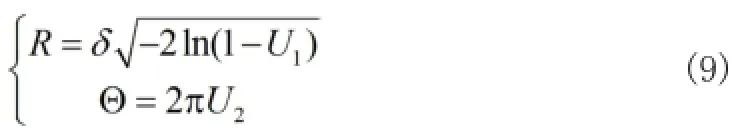

根据Box-Muller方法的推导,可以得到产生高斯白噪声的方法分为两个步骤:

1) 分别产生出在(0,1)范围内服从均匀分布的相互独立的两路序列和。

2 硬件设计

为了满足一定的灵活性,本设计把信号处理板、模拟采集板和模拟输出板进行了分离设计。

图1 A/D采集板

图2 D/A输出板

图3 信号处理板

模拟采集板把模拟信号进行量化输入到FPGA,FPGA内部通过对量化后的信号进行处理,仿造信号在信道中传播的过程。最后把处理后的信号通过D/A板输出,得到叠加噪声的模拟信号。

3 FPGA信号处理过程

FPGA的程序框图如图所示,分为信号采集驱动模块,高斯白噪声产生模块,信噪比控制模块和信号输出模块。

图4 FPGA程序框图

3.1高斯白噪声产生

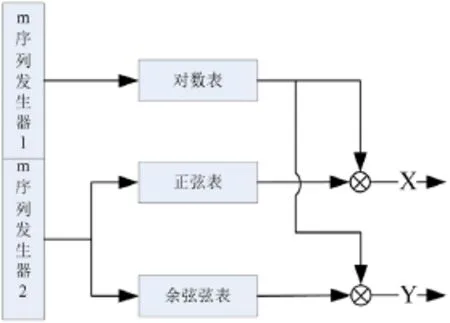

FPGA程序设计中采用m序列产生随机地址来访问在ROM中存储好的数据的地址来完成高斯白噪声的产生。高斯白噪声发生器的方框图如图5所示:

图5 高斯白噪声发生器框图

由图5可以看出,在采用Box-Muller算法产生单路的高斯白噪声的程序中有两个互相独立的作为地址发生器的m序列发生器,一个对数表和正弦表。

产生m序列的状态方程可以表示为:

图6 m序列发生器结构图

最长线性反馈移位寄存器是同级的移位寄存器序列里周期最长的一组序列,其周期长度为2n-1,其中 n为移位寄存器的级数。设置好移位寄存器的初始状态后,每经过一个时钟周期,移位寄存器都右移一位,整体输出一个m序列。

通过对所产生m序列进行分布参数、均匀性、独立性等数学特征进行分析,可以近似地认为,m序列发生器生成的序列是在(0,2n-1)范围内匀分布的,从统计学的角度上可以近似的认为是均匀分布的白噪声数据。因此可以通过利用m序列作为访问地址,访问存储好的在一定范围内的数据来生成服从均匀分布的随机数。而对需要访问的数据预先做取对数和做三角函数处理,再用m序列作为地址访问,两路输出的数据进行相乘处理,便实时生成通过Box-Muller算法产生的高斯白噪声。

3.2信噪比控制

需要对输出信号的信噪比大小进行控制。因此还需要通过一个功率比控制模块对信噪比进行控制。高斯白噪声信号经过线性系统处理后依然是高斯白噪声,只是在信号功率上有所变化,因此需要设计一个线性控制模块实现对高斯白噪声功率大小的控制。

本设计输入的信号幅度固定,即功率是固定的。假设高斯白噪声的功率为PN,噪声的方差为D2,采样后的信号功率为PS则有信噪比SNR为:

高斯白噪声由于没有直流分量,其数学期望为零,因此高斯白噪声的功率PN等同于其方差D2,从而得到信噪比SNR又可以表示为:

根据公式(13),在要求信噪比SNR为一定大小的可以得到高斯白噪声方差大小为:

通过Box-Muller算法产生的高斯白噪声其功率和方差是已知的,假设为。即产生的高斯白噪声是服从的高斯分布。根据高斯分布的性质可知,服从的高斯分布的高斯白噪声通过线性变换可以得到服从的高斯白噪声,即通过Box-Muller算法产生的高斯白噪声在其输出端应该乘以相应的系数K。信噪比SNR大小、信号功率和通过Box-Muller算法产生的高斯白噪声的方差为已知量,可以求出所需的高斯白噪声的方差,进而可以求出系数K的大小为:

因此,不同的信噪比SNR和系数K有着一一对应关系,通过调节系数K的大小可以控制信道处理板卡中的信噪比大小。

4 结论

通过示波器观测到的当参数SNR设置为10dB时信号与高斯白噪声叠加后的时域波形和频谱如图7所示:

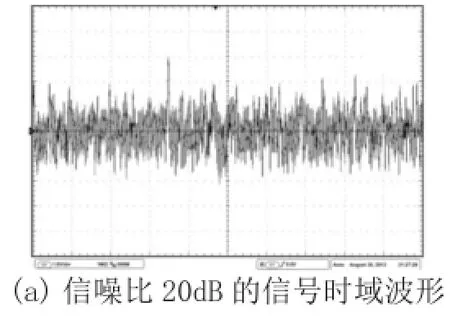

通过示波器观测到的当参数SNR设置为20dB时信号与高斯白噪声叠加后的时域波形和频谱如图8所示:

图8 信噪比为20dB的信号波形和频谱

通过对比观测,在一定带宽范围内,噪声在频域能量分布均匀具有高斯白噪声的一般特征。模拟器输出信号的SNR与实际设置的信噪比参数基本一致,验证了此方法的可行性。

[1] BOX G Muller MEA, note on the Generation of random normal deviates[J],Annals of math stat,1957:610-611

[2] 王鹏宇.二分之一连续频率切普键控及性能分析[D].哈尔滨工程大学硕士学位论文.2012.

[3] 古晓忱.一种基于FPGA的高斯随机数生成器的设计与实现[J],计算机学报2011;34(1):166-172.

[4] GHAZEL A. Design and performance analysis of a high speed AWGN communication channel emulator [C].IEEE PACRIM Conference, Victoria,B.C,2001.8:374-377.

[5] LEE D. LUK W. A hardware Gaussian noise generator using the Wallace method [J]. IEEE Transaction VLSI Systems. 2005. 13(8):911-920.

[6] Xilinx Data Sheet. Additive White Gaussian Noise(AWGN) Core v1.0. Xilinx[R]. Inc. October 2002.

[7] LEE D. Non -uniform segmentation for hardware function evaluation[C]. In Proc. Int’l Conference on Field Programmable Logic and its Application, LNCS 2778, Springer-Verlag, Lisbon, Portugal. Sep 2003:796-807.

晏慧强(1987.12-)男,汉,江西高安人,硕士,职称:助理工程师,研究方向:FPGA信号处理

Designing of White Gaussian Noise Channel Simulator Based on FPGA

Yan Huiqiang,Wang Dongdong

(ShangHai Marine Electronic Equipment Research Institute,ShangHai,201104)

The channel simulator has very important significance in the field of wireless and underwater communication.With different configuration,channel simulator can simulate signal propagation process in the physical environment directly.In this paper,the theory of Gauss white noise is derived, the method and steps are given,and the signal processing flow based on FPGA is designed.The feasibility of the proposed method is verified by comparing the output signals under different SNR conditions.

channel simulator;white gaussian noise;FPGA

图7 信噪比为10dB的信号波形和频谱

TB556

A