一种宽带小步进微波频率源设计

2016-08-29贵州航天计量测试技术研究所胡天涛谢韦春驻三五三一厂军事代表室石宏图

贵州航天计量测试技术研究所 胡天涛 刘 兴 谢韦春驻三五三一厂军事代表室 石宏图

一种宽带小步进微波频率源设计

贵州航天计量测试技术研究所胡天涛刘兴谢韦春

驻三五三一厂军事代表室石宏图

本文提出了一种简便易于实现的宽带小步进微波频率源设计方案,该方案电路结构简单,易于频率源小型化设计。本文方案基于DDS+PLL的方式实现,DDS芯片选用ADI公司生产的AD9914,利用AD9914参考时钟频率高、输出信号频率高特点,DDS输出500~900MHz信号激励锁相环,较高的鉴相频率可降低环路分频比,降低了锁相环的相噪恶化。经测试,输出信号的频率范围10~18GHz,步进100Hz,15GHz输出信号相噪-98dBc/Hz@10kHz,该方案对微波频率源DDS+PLL的设计方法和频率源小型化设计有一定借鉴意义。

微波频率源;锁相环;DDS

1.引言

微波频率源作为军用电子系统的核心,对频率稳定度、低相噪、低杂散、捷变频有了越来越高的要求,并随着技术的发展要求系统具有小型化、轻量化特点[1]。频率合成技术发展至今经历了直接频率合成,锁相环频率合成,直接数字频率合成,混合频率合成等几个阶段[2][3],如今微波频率源设计时应权衡频率范围、频率分辨率、跳频时间、相噪、杂散等指标,运用较为简便合理的混合方式实现。直接数字频率合成技术的出现极大的丰富了频率合成技术的方法,随着半导体工艺的不断进步,高性能、功能集成且封装尺寸小的 DDS 产品正快速发展,DDS具有极低的频率分辨率,极快的跳频时间,以及便于操控的数字控制接口,现今广泛应用于各类频率合成技术方案中[2][3]。DDS最大的缺点是输出信号杂散大,频率不高,而锁相环既有倍频作用又能有效抑制环路带宽外的杂波,因此DDS+PLL的频率合成方案已广泛展开使用[4]。本文根据指标要求,采用DDS作为锁相环参考信号的方式设计了一种宽带小步进微波频率源,相比已报道的文献方法,本文采用高达900MHz的DDS输出信号作为锁相环鉴相频率,有效提高了输出信号的相位噪声特性,运用一种较为简便的方案实现了综合较好的结果。

2.方案设计

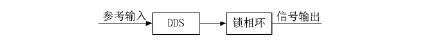

DDS+PLL的频率合成方法已广泛运用于微波频率源设计之中,它能有效提高锁相环的频率分辨率,抑制DDS输出的远端杂散,但此方法的频率切换时间由锁相环决定,牺牲了DDS的捷变频特性,并且在锁相环环路带宽内的近端杂散将会恶化20lgN[5]。DDS与锁相环的混合频率综合的方法一般有DDS直接激励锁相环[6]、DDS内插锁相环[7]、DDS作为小数分频器[8]、DDS与锁相环直接混频[9]等方案。本文基于DSS激励锁相环的方法,利用DDS输出频率分辨率高的特点实现输出信号频率的小步进要求,通过提高锁相环鉴相频率和降低环路分频比的方式改善输出信号相位噪声,且通过增加环路带宽降低跳频时间,实现了步进为100Hz的10~18GHz宽带微波信号输出。

图1 微波频率源系统方案

直接数字频率合成技术(DDS)是实现微波信号源小步进的简易方法,但DDS具有输出频率不高,输出杂散大的固有缺点[10]。理想的DDS输出除了有用信号以外,还会在输出信号f0两端产生交调分量n*f0±m*fc,除此以外还包含相位截断误差、幅度量化误差、DAC非线性等产生的杂散信号。通过采用DDS激励锁相环的方法,可以将DDS的输出信号倍频至较高频段,此外锁相环对环路带宽外的杂散信号有抑制作用,对于环路带宽内的杂散会恶化20lgN(dB)。

DDS电路采用ADI公司生产的AD9914芯片,它的参考时钟高达3.5GHz,具有较高的信号输出频率。DDS的输出信号用于激励锁相环电路,该锁相环通过一个宽带VCO实现微波信号输出,输出信号末端采用一个可变增益放大器实现功率放大和调节输出信号功率平坦度。锁相环的分频比可选取为20,则要求DDS的输出信号为500~900MHz,较高的锁相环鉴相频率和较低的环路分频比能有效抑制近端杂散和相位噪声恶化,获得较高的性能指标。AD9914输出信号近端杂散抑制<-90dBc,经过20lgN(N=20)恶化后近端杂散抑制<-63dBc。

图2 锁相环电路方案

DDS 输出信号经过锁相环后相噪变化为:

锁相环环内相位噪声:

VCO 输出的环内总相位噪声为:

该计算值是根据芯片资料估算的数据,实际由于参考时钟和电源的影响,输出信号的相噪会低于理想计算值。该方案的跳频时间由锁相环决定,根据VCO和锁相环的噪声特性可将环路带宽扩展到1MHz,从而降低变频时间。本方案提供了一种兼顾频率分辨率、杂散抑制、跳频时间、相位噪声综合设计的微波频率源设计方案,且电路结构简单,易于实现小型化设计。

3.电路设计与测试结果

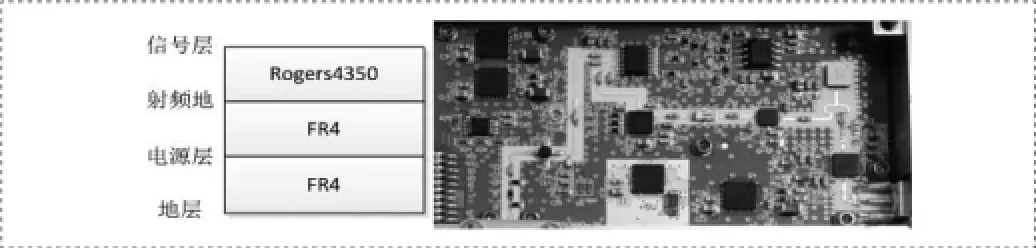

电路加工采用混合集成电路的工艺与方法,印制板采用板材Rogers4350与FR4的层叠混压技术,电路结构如图3所示。

图3 锁相环电路结构与实物图

图4 15GHz输出信号相噪测试曲线

经过测试,设置DDS的参考时钟频率fr=3.5GHz,环路分频比N=20时,相噪测试结果图4所示,15GHz输出信号相噪达到-98dBc/

Hz@10kHz,测试数据可以表明,提高锁相环鉴相频率能获得较好的相噪指标。通过实物加工与实验测试,验证了本文DDS+PLL方案的可行性,频率源的相位噪声、杂散抑制、频率分辨率等参数得到综合较优的结果,且电路结构简单、体积小。

4.结论

本文采用DDS激励锁相环的方式实现了10~18GHz的宽带小步进微波频率源设计,采用较高的鉴相频率提高了锁相环输出信号相位噪声。经过实验验证,窄带杂散抑制<-60dBc,宽带杂散抑制<-65dBc,15GHz输出信号相噪-98dBc/Hz@10kHz。得到一个相位噪声、杂散抑制、频率分辨率等参数综合较优的结果,且方案简易便于小型化设计。

[1]Manassewitsch V,何松柏,宋亚梅等.频率合成原理与设计:第三版[M].北京:电子工业出版社,2008.

[2]万天才.频率合成器技术发展动态[J].微电子学,2004(4).

[3]张广栋.C 波段频率合成器的研制[D].成都:电子科技大学,2004.

[4]张厥盛,郑继禹,万心平.锁相技术[M].西安:西安电子科技大学出版社,1991.

[5]陈科,叶建芳,马三涵.基于DDS+PLL技术频率合成器的设计与实现[J].国外电子测量技术,2010,29(4):43-47.

[6]杨 杰,杨 光,蒋国琼等.基于DDS激励PLL宽带低杂散频率合成器[J].信息与电子工程,2013(5):757-761.

[7]舒燕,李青平,孙桦.基于DDS内插PLL的设计分析[J].无线电工程,2009,39(8):45-48.

[8]张越成,要志宏,赵瑞华.DDS作为分频器在锁相环中的应用研究[J].半导体技术,2003,28(10):70-73.

[9]张子轩,彭浩.C波段宽带捷变频率综合器设计[J].电子产品世界,2014(10):29-31.

[10]Saul, P.H.; Mudd, M.S.J.” A direct digital synthesizer with 100-MHz output capability” Solid-State Circuits, IEEE Journal of Volume:23.

胡天涛,男,硕士研究生,毕业于电子科技大学,现就职于贵州航天计量测试技术研究所,现主要从事微波、毫米波电路与系统设计。