集成电路可测试性设计与验证

2016-08-11吴立斌

吴立斌

(中国人民解放军装甲兵工程学院,北京 100072)

集成电路可测试性设计与验证

吴立斌

(中国人民解放军装甲兵工程学院,北京 100072)

文章介绍了集成电路系统芯片(SoC)以及IP核相关理论知识,对DFT集成电路可测试性设计进行了概述,给出了几种常用IC产品的测试方法,并对以后DFT可测试性设计的发展进行了论述;提出了一种基于图像处理的多级滤波芯片DFT测试进行分析,给出了DFT Compiler软件实验验证报告,有效地提高了测试覆盖率。

集成电路;DFT;边界扫描测试;设计验证

随着集成电路集成度越来越高,智能化程度也越来越高,集成系统逐渐由板上系统过渡到片上系统,即系统芯片(SoC)。SoC能够集成模拟电路、逻辑电路、存储器、模数混合电路等,系统体积越来越小,延迟性得到改善,大大减少了生产成本,提高了系统的稳定性。近些年集成电路系统多采用嵌入式核设计,也称为IP核,IP核设计理念是基于库资源的IP复用,成为IC电路系统设计的主流,但是由于系统设计的复杂性,也给集成电路的可测试性提出了更高的要求。基于此,本文对于IP电路的一种可测试性设计进行研究并对三态门电路进行可测试性设计验证。定位出产品的设计缺陷,提高检测率,节省高精度产品设计的生产成本。

1 系统芯片可测试性设计概念

1.1基本概念

Design For Test(DFT)在世界各国集成电路设计及产品生产过程中是必不可少的环节。根据可测试性大纲,DFT定义为对产品状态进行确认,状态包括可完好性、损坏性、缺陷性。对于其内部缺陷进行的有效隔离的设计性特性而言,为了提高IC可测试性目的,在产品设计过程中进行可测试性设计即为design for testability。IC产品的可测试性主要包括采用外部激励获取的缺陷性特征,成为可控性;将这种缺陷性特征传递到输出端口进行表现的特性,称为可观测性。通常行业生产中,对于合格的芯片一般需要经过晶圆片测试,就是对成品晶圆片进行性能测试和产品质量测试。晶圆片测试是生产前的严格测试,属于设计测试,只有通过严格的设计性测试的裸片,才能进行划分、封装;产品测试是对封装后的产品成品测试。通常定义为产品的开发阶段考虑的可测试性,即为DFT问题[1]。20世纪80年代中期,美国军方颁发MIL-STD-2165A《系统和设备的可测性大纲》,大纲规定了可测试性分析、设计及验证的要求、实施方法等内容。从此DFT成为一项专门的学科,在世界范围内开始研究并推广。

1.2可测试性设计的常用方法

可测试性设计在集成电路设计完成后为便于测试,通过增加一定激励信号控制和观察电路中的输出信号,来确定电路工作过程有无缺陷,从而降低测试的难度。这种增加电路节点的故障检测的方法,有利于提高集成电路的可测试性。在这个过程中,主要通过结构设计来完成集成电路的功能设计,以此来提高集成电路内部节点的可观测性和可控制性,从而实现可测试性设计。可测试性设计主要包括功能点测试、扫描测试、内建自测试3种测试方法,从而经济高效地完成IC芯片的生产测试过程。

(1)功能点测试。IC电路芯片成品生产后的一种测试,主要用于某些单元的测试功能点测试。其具体可运用分块法进行机械分割以及跳线、选通门、增加测试点、功能块、总线结构等方法。机械分割比较原始,将集成块直接分割为多块,再进行测试;跳线则是增加I/O输入输出测试端口;选通门则是在跳线基础上,在设计过程实现I/O端口的选通功能测试。增加测试点则是在电路难测试节点引出进行测试,该引出点可以作为系统测试输入,也可以作为系统测试输出,提高了电路的测试可控性和可观察性,是提高电路可测试性最直接的方法。但是,这种方法由于引脚数目有限,引入的测试点有限,限制了测试的灵活性。功能块和总线结构测试都是把电路进行功能块划分,然后利用总线连接,对各功能块进行测试,其缺陷性在于无法对总线故障进行检测[2]。

功能点测试技术增加了附加I/O端口、联线,提高了系统面积开销,且对于成品IC电路的测试筛选无法自动生成,可作为电路产品辅助分析的一种测试方法。

(2)扫描测试。扫描测试主要包括全扫描、边界扫描、区域功能扫描3种方法。这种测试通过将IC电路设计中的逻辑电路中任一节点的状态进行测试定位。改变可测试性设计逻辑电路的整体性,使其具有可扫描性,测试数据从芯片端口经移位寄存器等组成的数据通路串行移动,并在数据输出端对数据进行验证分析,以此来提高电路内部节点的可控制性和可观察性,达到测试芯片内部节点的目的。边界扫描总体结构如图1所示。

(3)内建自测试。Built-In-Self-Test(BIST)内建自测试主要针对数字电路进行测试。其检测原理是先将测试信号发生器产生的测试序列叠加在被测电路中,再通过输出响应分析器对输出数字信号序列进行检测分析,从而检测电路是否有缺陷或缺陷在哪里。内建测试有伪穷举测试、伪随机测试等测试、ROM比较逻辑法等方法。BIST测试不需要很多连接/次序,存储量较少,不存在ATE存储限制,能够实现全速测试;测试成本低廉,可以多单元并行测试;提高和简化元件维护;因为内部测试电路运行于工作速度,可以减少测试时间。

图1 边界扫描标准的总体结构

1.3系统芯片可测试性设计发展

技术日益更新,IC产品开发周期更短,系统芯片的规模更大,系统结构越来越复杂,芯片的制造厂家更多,造成了系统芯片测试的巨大困难。巨大的系统芯片,包含有大量的嵌入式内核,测试向量日益增加,测试时间、测试开销也趋于增大。DFT测试技术未来发展主要表现为以下几点[3]。

(1)随着IC制造工艺的不断涌现,尤其是深亚微米、纳米、超导纳米等工艺的应用,IC电路越来越小,IC电路失效故障会出现更多新的模型,电信号迁移、温度漂移、串扰、电磁干扰、信号完整性等电路设计问题更突出。

(2)设计规模不断扩大,要求测试向量数目急剧增加,测试向量的压缩方法要求更甚,研究硬件电路实现测试向量的编码和解码,并尽可能地减少硬件开销以及电路设计的功能影响是未来DET测试技术的发展方向。

(3)芯片系统运行速度不断升级,功耗越来越低,测试功耗如何控制,数字信号以及数/模混合系统的可测试性设计表现出更加复杂的叠加模拟特性,因此,测试仪设计精准度更高,需要进行实速测试,避免测试功耗大发热烧毁芯片系统。

(4)由于IC核心技术、上市时间、成本控制等因素影响,集成电路IP核提供商开启知识技术保护措施。这给集成测试设计带来技术难题,影响了测试的质量;另外,为了节约时间和成本,需要对各IP核进行调度,实行并行测试,同时需要建立数学模型,减少测试发热复杂度。

2 基于边界扫描测试多级滤波芯片DFT设计

基于边界扫描测试的IEEE Std 1149.6标准采用对跳变敏感的技术,采用迟滞比较器,图2中给出了最初的信号,一个延迟信号和迟滞比较器的输出结果。输出信号是原始信号的准确重建,延迟了输入波形通过迟滞门限的时间。输出波形已经变为标准逻辑电平。

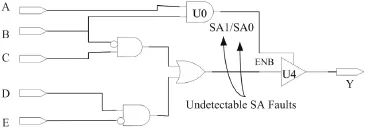

对于多级滤波芯片的三态门测试,如图3所示,存在不可测试故障,增加一个总线保持单元,需要2个连续的测试向量实现上图中所示的SA0故障诊断。第一个测试向量将一个初始数据打入总线数据保持单元,用来覆盖第二个测试向量在输出端产生的高阻值Z。在图4中,用第一个测试向量110将Bus Keeper置为弱1,当第二个测试向量施加到输入端时,如果上述SA0故障存在,则由Bus Keeper提供的1作为输出,如果电路不存在此故障,则输出0电平。采用这种方法的缺陷是ATPG的数量相应增加,故障覆盖率偏低。

图2 一个伴有未知电压偏移的直流耦合的延迟自参考重建

图3 多级滤波芯片的三态门测试

图4 采用总线保持单元提高电路的故障覆盖率

3 测试验证

本文采用Synopsys公司的DFT Compiler软件进行实验验证。应用于图像处理的多级滤波芯片规模较小,内部有2554个触发器,4个“位数为16、深度为128”RAM的IP核。

该芯片采用的硬核内部有64个三态门,其中有4个时序向量和231个组合向量。

4 结语

文章介绍了用于图像处理的可测试性设计IP核的多级滤波芯片。该IC芯片电路可以作为辅助测试的模块嵌入到电路中,提高测试的覆盖率。通过边界扫描测试的IEEE Std 1149.6标准串口通信技术向IP发送控制信号,增加一个总线保持单元,需要两个连续的测试向量对电路测试,提高了测试覆盖率。

[1]冯泽民.一种用于数模混合电路的可测试性设计IP核[J].固体电子学研究与进展,2014(6):550-554. [2]陈然.外场可更换模块体系下测试性验证试验发展研究[J].计算机测量与控制,2016(2):1-5.

[3]王厚军.可测性设计技术的回顾与发展综述[J].中国科技论文在线,2008(1):52-57.

Design and Verification of Integrated Circuit Testability

Wu Libin

(Chinese People's Liberation Army, the Academy of Armored Forces Engineering, Beijing 100072, China)

This paper introduces the integrated circuit system on chip (SOC) and IP related theoretical knowledge, onthe DFT integrated circuit can be design for testability are outlined, gives several commonly used IC product test methods and of DFT can be the development of design for testability are discussed; puts forward a test based on the analysis of image processing of multilevel filter chip DFT, given the DFT compiler software for experimental validation report, effectively improves the test coverage.

integrated circuit; DFT; boundary scan test; design verification

吴立斌(1991-),男,安徽宿松,本科;研究方向:控制科学与工程。