基于DE0的测温系统的设计*

2016-08-10刘昌华

聂 云 刘昌华 邹 翰 王 慧

(武汉轻工大学数学与计算机学院 武汉 430023)

基于DE0的测温系统的设计*

聂云刘昌华邹翰王慧

(武汉轻工大学数学与计算机学院武汉430023)

摘要使用DE0开发板以及一个温度传感器DS18B20,来实现温度的采集与显示。介绍了温度传感器DS18B20的接口原理和操作时序,阐述了系统组成的硬件电路和软件设计。使用EP3C16F484C6作为主控芯片,使用Verilog HDL硬件描述语言设计状态机,根据单总线协议完成FPGA对DS18B20温度传感器的复位、数据读、数据写的操作,完成测量温度的功能。并将测量的二进制温度数据转换为BCD码,通过数码管显示。利用Quartus II 13.0软件自带的逻辑分析仪Signal Tap II进行仿真。

关键词DE0开发板; DS18B20传感器; 单总线协议; Verilog HDL

Class NumberTP391

1引言

温度控制已被广泛应用于生活各个领域,如在军工、食品、农业生产等方面。在这些领域对温度的要求很高,如果温度超出规定范围,会造成很多不利于生产的影响。DS18B20是美国DALLAS半导体公司生产的1-Wire系列的高精度数字温度传感器,温度测量范围为-55℃~+125℃,可设置9位~12位A/D转换精度,最小的分辨率为0.0625℃。单总线协议是Dallas公司的专利,与其他通用的串行数据通信方式不同,它只用一根信号线,传输时钟和数据,传输数据时是双向口。具有很多优点,例如节省接口资源、便于在总线上扩展多个传感器等。结合FPGA器件强大的并行处理能力、功耗低等优点,所以选择FPGA与DS18B20结合来实现该测温系统[1]。

本设计采用Altera公司的Cyclone III系列芯片EP3C16F484C6和DALLAS公司的DS18B20[9]组成的测温系统,DS18B20采集被测物体的温度,FPGA通过读取单总线的数据,最后把温度数据传送给数码管显示。该测温系统硬件电路简单,应用范围广泛,易于扩展,有广阔的应用前景。

2数字温度传感器DS18B20

2.1DS18B20的内部结构

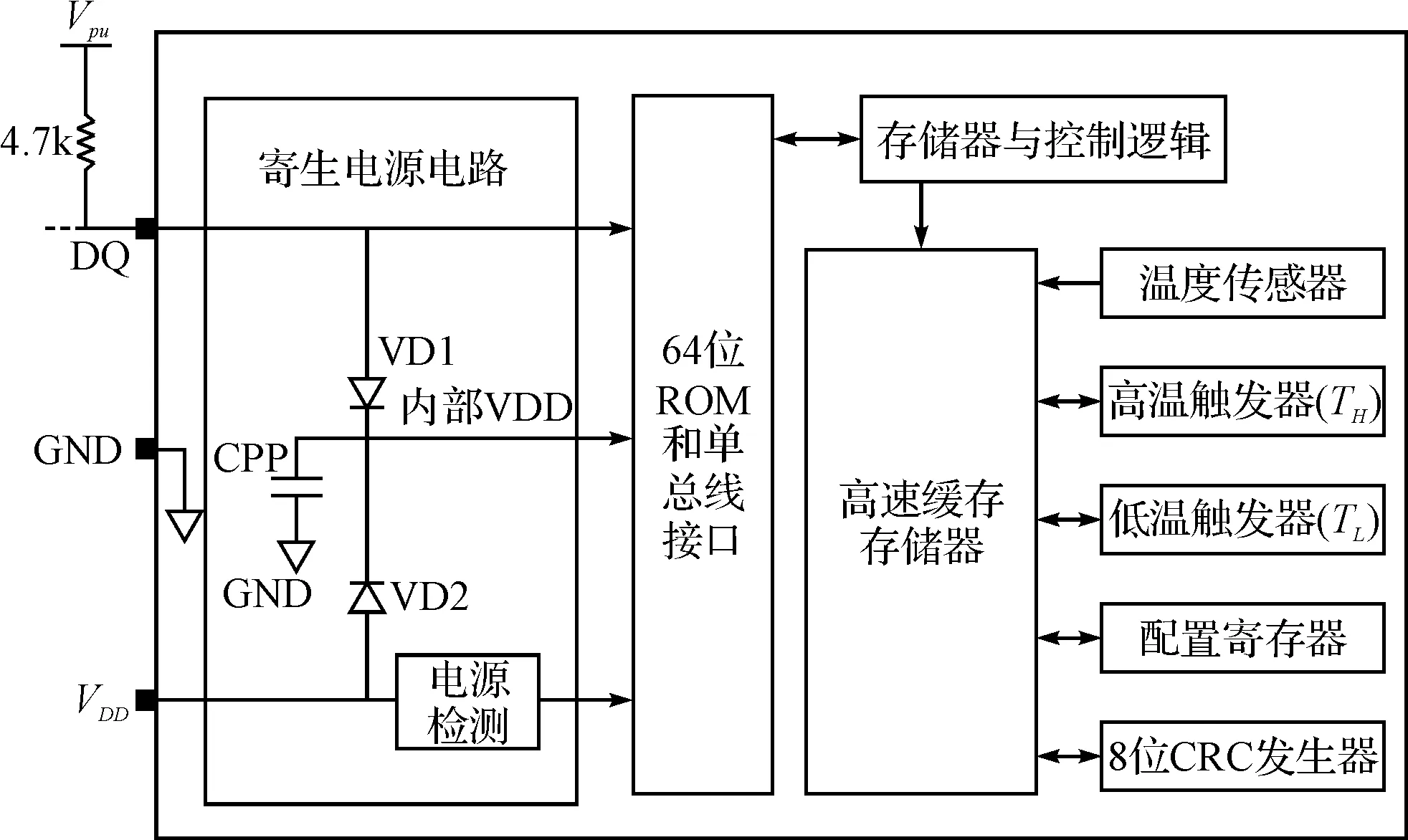

DS18B20内部结构如图1,主要由下面几个部分组成:64位ROM、温度传感器、非挥发的温度报警器TH(高温)和TL(低温)、配置寄存器、暂存寄存器(SCRATCHPAD)、存储器与控制逻辑。DQ为温度传感器与外部器件传输数据与时钟的引脚。其中64位ROM中有64位序列号(8位产品家族编号、48位ID号、8位CRC),该序列号是出厂前刻好的,而且每个DS18B20的序列号是不同的。

图1 DS18B20内部结构图

DS18B20加电后,处在空闲状态。温度传感器的操作分为启动温度转换和读取温度两个过程。在启动温度转换阶段,当DE0向其发出Convert T[44H]命令后开始模数转换,转换完后,温度数据以二进制补码存储在温度寄存器中,温度寄存器格式如图2。

图2 温度寄存器格式

LS byte存储温度的低8位,MS byte存储温度的高8位,高8位中的前5位都为符号位,说明温度的正负状态,当温度为正值时S为0,温度为负值时S为1[2]。

表1为DS18B20温度/数据的对应关系表,该表给出的温度范围为-55℃~125℃。DS18B20在上电复位时,温度寄存器的初始值是85℃。

2.2DS18B20的操作时序

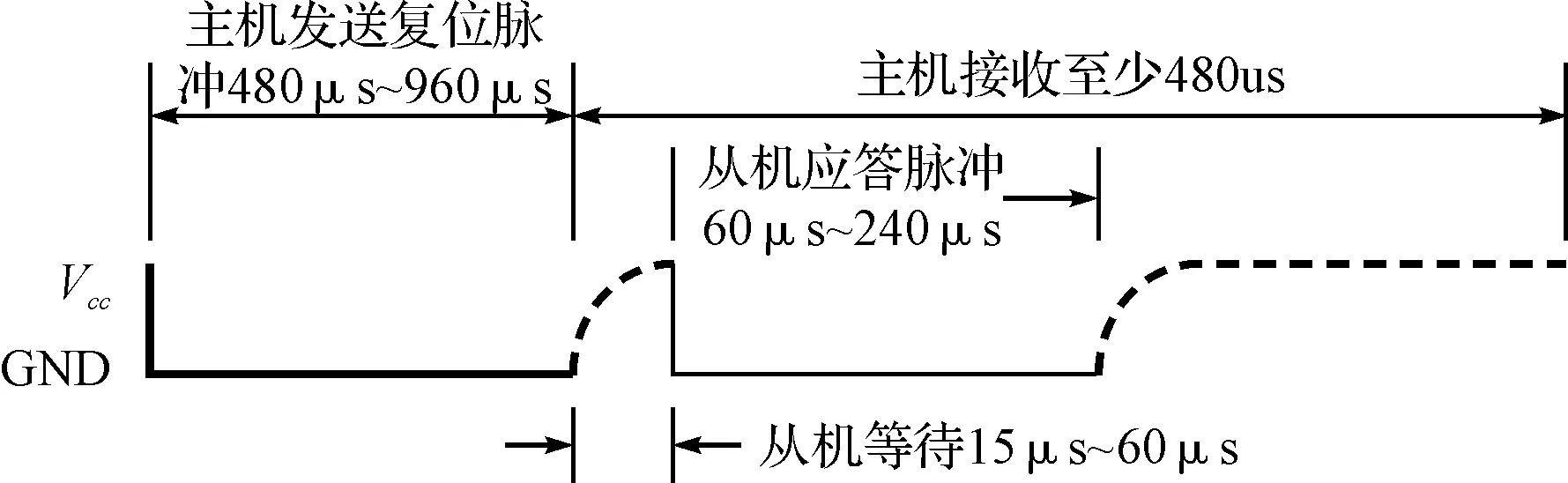

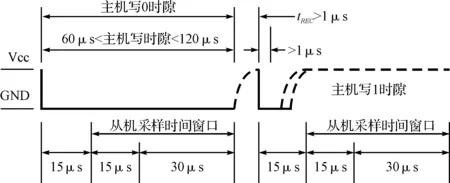

图3为DS18B20操作的初始化时序,图4为写操作时序,图5为读操作时序。单总线协议器件严格按照时序进行操作。本文用Verilog HDL硬件描述语言[3]编写有限状态机程序,由主控芯片发出同步信号,发送命令和数据都是以bit为单位,而且是以低位在前高位在后的形式。

表1 DS18B20温度/数据的关系

图3 传感器初始化时序

FPGA在开始时刻发送一复位脉冲(最短为480μs的低电平信号),经过480μs~960μs的低电平之后释放总线并进入接收状态[4],DS18B20在检测到总线的上升沿之后,等待15μs~60μs,接着DS18B20发出响应脉冲(低电平持续60μs~240μs),如图3中黑粗线所示。

当写入命令到DS18B20时,DE0将数据总线从高电平拉至低电平后,就产生写时间隙。如图4,拉低总线15μs内应将数据位送到总线上[5]。DS18B20在开始时刻后15μs~60μs间对总线进行采样,若采样的电平为低电平,则写入的位是0;若为高电平,则写入的位是1。连续写2位间的间隙应大于1μs,每写一位的时隙至少为60μs。

图4 传感器写时

当从DS18B20读取数据时,DE0把数据总线从高电平拉至低电平并保持1μs,然后释放总线。来自DS18B20 的输出数据在下降沿后15μs有效。在读取数据结束时I/O引脚应拉回到高电平,没读取一位的时隙至少为60μs,如图5。

图5 传感器读时

3DE0与DS18B20的连接

DS18B20支持寄生电源供电,在总线为高电平时,DS18B20的内部电容会总线上获得电荷;在总线为低电平,内部电容可以供电。但在温度变换期间,I/O引脚电流较大,如果在该I/O引脚上保持高电平,会对FPGA芯片引脚造成很大压力。所以使用VCC引脚接外部电源,DS18B20的数据线与DE0开发板的GPIO 0口的GPIO0_D0口连接,如图6所示[6]。

图6 DS18B20与DE0的连接电路图

4软件设计

根据系统的要求,将软件设计分为三个模块,包括DS18B20的驱动模块、数码管显示模块、温度显示顶层模块。利用Verilog HDL语言[7]在Quartus II13.0开发平台上完成程序设计。其RTL图如图7所示。

图7 测温系统的RTL电路图

单总线协议通信器件,其硬件电路简单,相对的软件设计过程比较复杂。 通过对DS18B20功能的分析可知,DE0与DS18B20组成的测温系统软件流程图如图8所示。

图8 测温程序流程图

软件设计过程分为启动温度转换、读取温度、显示温度三个过程。前面两个过程都是从复位DS18B20开始。由于单总线协议对时序要求非常严格,分频出1Mhz的频率为了方便计数器计数。系统只用到一个温度传感器,SKIP ROM为跳过ROM命令,不需要读取64位序列号来确定从机地址。

4.1DS18B20的驱动模块

本设计使用的目标芯片是EP3C16F484C6[8],全部软件功能在Quartus II13.0平台上实现,使用了Verilog HDL语言编写各个模块的程序。DS18B20的驱动模块电路图符号如图9所示, 该模块有四个端口:clk是由开发板的50 MHz系统时钟分频得到的1MHz的时钟信号;rst_n是低电平复位信号线;one_wire是与DS18B20的双向接口;temperature[15…0]是16位的温度数值输出。DS18B20的驱动模块利用状态机将DS18B20的单总线协议描述出来,完成了初始化时序、读时序、写时序。

图9 DS18B20的驱动模块

以下是对采集的温度数据进行处理的Verilog代码,形成一定的线性关系。

Wire [15:0] t_buff = temperature_buff& 16'h07FF;

assign temperature[3:0] = (t_buff[3:0] * 10) ≫ 4;

// 小数点后一位

assign temperature[7:4] = (t_buff[7:4] >= 10) ? (t_buff[7:4] - 10) : t_buff[7:4]; // 个位

assign temperature[11:8] = (t_buff[7:4] >= 10) ? (t_buff[11:8] + 1) : t_buff[11:8]; //十位

assign temperature[15:12] = temperature_buff[12] ? 1 : 0; // 正负位

4.2数码管显示模块

该系统采用四位数码管来显示采集的温度值。DS18B20采集到温度数据是二进制数据,一共有16位。高5位共同作为符号位,用S表示,当温度为正时S为0,温度为负值时S为1;低11位是数据位,与符号位组成12位的温度数据。第一位数码管表示温度的正负状态,如果温度为正,则数码管显示熄灭状态,如果温度为负,则数码管显示’-’。第二位数码管表示温度的十位的值,第三位数码管表示温度的个位的值,该数码管的dp位为小数点,为常亮状态,第四位数码管表示温度的小数点位的值。根据系统设计的要求,分别设计了三个不同的数码管译码模块。第二位和第四位数码管调用seg7x8_drive译码电路,第三位数码管调用seg7x8_drive1译码电路,第一位数码管调用seg7x8_drive2译码电路。三个数码管显示模块如下图10所示。

4.3温度显示顶层模块

该模块为系统设计的顶层模块,在该模块中定义了与外部硬件连接的输入输出引脚,依次调用DS18B20驱动模块和数码管显示模块,实现16位带符号的温度值在数码管上显示。该模块的电路符号如图10。

图10 数码管显示模块

该模块中定义的输入输出引脚如下:

module DS18B20_SEG7(

inputCLOCK_50,// 板载50MHz时钟

inputQ_KEY,

inoutDS18B20,

inputSW,

output[6:0]HEX3_D,

output[6:0]HEX2_D,

output[7:0]HEX1_D,

output[6:0]HEX0_D);

图11 温度显示顶层模块

5调试与结果分析

Signal Tap II[10]是Quartus II13.0软件自带嵌入式逻辑分析仪,该分析仪用于调试FPGA,并进行片内信号分析的一个重要工具,本设计在进行温度数据采样和捕获信号时,通过JTAG端口进行数据传输,采用Signal Tap II逻辑分析仪进行数据处理,验证该系统设计的逻辑功能是否正确。

逻辑分析仪的基本步骤如下:

1) 打开Signal Tap Ⅱ编辑窗;

2) 调入待测信号;

3) 相关参数设置。首先设置采样时钟;其次设置采样深度;最后设置触发条件;

4) 下载、启动并查看数据。

经过上述步骤,程序下载到DE0后,用Signal Tap II抓取各个端口的数据并观察其结果如图12所示。

通过对各部分软件的设计,用Quartus II 13.0软件进行Verilog HDL语言的程序编译,调试结果显示没有错误后,就可以将此程序烧写进目标芯片里面,数码管显示如图12所示结果,Signal Tap II的仿真结果显示HEX3_D:1111111b,HEX2_D:1111001b,HEX1_D:01111001b,HEX0_D:0110000b,经数码管译码后应该显示:11.3℃,由于是正温度,HEX0_D为熄灭状态,与数码管的显示结果一样。通过Signal Tap II的仿真和在数码管显示的结果可以验证,该测温系统实现了预期的目的。

图12 Signal Tap II调试图

6结语

本文用DE0开发板搭建硬件开发平台,使用EP3C16F484C6 为主控芯片,DS18B20以单总线的方式与主控芯片连接,组成测温系统。从DS18B20的操作步骤和时序出发,用Verilog HDL硬件描述语言编写有限状态机程序[11],实现对DS18B20的控制。该接口实现了DS18B20与DE0的通信,并可以将该接口做成IP核,嵌入到其它温度控制系统中。实验结果表明,该系统可以稳定的运行。该测温系统还可以灵活地添加多个温度传感器,实现多路温度测量系统,实时地感知不同环境下的温度,实现多路传感器数据的信息融合,该系统实时性高,可靠性高,有广阔的应用前景。

参 考 文 献

[1] 郑丽娟,王梅,王宁.基于FPGA的多路温度采集系统设计[J].通信电源技术,2015,32(2):47-49.

[2] 王春玲,王美红.基于DS18B20的小环境测温控制的FPGA实现[J].泰山学院学报,2014,36(3):10-16.

[3] 胡同花,周维龙.温室大棚多点温度采集系统的设计与实现[J].电子设计工程,2014,22(13):87-90.

[4] 于京,吕殿基.基于FPGA的测温系统的设计[J].内蒙古大学学报,2011,42(5):576-580.

[5] 仁爱锋,罗丰.基于FPGA的嵌入式系统的设计[M].西安:西安电子科技大学出版社,2014:30-58.

[6] 刘昌华.EDA技术与应用—基于QUARTUS II与VHDL[M].北京:北京航空航天大学出版社,2010:47-60.

[7] 夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008:166-175.

[8] Altera公司.DE0用户手册,2010.

[9] DALLAS公司.DS18B20数据手册.

[10] 潘松,黄继业.EDA技术实用教程[M].北京:科学出版社,2010:110-127.

[11] 王晓磊,李宏生.基于有限状态机的数字温度传感器控制系统设计[J].舰船电子工程,2010:30(12):182-185.

收稿日期:2016年1月7日,修回日期:2016年2月19日

基金项目:国家科技计划项目(863计划)(编号:2013AA100302);武汉轻工大学2013研究生创新基金(编号:2013cx007)资助。

作者简介:聂云,女,硕士研究生,研究方向:嵌入式FPGA设计。刘昌华,男,副教授,硕士生导师,研究方向:计算机网络及应用、嵌入式FPGA设计。邹翰,男,硕士研究生,研究方向:嵌入式技术。王慧,女,硕士研究生,研究方向:软件开发。

中图分类号TP391

DOI:10.3969/j.issn.1672-9730.2016.07.033

Design of Temperature Measurement System Based on DE0

NIE YunLIU ChanghuaZOU HanWANG Hui

(School of Mathematics and Computer Science, Wuhan Polytechnic University, Wuhan430023)

AbstractA DE0 development board and the temperature sensor DS18B20 is used to achieve the collection and display of temperature. It introduces the interface principle and operation sequence of the sensor and demonstrates the hardware circuit system composition and software design. By means of EP3C16F484C6 as the master chip, Verilog HDL hardware is used to describe language design state machine, which complete the FPGA’s operation about resetting, data-reading and data-writing on the DS18B20 temperature sensor according to the 1-wire protocol to finish temperature measurements. It also converts measured the binary temperature data into BCD code through digital tube display and use thes logic analyzer Signal Tap II of the Quartus II 13.0 software to simulate.

Key WordsDE0 development board, DS18B20 sensor, 1-wire protocol, Verilog HDL