基于锁相环与FPGA的频谱仪的设计与制作

2016-08-09张学梁王诏君张凯刘雨晴

张学梁 王诏君 张凯 刘雨晴

【摘要】 提出了一种基于新的锁相环与FPGA制作频谱仪的方法。采用扫频外差法,以单片机STM32F103VET6为控制核心,结合高速可编程逻辑器件FPGA,采用锁相环技术产生本振信号,本振信号和输入信号混频滤波输出中频信号,采用了一次下混频、滤波,经过高速AD采样之后由FPGA实现FFT算法输出频谱,最后由单片机液晶屏显示出频谱。

【关键词】 扫频外差式频谱仪 锁相环 FPGA 单片机控制显示

理论分析:

电路实现:

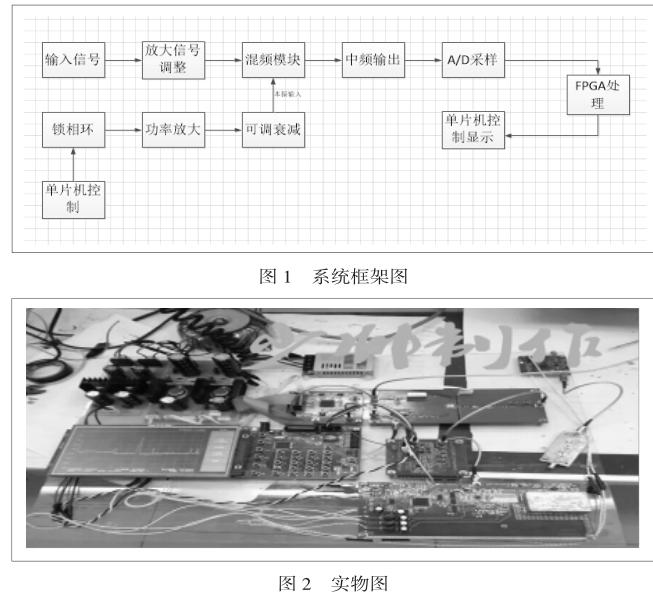

(1)系统框图:

(2)锁相环电路:ADF4351集成芯片内部集成鉴频器和压控振荡器,结合外部环路滤波器和外部参考频率输入,结合外部电路即可实现程序控制锁相环功能。

(3)中频信号产生:输入信号经过放大输入混频器,和锁相环产生的本振信号混频经过带通滤波器后输出中频信号,经过两级放大信号调理提供AD转换模块的输入。

(4)AD采样模块采用12位AD采样芯片LTC2227CUH,采样速率可以达到40MSPS,有很高的分辨率,为FPGA模块提供信号输入。A/D采样电路对下混频后的信号进行采样。

(5)FPGA电路:采用CycloneIV 系列EP4CE10芯片,实现数字信号处理,进行滤波操作,实现FFT运算。共采集转化为512个点,提供给单片机。

实物图:

测试分析与结论

根据测试数据,可以得到,通过软件控制的锁相环输出频率和实际测到的锁相环输出频率在误差范围内相等。在输出频率较大时波形输出幅度有所衰减,是由于集成芯片内部环路滤波器有所衰减,对输出的频率变化影响不大。可以通过输出端的指示灯观察是否实现锁定。由于灯的闪烁程度看出锁定时间小于1MS。系统将扫频外差法与快速傅里叶变换方法相结合,具有测量时间快、频带范围宽、频率分辨率高、测量精度高的优点,并具备频谱存储与回放功能。

参 考 文 献

[1]戴志坚 师奕兵 王志坚, 逻辑分析仪高速数据采集及数据窗口定位,

[2] 张世箕, 数据域测试及仪器, 电子工业出版社

[3] [美]约输·肯尼 吴运熙、张压西、刘大可译, 逻辑分析仪 ,电子工业出版社