IC+MOS组合电路封装漏电机理探讨

2016-08-08牛社强胡燕燕何文海

牛社强,胡燕燕,何文海

(天水华天科技股份有限公司,甘肃天水741000)

IC+MOS组合电路封装漏电机理探讨

牛社强,胡燕燕,何文海

(天水华天科技股份有限公司,甘肃天水741000)

通过对IC+MOS电路组合特点的讨论,重点对MOSFET晶圆前制程中的缺陷、封装过程的外力损伤缺陷等对封装后产品漏电现象的影响进行了探讨,以期通过制程控制和过程缺陷分析,为MOSFET封装在品质保证上提供保证。

IC+MOSFET组合封装;漏电;芯片缺陷;封装过程;外力损伤

随着节能手机、电脑、电视、汽车等电子产品进入普通消费阶层,同时由于电气开关、充电包的需求急剧增加,IC+MOSFET类的驱动转换电路需求也出现井喷式增加。漏电问题是解决集成电路IC+MOS组合MOSFET器件封装的基础问题之一,本文针对集成电路IC+MOSFET封装中的漏电现象进行探讨,主要对晶圆前制程中的制作缺陷和封装过程的填充料选择引起的应力缺陷进行探讨。

1 封装漏电机理

1.1 MOSFET漏电流简介

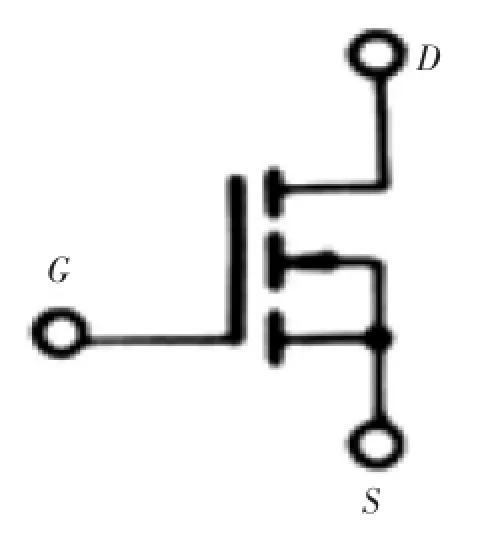

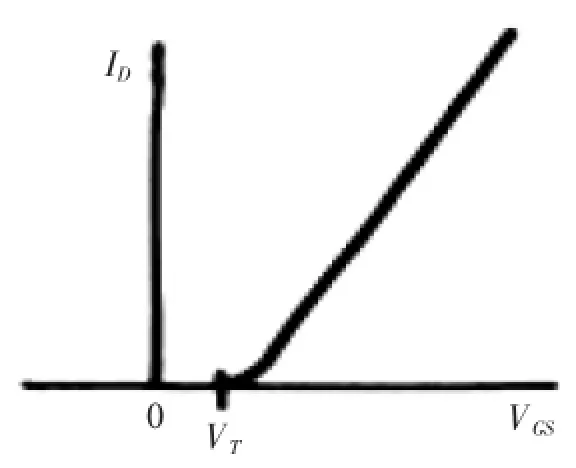

以增强型N沟道的MOSFET为例,如图1所示,当在G、S之间加正电压VGS及在D、S之间加正电压VDS,则产生正向工作电流ID。改变VGS间的电压可控制工作电流ID,当VGS电压太低时,漏源之间无电流ID。当VGS增加到一定值时,其感应的负电荷把两个分离的N区沟通形成N沟道,这个临界电压称为开启电压 (或称阈值电压、门限电压),用符号VT表示(一般规定在ID=10 μA时的VGS作为VT)。当VGS继续增大,ID也随之增加,并且呈较好线性关系,如图2所示,此曲线称为转换特性。故在一定范围内,改变VGS之间的电阻,可以达到控制ID的作用。

图1 N沟道MOSFET

图 2 VGS与ID理论曲线

1.2 IC芯片缺陷对产品漏电的影响

集成电路IC芯片缺陷,是指在晶圆制作(流片)过程中形成的缺陷,包含:铝保护层裂纹、铝保护层损伤、光刻不足、铝线偏移、铝层氧化等。由于晶圆制作过程缺陷,会影响IC封装良率、成本以及产品功能,部分缺陷会延伸至终端客户使用,从而导致更多损失,所以,本节从集成电路IC芯片制作缺陷对封装后漏电进行分析讨论。在集成电路IC前制程的晶圆制作从形成的缺陷中,铝保护层裂纹和铝保护层损伤会导致集成电路IC封装后产品产生漏电[1]。

铝保护层缺陷产生的漏电:当集成电路IC+MOSFET组合封装成品进行ID测试时(测试条件:650 V,160℃,30 min,以下测试方法及条件均相同),示波器上出现以下波形(4颗成品),见图3、图4所示。

图3正常产品ID曲线

图4异常产品ID曲线

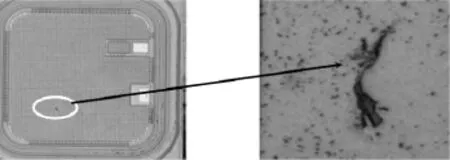

当栅极、源极VGS增加时,漏极电流ID在每颗成品上表现出一致波形特征,为了排除外围材料吸湿引起的信号干扰,该4颗产品随后经过125℃,4 h加热除湿烘焙。再次测试,信号无变化[2]。针对4颗产品进行开封(化学方法去掉包封材料),并对集成电路IC表面进行激光束的OBRICH分析(OBIRCH常用于芯片内部高阻抗及低阻抗分析,线路漏电路径分析.利用OBIRCH方法,可以有效地对电路中缺陷定位,如线条中的空洞、通孔下的空洞、通孔底部高阻区等,也可有效检测短路或漏电,是发光显微技术的有力补充),如图5~图7。

图5高倍下观察的漏电区域

图6进一步放大后漏电区域

图7漏电区域

在MOSFET的源极SOURCE靠近高压保护环附近,阻抗异常,电流偏大见图2;集中MOSFET表面该异常区域,MOSFET表面有电流烧伤。

利用FIB(Focused Ion beam聚焦离子束)对烧伤位置进行切割并在高倍显微镜下放大,如图8所示。

图8 MOSFET表面铝层缺陷

由图8可以看出,MOSFET表面有铝层缺陷,即:铝层裂纹,该铝层裂纹缺陷会引起漏极ID电流比较MOSFET表面其他区域明显偏大。这是因为,当MOSFET器件在瞬态加热时,表面的裂纹缺陷会导致MOSFET结短路或瞬态电阻变小,从而引起漏极电流ID增大。

该漏极电流变化异常只有在瞬间受热或者电流通过时才会显,且该变化在一般的集成电路IC成品常规功能测试中无法检测,只有在模拟成品电路使用环境下才能发现,一旦发现,该缺陷引起的后果是破坏性的,所以,集成电路IC+MOSFET封装中,对晶圆前制程缺陷检测是比较重要的,因为它制约后封装制程的品质以及客户端的使用结果。

1.2材料选择对集成电路IC封装后产品漏电影响

在树脂封装的集成电路IC中,填充用树脂按形状分为两类:结晶型和球形。结晶型树脂聚合为一体后,形状表现为菱角状;球形内部组成树脂聚合后,大聚合物分子外观表现为球形。具体如图9、图10所示。

图9结晶型树脂内部放大图

图10球形树脂内部放大图

1.2.1结晶型树脂包封对MOSFET产品的影响

当使用结晶型树脂包封MOSFET产品时,包封条件为:注塑压力:1 200~1 800 Pa,注塑时间:7~15 s,模具温度:160~180℃,合模压力:8~20 MPa,经125℃温度条件下3 h固化防湿处理,抽取封装后产品使用FIB(Focused Ion beam聚焦离子束)方法进行刨面并观察,菱角形结晶树脂在MOSFET表面产生损伤,具体见图11、图12所示。

图11包封树脂与MOSFET接触区域刨面图

图12开封后采用物理法处理的MOSFET表面损伤区

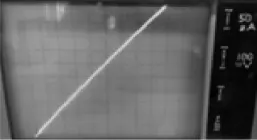

由图11、图12可以看出,当采用结晶型包封树脂时,在高压作用下,MOSFET表面出现应力损伤,同时测试(测试条件:650 V,160℃ 30 min,)未开封样品漏极电流ID,与正常产品对比,示波器显示如图13、图14所示。

图13正常产品ID曲线

图14异常产品ID曲线

可以发现,表面划伤的异常产品漏极电流ID较正常产品偏大,原因是划伤部位由于瞬态高温高压,划伤缺陷导致MOSFET结短路或瞬态电阻变小,从而引起漏极电流ID增大。

1.2.2球型树树脂包封对MOSFET产品的影响

当使用球型树脂包封MOSFET产品时,包封条件为:注塑压力:1 200~1 800 Pa,注塑时间:7~15 s,模具温度:160~180℃,合模压力:8~20 MPa,经 125℃温度条件在3 h固化防湿处理,抽取封装后产品,使用FIB(Focused Ion beam聚焦离子束) 方法进行刨面并开封观察MOSFET表面,如图15、图16所示。

图15 MOSFET与球形树脂接触点刨面

图16开封后的MOSFET

可以看出,MOSFET表面无损伤,对未开封样品在高温高压状态下测试瞬态漏极电流ID,示波器波形正常,所以,在封装时包封树脂选用时,球型树脂相比结晶型树脂,对MOSFET漏极电流影响较小,主要表现在树脂形状对MOSFET表面损伤[3]。

2 结束语

综上,本文针对MOSFET表面缺陷对漏极电流ID的影响进行了初步探讨,对存在晶圆制作缺陷或外力损伤缺陷时,在高温高压条件下,MOSFET漏极电流ID会增加,此外,由于漏极电流ID仅仅在模拟使用条件下才会发生变化,正常条件下的功能测试无法检测瞬态下的漏极电流ID,所以,MOSFET本身缺陷或外力引起的MOSFET损伤缺陷,就显得尤为致命。同时,进一步的对MOSFET漏极电流变化的研究,将是我们持续研究的方向。

[1] 唐冬和.纳米MOSFET散粒噪声抑制及其应用[D].西安:西安电子科技大学,2011.

[2] 沈晔.MOSFET封装不良与最终测试的技术研究[D].上海:上海交通大学,2010.

[3](美)哈拍(Herper,C.A.).电子封装材料与工艺[M]. 3版.沈卓身,贾松良,译.中国电子学会电子封装专业委员会,2006.

Study of Assembly Technology for IC+MOS Package

NIU Sheqiang,HU Yanyan,HE Wenhai

(Tianshui Huatian Technology Co.,Ltd,Tianshui 741000,China)

By IC+MOS circuit combination characteristic,The article focus on:MOSFET wafer process before the flaws of external force damage,encapsulation process of packaging products such as leakage effect were discussed;In order to,through the analysis of the process and process defects on the MOSFET encapsulation quality guarantee to provide the reference.

IC+MOSFET combination packaging;Electric leakage;Chip defects;Package process;External force damage

TN405

B

1004-4507(2016)06-0016-05

2016-04-06

牛社强(1975~),男,工程师,2003年毕业西安理工大学电子科学与技术专业,现于天水华天科技股份有限公司从事集成电路IC塑料封装的工艺优化及组合材料的分析研究工作。