基于FPGA的串口通信电路设计与实现

2016-07-23党俊博李雅俊

党俊博,李 哲,李雅俊

(1. 西安邮电大学 电子工程学院,陕西 西安 710061 ;2. 西安北方捷瑞光电科技有限公司,陕西 西安 710111)

基于FPGA的串口通信电路设计与实现

党俊博1,李哲1,李雅俊2

(1. 西安邮电大学 电子工程学院,陕西 西安 710061 ;2. 西安北方捷瑞光电科技有限公司,陕西 西安 710111)

摘要针对计算机与基于FPGA控制系统需要进行数据通信的需求,采用有限状态机设计了一种串口通信电路。该电路实现了控制系统与计算机之间的通信,包括计算机发送给控制系统的控制命令和参数;控制系统发送到计算机的运行状态信息。使用ISE软件中的嵌入式逻辑分析仪Chipscope对通信电路进行测试,结果表明,该电路工作稳定可靠,能够完成数据传输的功能。

关键词串口通信;FPGA; UART;通信协议

串口以其通信电路简单、可靠性高和传输距离远等优点,广泛应用在计算机与外设之间的通信电路中。串口通信使用通用异步收发传输器(UniversalAsynchronousReceiverTransmitter,UART)和电平转换芯片进行数据传输。一般FPGA芯片中没有集成UART,为使FPGA能进行串口通信,可有两种选择:一种是使用UART专用集成芯片,这种方法设计简单,但会增加电路板的面积和成本;另一种方法是在FPGA内部设计UART,这种方法设计灵活,可靠性高。本文提出了一种使用硬件描述语言VerilogHDL设计UART和高层协议电路的方法,实现了FPGA与计算机之间的数据通信。

1串口通信协议设计

通信协议是指通信双方的一种约定,对数据格式、传输速度、校验方式和字符定义等问题做出统一规定,通信双方必须共同遵守。串口通信协议[1-3]采用分层结构,分为底层协议和高层协议。底层协议采用标准的UART传输协议,高层协议定义了数据包格式和校验方式。

1.1底层协议

UART最重要的参数是波特率、起始位、数据位和停止位。UART数据格式以低电平为起始位,中间传送8bit的数据位,以高电平为停止位,空闲状态为高电平,无奇偶校验位[4]。

底层协议的功能是:发送数据时,将高层协议电路传递过来的并行数据转换为串行数据流,并加入起始位和停止位,按照通信双方约定的波特率,将数据流发送出去;接收数据时,去掉起始位和停止位,将串行数据流转换成字节,然后传递到高层协议电路中。

1.2高层协议

定义由FPGA发送到上位机的数据为上行数据,由上位机发送到FPGA的数据为下行数据。

(1)上行数据包。上行数据长度固定,数据包格式如表1所示。

表1 上行数据包格式

各字段含义定义如下:

帧头:作为数据包的起始标志;

帧序号:参数的顺序号,用以将FPGA中使用的参数读回到上位机;

参数返回:电路当前使用的参数,每个数据包中包含1Byte,多个数据包能够解析出来一组控制参数;

状态信息:设备的运行状态信息;

校验:采用循环冗余校验码(CRC)进行校验;

(2)下行数据包。下行数据包格式如表2所示。

表2 下行数据包格式

帧头和校验:同上行数据包;

参数地址:FPGA内的数据断电后不能保存,因此将参数数据保存到外部EEPROM中,不同的数据包使用不同的地址,参数地址作为一个数据包保存到外部EEPROM的起始地址;

参数数据:控制电路的控制参数。

2FPGA电路设计

串口通信电路包括时钟产生模块、发送通道和接收通道,发送通道和接收通道各自独立工作,互不干扰。时钟产生模块为发送通道和接收通道提供时钟信号。发送通道主要包括发送控制状态机、数据寄存器、移位寄存器、CRC校验模块[5-6]和UART发送模块[7]。接收通道主要包括接收控制状态机、控制参数寄存器、RAM、EEPROM读写控制器[8-9]、CRC校验模块和UART接收模块,整体结构如图1所示。

图1 串口通信电路结构框图

2.1串口发送

串口发送电路从功能上可分为UART发送(底层协议)和发送控制(高层协议)两大模块。根据需要,发送数据包采用周期发送方式,发送周期为400Hz,在发送周期信号的下降沿启动一个数据包的发送。

(1)UART发送模块。UART发送模块由发送状态机、位计数器、数据缓存寄存器和移位寄存器组成,结构示意图如图2所示。发送状态转移描述如下:

IDLE:当byte_ready信号有效后,进入下一状态;

DATA_LOAD:在当前状态,load信号有效,将移位寄存器中的数据连同起始位和停止位加载到移位寄存器中,进入数据发送状态。

DATA_TRANS:当bit_count<9时,en信号使能计数器计数,shift信号使移位寄存器右移,移位寄存器高位填充1,移位寄存器最低位与TxD相连,当bit_count计数到9时,clear信号有效,bit_count清零,TxD_over信号有效一个周期,状态机回到IDLE状态。

图2 uart发送结构示意图

(2)发送控制模块。发送控制模块主要由发送控制状态机、移位寄存器、MUX和CRC校验模块组成,发送控制模块采用状态机的方式设计,状态转移图如图3所示。

图3 发送控制模块状态机

状态描述如下:

IDLE:当400Hz时钟信号下降沿到来时,load信号有效,将帧头连同数据按照一定顺序加载到移位寄存器中,状态机进入数据发送状态;

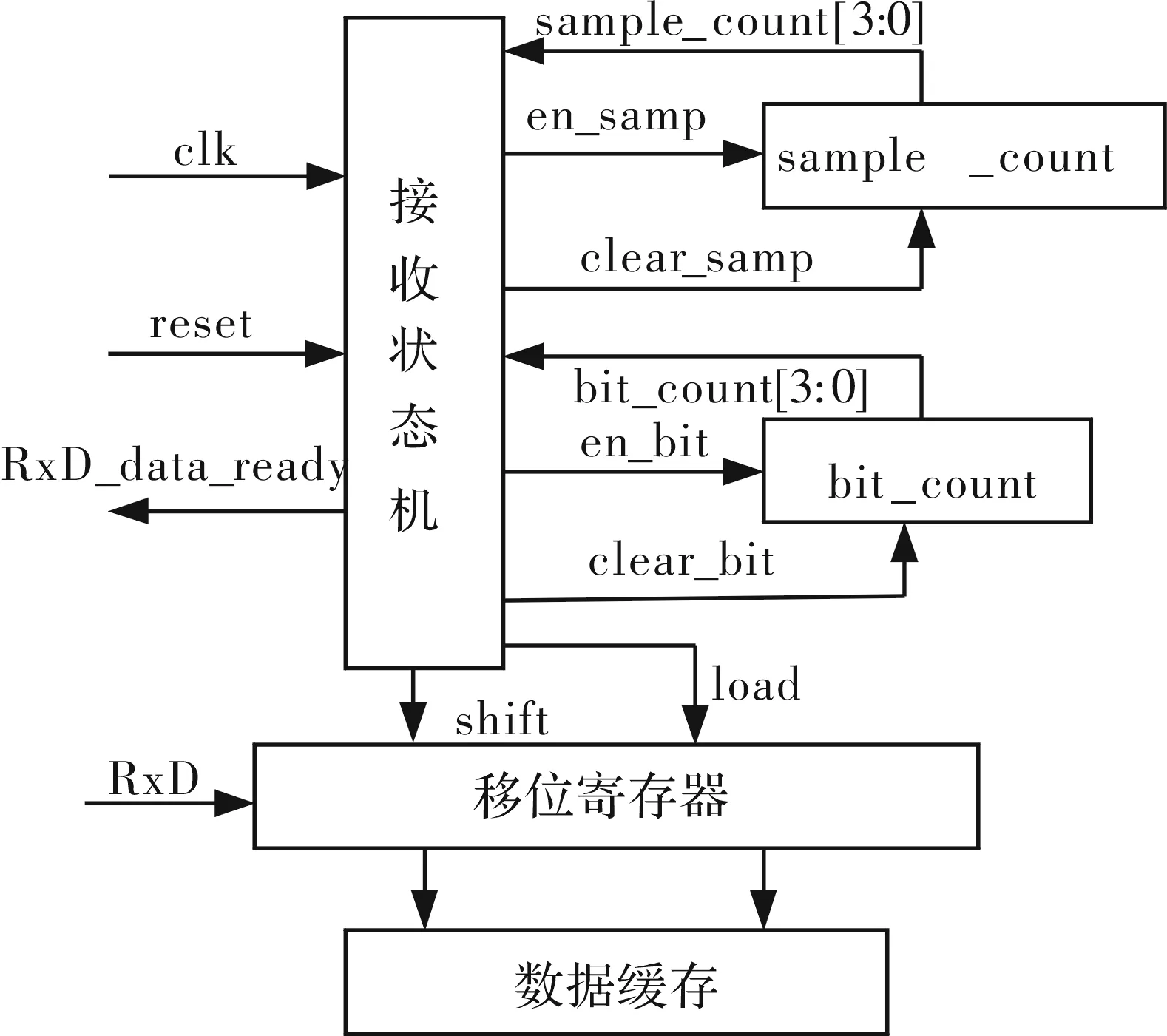

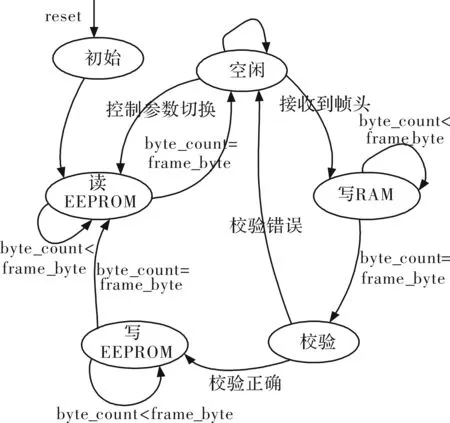

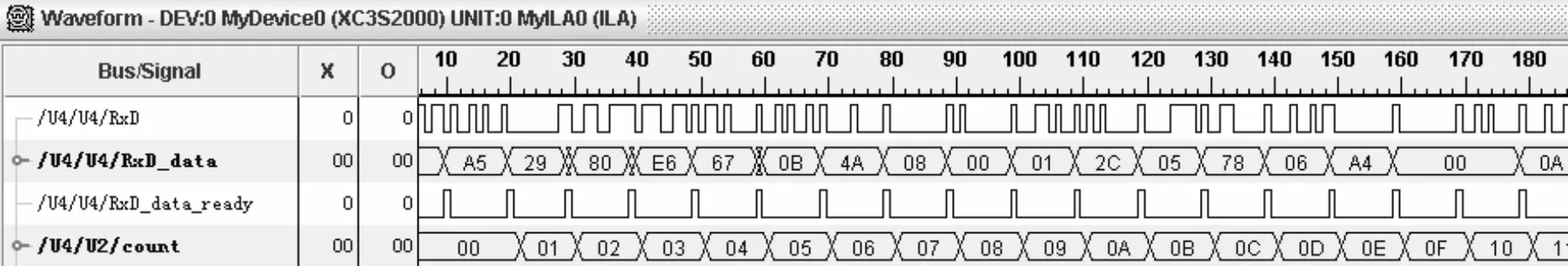

TRANS_CTRL:在发送状态,byte_count加1,移位寄存器右移一个字节,byte_ready信号置1,状态机进入等待状态。当byte_count WAITING:当TxD_over信号有效后,状态机回到发送状态。 2.2串口接收 串口接收由UART接收(底层协议)和接收控制(高层协议)模块组成,实现数据的串并转换、CRC校验以及将参数数据保存到外部EEPROM中的功能。 (1)UART接收模块。UART接收电路结构示意图如图4所示,主要由接收状态机、采样计数器(sample_count)、位计数器(bit_count)、移位寄存器和数据缓存等部分组成。接收状态机的时钟频率是波特率的8倍,当连续四次采样RxD均为低电平时,认为是启动信号,否则认为是噪声信号。此后,在接收电平的中间时刻,将电平数据放入移位寄存器中,每接收一位数据,采样计数器清零一次,位计数器加1,shift信号有效,移位寄存器右移一次。当位计数器加到8时,位计数器清零,load信号有效,将移位寄存器内的数据放入数据缓存区,同时RxD_data_ready信号有效,请求高层电路读取数据; (2)接收控制模块。接收控制模块由接收控制状态机、RAM、CRC校验模块和EEPROM读写控制模块组成。接收控制模块采用状态机的方式设计,状态转移图如图5所示。 图4 UART接收电路结构示意图 图5 接收控制状态转移图 INIT:上电复位后,状态机在此状态,然后状态机进入读EEPROM状态; IDLE:当RxD_data_ready信号有效后,若RxD_data=0xA5时,状态机进入写RAM状态;当需要读取其他段控制参数时,状态机进入读EEPROM状态; WRITE_RAM:当接收请求信号有效后,将RxD_data写入到RAM中,同时对接收的字节数进行计数,当byte_count=frame_byte时,状态机进入校验状态; CRC_CHECK:当接收请求信号有效后,接收的RxD_data即为上位机发送过来的校验字,将其与内部生成的CRC校验字进行对比,当校验正确后,状态机进入写EEPROM状态,否则回到空闲状态; WRITE_EEPROM:将数据从RAM中读出写入到外部EEPROM中,对写入的字节数进行计数,当byte_count=frame_byte时,状态机读EEPROM状态; READ_EEPROM:从EEPROM中读出刚写入的数据,并将数据分配到控制参数寄存器中,每读一个字节,byte_count加1,当byte_count=frame_byte时,状态机进入空闲状态。 3数据传输测试 随着逻辑电路设计复杂性的不断增加,仅依靠软件仿真对硬件电路测试具有较大的局限性。使用ISE集成开发环境中的嵌入式逻辑分析仪Chipscope,可将测试电路和设计电路一起下载到目标芯片中[10]。测试电路对设计电路中的数据流进行采集,而又不影响设计电路的正常工作,测试数据通过JTAG发送到ISE软件中以波形的形式显示出来,这是一种高效的测试方法,能够较好地对硬件电路进行测试。 FPGA选用Xilinx的XC3S2000器件[11],该器件具有丰富的逻辑资源和硬件乘法器,能满足电路的设计需求。将测试电路和设计电路一并下载到FPGA芯片中,计算机端运行上位机软件和ISE软件,然后分别对发送通道和接收通道电路进行测试。图6为串口发送通道信号测试波形,图7是串口接收信号测试波形,图8是将接收到的数据从EEPROM中读出,然后分配到 图6 串口发送数据波形 图7 串口接收数据波形 图8 串口接收数据分配波形 控制参数寄存器中的波形。测试结果表明,发送通道和接收通道功能正常。 4结束语 基于FPGA设计实现的UART和高层协议电路,可使用较少的逻辑资源实现串口通信的功能,能有效提高系统的可靠性和稳定性,减小电路板面积,降低成本,且便于移植在其他FPGA通信电路中。串口通信协议和电路经过严格的测试,目前已应用到实际产品中。 参考文献 [1]李煊,丁为.常用设备串口通信协议及其应用[J].自动化仪表,2011,32(10):82-86. [2]冯子陵,俞建新.RS485总线通信协议的设计与实现[J].计算机工程,2012,38(20):215-218. [3]张伟.基于FPGA的通信接口模块设计与实现[J].电子科技,2012,25(7):95-98. [4]杨晶.基于FPGA的UART接口协议转换模块设计[D].哈尔滨:哈尔滨工业大学,2014. [5]田佳,王一平.基于FPGA的带CRC校验的异步串口通信[J].现代电子技术,2010,33(20):5-7. [6]刘春阳.基于FPGA的串行通信实现与CRC校验[D].北京:北京化工大学,2006. [7]杨扬,叶芃,李力.基于FPGA的UART设计与实现[J].电子测量技术,2011(7):80-82. [8]黄晓敏,张志杰.基于FPGA的IIC总线IP核设计[J].测试科学与仪器:英文版,2015(1):13-18. [9]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2008. [10]万翔.ChipScopePro在FPGA调试中的应用[J]. 计算机与网络,2005(21):58-59. [11]XilinxCorpration.Spartan-3FPGAfamilydatasheet[EB/OL]. (2013-06-27)[2015-08-22]http://www.xilinx.com. Design and Implementation of Serial Communication Circuits Based on FPGA DANGJunbo1,LIZhe1,LIYajun2 (1.SchoolofElectronicEngineering,Xi’anUniversityofPostsandTelecommunications,Xi’an710061,China; 2.NorthJieruiPhotoelectricTechnologyLtd.,Xi’an710111,China) AbstractA serial communication circuit is designed by finite state machine for the requirement of data communication between computer and control system based on FPGA. The circuit realizes the communication between the control system and the computer, including the control commands and parameters the computer sends to the control system and the status information the control system sends to the computer. The communication circuit is tested by the embedded logic analyzer Chipscope in the ISE software. The results show that the circuit is stable and reliable, and can complete the function of data transmission. Keywordsserial communication; FPGA; UART; communication protocol 收稿日期:2015- 11- 15 作者简介:党俊博(1989-),男,硕士研究生。研究方向:通信电路与系统。李哲(1963-),男,教授。研究方向:嵌入式系统和激光陀螺。 doi:10.16180/j.cnki.issn1007-7820.2016.07.031 中图分类号TN79+1 文献标识码A 文章编号1007-7820(2016)07-106-04