基于Nios II的线阵图像传感器驱动设计

2016-07-01陈文艺雷武亮

陈文艺, 雷武亮, 杨 辉

(1. 西安邮电大学 物联网与两化融合研究院,陕西 西安 710061; 2 西安邮电大学 通信与信息工程学院,陕西 西安 710121)

基于Nios II的线阵图像传感器驱动设计

陈文艺1, 雷武亮2, 杨辉1

(1. 西安邮电大学 物联网与两化融合研究院,陕西 西安 710061; 2 西安邮电大学 通信与信息工程学院,陕西 西安 710121)

摘要:针对线阵图像传感器DLIS-2K,设计一个基于FPGA/Nios II的串口通信驱动系统。选用Altera Cyclone IV系列FPGA芯片EP4CE10E22C8N作为硬件设计平台,在SOPC(可编程片上系统)中采用Nios II软核处理器实现传感器串口通信方案,给出了SOPC及传感器串口模块的硬件驱动电路,使用Verilog HDL语言进行描述,并对设计的驱动电路进行了仿真。结果表明,设计的驱动系统能使传感器串口正常工作。

关键词:现场可编程门阵列;线阵;时序控制;串口通信;Nios II

互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)图像传感器的研究开始于20世纪80年代早期[1],随着超大规模集成电路工艺在近年来的飞速发展,线阵CMOS图像传感器集成度不断提高,性能不断完善,可应用于多种场合,如条形码、机器视觉、边沿检测、接触成像、指纹印和编码定位[2]。

Nios II系统开发与传统现场可编程门阵列(Field Programmable Gate Array,FPGA)开发相比,增加了一个中央处理器(Central Processing Unit,CPU),从而简化了复杂的设计[3]。Nios II处理器是一种面向用户的可以灵活定制的通用精简指令集架构嵌入式CPU。它将硬件设计软件化,降低了设计难度,缩短了开发周期[4]。目前,国内外设计图像传感器驱动较多采用硬件语言描述出驱动电路或者设计硬核来为传感器芯片提供驱动时序[5-7],使用该方法须将传感器内部寄存器地址都写入硬件设计中,当改变寄存器设计时,须在硬件源代码中进行修改,使系统不易于升级。为了在驱动系统硬件核不变的情况下实现传感器寄存器配置,设计一个采用Nios II处理器结合片上可编程系统[8](System On a Programmable Chip,SOPC)的串口通信驱动系统,来实现线阵CMOS图像传感器的内部寄存器配置。该系统将硬核模块挂载到avalon总线上,只需软件通过Nios II处理器向传感器写入寄存器地址值便可对寄存器进行配置。

1DLIS-2K线阵图像传感器

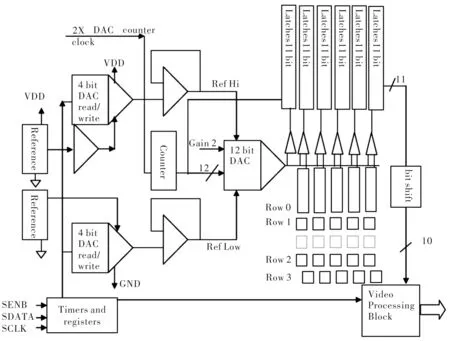

DLIS-2K是一个具有用户可编程的时序引擎的多模式线阵图像传感器[9],其工作原理如图1。传感器在单电源3.3 V供电正常工作时,加入主时钟以及开始信号,三线串口读写正常,此时串口可进行读写操作,串口时钟范围最大值为20 MHz。

传感器内部共有42个寄存器,其中定义了33个寄存器,这33个寄存器定义了传感器工作所需的参数以及工作模式[10]。传感器的设置和控制信息发送到设备内部寄存器的通信通过一个三线串行接口来实现,这三线分别为:串行使能引脚(SENB),用于使能串行接口;串行数据接口(SDATA),用于发送或接收寄存器的地址或寄存器的值,其建立时间至少为10 ns;串行时钟接口(SCLK)。

图1 传感器工作原理

传感器串口通信由36个时钟周期来完成,完整的写时序配置在串口使能信号被拉高时开始,持续32个时钟周期,每个时钟周期发送1位数据,前15位为地址信号,第16位为读写控制位,其中0为写。第17至32位为寄存器写入值,在配置完成后,需要4个时钟周期来对寄存器进行值的更改。传感器的一个完整读时序与写时序差别在于第16位读写控制位的值为1(逻辑高电平)。

2系统设计

2.1系统结构

系统整体包括线阵CMOS图像传感器图像采集、FPGA逻辑控制以及PC机的软件设计3个部分,系统结构如图2所示。硬件部分是用Verilog HDL硬件描述语言实现的传感器串口驱动系统,软件部分在Nios II IDE中完成的一个需要硬件系统支撑的在线调试系统。

图2 系统设计框图

2.2软件系统设计

Nios II的软件开发部分以硬件开发部分为基础,软件平台采用一个基于Eclipse IDE架构的集成开发环境Nios II IDE来进行设计。硬件设计完成之后,软件将硬件代码重新编译,产生系统头文件system.h,其内部描述为一些宏定义,需要关注的是基地址的值。硬件系统中的每个外设都有基地址,软件设计中通过每个外设的基地址对Nios II软核进行寄存器操作。

2.3Nios II下的传感器IP核设计

FPGA型号采用Cyclone IV系列EP4CE10E22C8N,该芯片有10 320个逻辑单元(LE),有42万个存储位(memory bit),两个PLL(锁相环),并且支持Nios处理器。硬件系统主要完成用户自定义外设IP核[11]并添加到Avalon总线上,构建了Nios II系统下的串行通信接口。

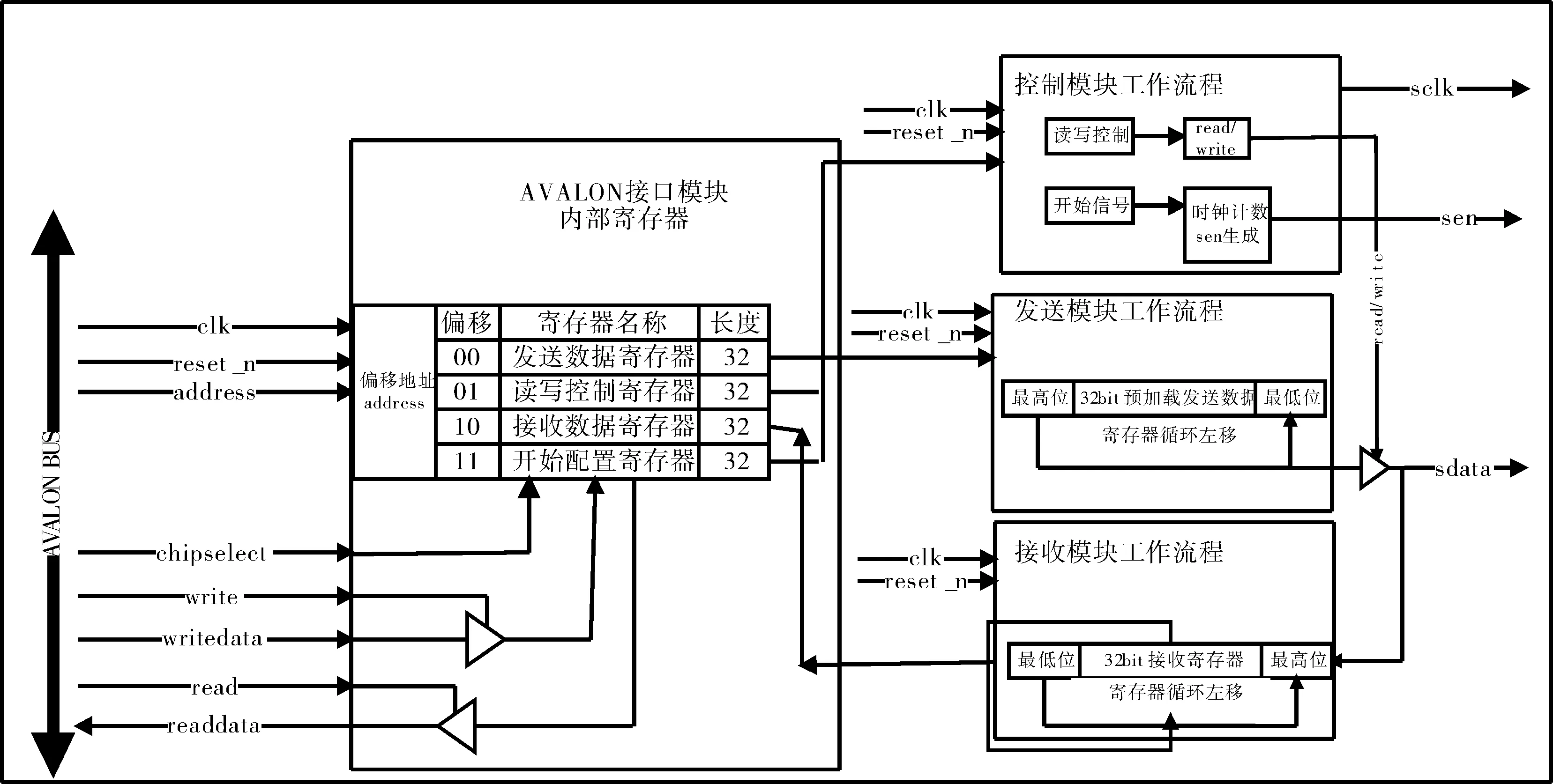

FPGA核心板的时钟为100 MHz,SOPC系统采用锁相环(PLL)将系统时钟的五分频(20 MHz)作为模块的时钟输入。系统采用自顶向下的设计方法[12],在Quartus II 11.0硬件设计平台下采用Verilog HDL硬件描述语言来对整个硬件系统进行设计。将整个时序控制部分分为Avalon接口模块、发送模块、接收模块和控制模块4个模块。4个模块之间有严格的依赖关系,其内部框图如图3。

Avalon接口模块内部有发送数据寄存器、读写控制寄存器、接收数据寄存器和开始配置寄存器4个寄存器。软件可以通过Nios II系统对这4个寄存器进行读写访问,所有其他模块都通过接口模块与Avalon总线结构进行交互,这4个内部寄存器的寻址方式与片选信号,偏移地址信号,读写信号有关,当片选以及读或写信号有效时,偏移地址指向的寄存器将执行读或写操作。

发送模块中设计了一个32位的循环移位器[13],该模块由控制模块产生的控制信号来读取接口模块中发送寄存器中的值,并且循环移位发送最高位的值(高位在前,低位在后),接收模块用于接收在读状态下的传感器DLIS-2K发送来的16位值,并存储于接收寄存器。控制模块产生串口使能信号以及各模块所需要的控制信号。

图3模块内部框图

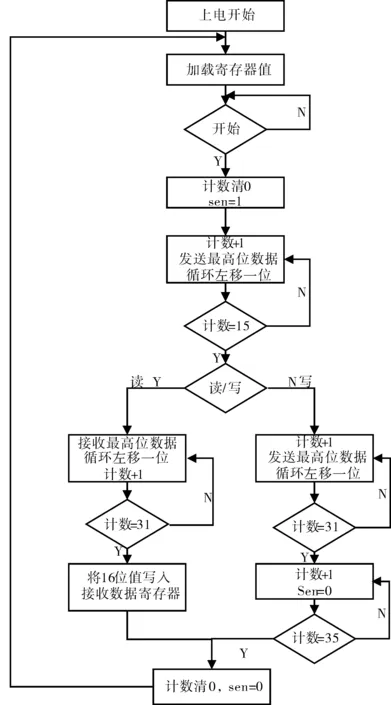

硬件算法流程如图4所示,上电开始后,由软件通过Avalon总线向模块内部的发送数据寄存器写入32 bit数据,随之判断开始配置的信号是否来到,若来到,则开始配置。首先,让串口使能信号SEN拉高,同时计数器清零,然后,开始计数,每次计数都将发送数据寄存器中的最高位发送到双向信号SDATA上,最后,对该寄存器的32bit数据进行循环左移操作,以保证每次发送的最高位的正确性。当计数到15时,将根据读写控制寄存器判断本次配置操作的类型,读或者写操作。若为读操作,则此时在时钟下降沿到来时,SDATA为输入状态,读取传感器内部寄存器数据,同时继续计数,当计数到31时,将读取到的16位数据发送至接收数据寄存器,读操作完成。若为写操作,则继续发送移位寄存器的最高位,继续循环左移1位,直到计数值到31时,本次配置完成,将串口使能信号SEN置0,结束配置,然后继续计数到35之后计数器清零,本次写操作完成。可以进行下一次配置。

图4 算法流程

3仿真及试验

为检验各个模块功能的正确性,利用Modelsim仿真工具编写测试向量来模拟Avalon接口信号,并对模块的读写进行了功能仿真。

在读操作时序中,与写操作不同的地方在于在最后16 bit,串口数据SDATA的方向为输入(写操作为输出),在测试向量中设计了三态门仿真方法,待测模块及其核心测试代码为

sdata=(write_read==0)?sdata_write:1'bz

该代码描述了一个三态门,在测试向量中,sdata为最终写入信号,其信号值由write_read和sdata_write共同提供,在发送前16bit时,write_read为高电平,禁止赋值给sdata,在后16bit时,需要将write_read置为0,通过改变sdata_write的值来对sdata赋值。通过此方法,测试模块便可通过改变sdata_write和write_read的值来对sdata的输入功能进行仿真,读仿真完成之后,查看接收数据寄存器与sdata接收到的16bit值是否一致。

自定义IP核的代码编写完成之后,在SOPC Builder中生成了SOPC系统。利用Component Editor生成自定义IP核作为系统一部分,结合Nios II处理器模块,系统ID模块,JTAG_UART片上调试模块,以及onchipmemory片上FLASH模块生成了一个图像传感器串口通信嵌入式系统。SOPC系统验证在NIOS II IDE中完成,其核心代码为

IORD(DLIS_2K_BASE,1)

IOWR(DLIS_2K_BASE,1,DATA)

在软件中首先指向SOPC系统中IP核的基地址(DLIS_2K_BASE),其偏移量为定义的寄存器。DATA为向寄存器写入的数据。

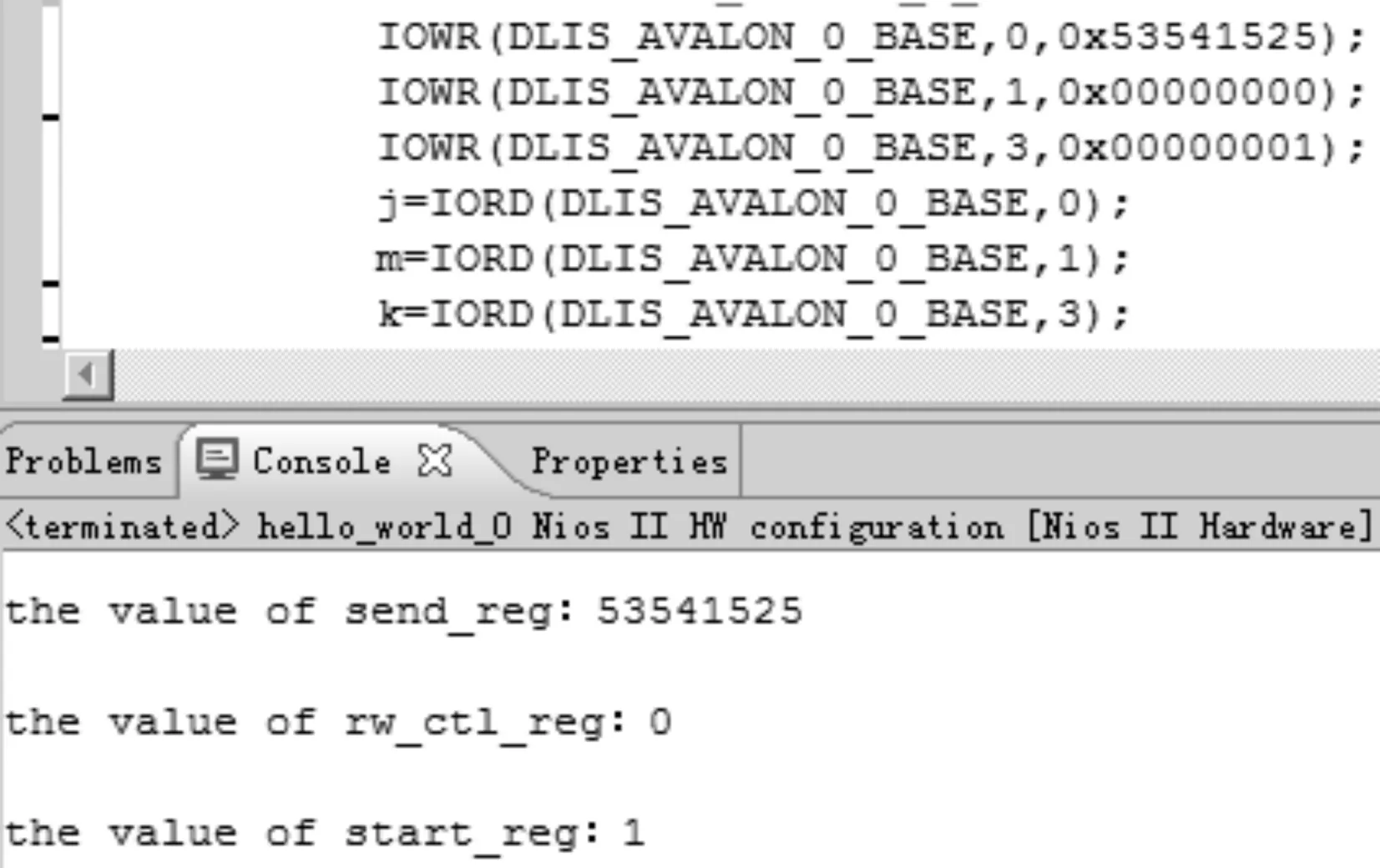

仿真结果及SOPC系统如图5。

图5 仿真结果及SOPC系统

由仿真结果可以看出,在模块执行一次写操作时序中,偏移地址信号address为00,片选信号chipselect为1,写使能信号write为1,输入的数据信号值writedata为0x55151515,在时钟上升沿来到时存进发送寄存器send_reg,然后又将0x0000000e写入读写控制寄存器,0x3f3f3f3f写入接收寄存器,0x00000001写入开始寄存器,写入完毕,系统开始配置,控制模块产生一系列信号生成了串口使能信号sen,将send_reg的32位值循环移位发送到了双向信号sdata上,然后缓冲4个周期,等待图像传感器端的寄存器写入。

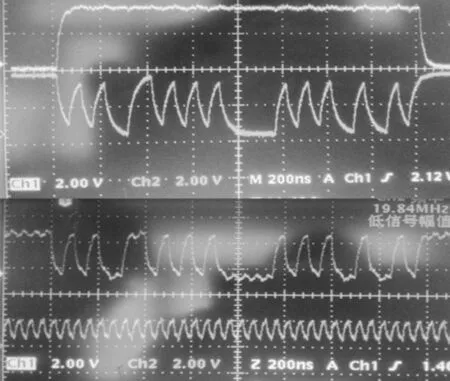

Nios IDE与FPGA开发板联合仿真测试中,寄存器通过系统函数写入与读取如图6,引脚输出的波形如图7。通过IOWR函数向发送数据寄存器send_reg,读写控制寄存器rw_ctl,开始配置寄存器start_reg写入预置值,然后通过IORD读取该值,由结果可看出通过Avalon接口读取模块配置信息正确。由示波器双通道的局限性,通过两次实际测量可验证出所设计的驱动系统输出信号。图7中从上至下,信号分别为串口使能sen、串口数据sdata、串口数据sdata和串口时钟sclk。在Nios II IDE软件中向发送寄存器写入的值为0x53541525(十六进制),串口使能先在此期间为高电平,串口时钟为20 MHz。输出波形符合数据手册中的理论波形,从而验证了所设计的驱动系统正确性。

图6 寄存器读写

图7 实际测试

4结束语

在分析线阵CMOS图像传感器DLIS-2K的内部寄存器工作时序基础上,设计了一个传感器驱动的嵌入式系统,仿真验证结果表明,该系统实现了在Nios II系统下寄存器的配置,自定义IP核具有较好的可重用性,满足了图像传感器的驱动要求。

参考文献

[1]晋孝峰,岳素格,刘丽艳,等.CMOS图像传感器的硬复位电路研究[J].电子学报,2014(1):182-186.DOI:10.3969/j.issn.0372-2112.2014.01.029.

[2]孙佳帝.基于SOPC的图像采集及传输系统设计[J].电子器件,2014,37(6):1116-1120.DOI:10.3969/j.issn.1005-9490.2014.06.022.

[3]江志东,高太长,孙海洋,等.线阵CMOS图像采集及编码传输的实现[J].传感技术学报,2012,24(4):554-558.DOI:10.3969/j.issn.1004-1699.2011.04.017.

[4]郭燕波,于晓洲,周军.组合导航高性能Nios II软核处理器研究[J].计算机测量与控制,2013,21(10):2868-2871.

[5]CHENG K W, YIN C, HSIEH C C, et al. Time-Delay In-Tegration Readout with Adjacent Pixel Signal Transfer for CMOS Image Sensor[C]//2012 International Symposium on VLSI Design, Automation, and Test(VLSI-DAT),Hsinchu:IEEE, 2012:1-4.DOI:10.1109/VLSI.DAT.2012.6212600.

[6]YASVTOM K, ITOH S, KAWAHITO S. A Two-Stage Charge Transfer Active Pixel CMOS Image Sensor With Low-Noise Global Shuttering and a Dual-Shuttering mode[J]. IEEE Transaction on Electron Devices, 2011, 58(3): 740-747.DOI:10.1109/TED.2010.2095856.

[7]潘越,宋萍,李科杰.基于PowerPC和FPGA的小型无人直升机飞行控制器计算机系统设计[J].计算机测量与控制,2013(1):112-115.DOI:10.1109/VLSI.DAT.2012.6212600.

[8]戴迎珺.基于SOPC的USB设备控制器IP核设计[J].计算机工程与设计,2008,29(20):5234-5236.

[9]李继军,杜云刚,张丽华,等.CMOS图像传感器的研究进展[J].激光与光电子学进展,2009(4):45-52.DOI:10.3788/LOP 20094604.0045.

[10]杨波,陈文艺.基于FPGA的高速CCD驱动电路的设计与实现[J].西安邮电学院学报,2010,15(1):93-97.

[11]樊宏.基于Nios II的视频采集及系统分析[J].西安邮电学院学报,2010,15(3):85-88.

[12]何鑫,周健,聂晓明,等.基于线阵图像传感器的新型空间滤波测速仪[J].红外与激光工程,2014,43(12):4117-4122.DOI:10.3969/j.issn.1007-2276.2014.12.049.

[13]袁兴,王林林,王桂海,等.基于Nios II的视频采集及网络传输系统的实现[J].计算机工程与设计,2013,34(2):485-489,506.

[责任编辑:祝剑]

Driving design of linear image sensor based on Nios II

CHEN Wenyi1,LEI Wuliang2,YANG Hui1

(1. Institute of Internet of Things and IT-based Industrialization, Xi’an University of Posts and Telecommunications, Xi’an 710061,China;2. School of Communication and Information Engineering, Xi’an University of Posts and Telecommunications, Xi’an 710121,China)

Abstract:A drive system of serial communication based on FPGA/Nios II is designed for the linear cmos image sensor DLIS-2K. The Cyclone IV FPGA chip of EP4CE10E22C8N of Altera is chose as the hardware design platform, and the DLIS-2K serial communication is designed by using the FPGA scheme of embedded soft core processor Nios II. Simulations are carried out for this circuit design. Experiments show that the designed drive circuit can achieve the serial work.

Keywords:FPGA, linear, timing control, serial communication, Nios II

doi:10.13682/j.issn.2095-6533.2016.01.017

收稿日期:2015-06-09

基金项目:陕西省科技厅工业攻关计划资助项目(Z013K06-14)。

作者简介:陈文艺(1964-),男,教授,从事数字图像处理及传输研究。E-mail:chenwy@xupt.edu.cn 雷武亮(1988-),男,硕士研究生,研究方向为数字图像处理。E-mail:leiwuliang@163.com

中图分类号:TP391

文献标识码:A

文章编号:2095-6533(2016)01-0084-05