可编程时钟芯片在高速图像处理系统中的应用

2016-06-24周全陈锡侯

周全,陈锡侯

(重庆理工大学 机械检测技术与装备教育部工程研究中心 时栅传感及先进检测技术重庆市重点实验室,重庆 400054)

可编程时钟芯片在高速图像处理系统中的应用

周全,陈锡侯

(重庆理工大学 机械检测技术与装备教育部工程研究中心 时栅传感及先进检测技术重庆市重点实验室,重庆 400054)

摘要:随着图像处理系统对速度的要求越来越高,系统中时钟的稳定性和同步就显得非常关键,单颗晶振的方法已经不能满足发展需要。针对这一问题,提出了一种新型可编程可输出多路差分时钟的芯片CDCM6208,通过编程方法调节芯片的输出时钟频率,具有稳定、灵活、适用范围广的特点,并通过实验验证了此芯片在高速图像处理系统中的效果。

关键词:高速图像处理;差分时钟;多路输出;编程控制

引言

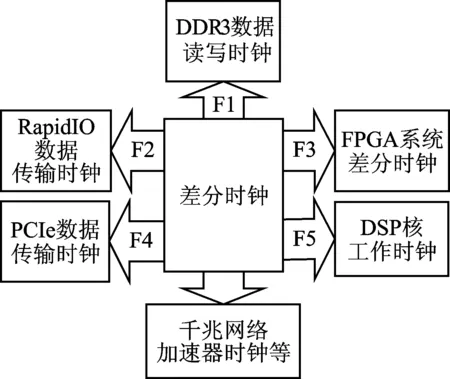

随着数字化技术的不断发展和完善,基于FPGA+DSP架构的高速数字图像处理系统已广泛应用于工业、军事、生物、医疗等领域[1-2],由于这种架构需要用到多种高速接口进行数据传输处理,因此高速差分时钟就成为设计的关键。图1给出了在高速图像处理领域常用到的高速差分时钟。

图1 常用的高速差分时钟

传统数字图像处理系统在进行时钟设计时,都是采用单颗固定频率的时钟晶振,由于每个晶振的标称频率和实际频率存在误差[3],且多个单颗晶振分别工作,不符合高速图像处理系统对时钟稳定和同步的需求[4],此外由于高精度晶振价格高昂且电路板成型后不易更改,所以对设计的准确性和采购的全面性提出了很高的要求,然而在这方面往往需要耗费大量的时间、人力和物力,而且还经常不尽如人意。本文提出了一种新型的可编程差分时钟芯片,该时钟芯片可以同时产生8路差分时钟输出,且每一路输出时钟的频率可以通过编程方式进行灵活调节,满足了高速时钟设计对同步、稳定、灵活的要求。

1芯片工作原理

1.1芯片总体架构

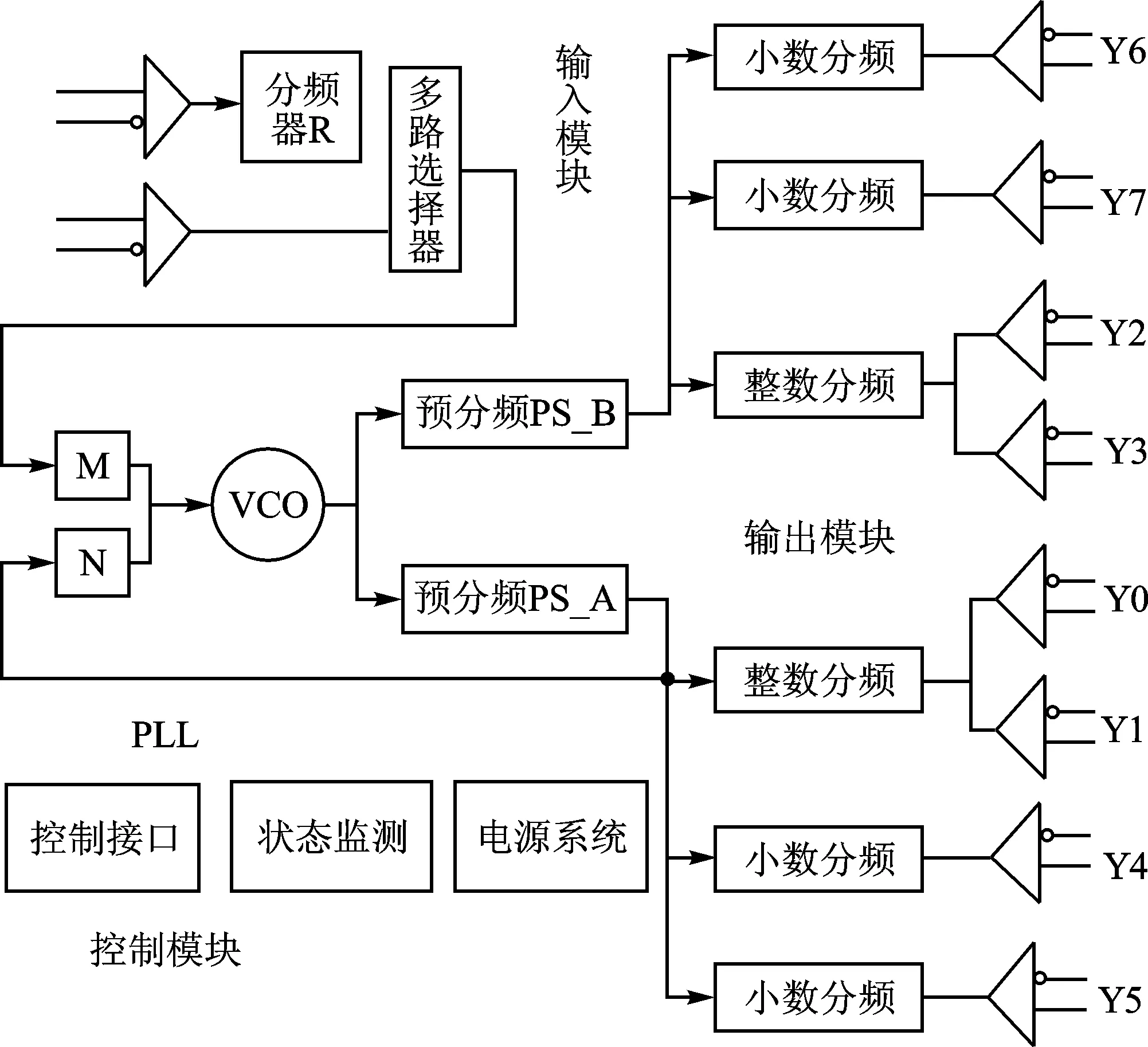

如图2所示,本芯片包含4个模块:输入模块、锁相环、输出模块、控制模块。输入模块包含分频器R和多路选择器,分频器R对第一路输入时钟进行分频,多路选择器完成对两路输入时钟的选择;锁相环模块完成输入时钟的滤波和倍频,并将倍频后的时钟传送至输出模块;输出模块将从锁相环出来的时钟进行分频后输出至外部端口Y0~Y7,其中输出端Y0~Y3可以进行整数分频,Y4~Y7可以进行小数分频。控制模块包含主机接口、状态控制、电源状态模块,通过控制模块可以完成对芯片工作状态的控制。

图2 芯片功能框图

1.2芯片工作流程

芯片的工作流程如图3所示,在上电后先检测掉电引脚PDN的状态,若为低则继续等待,若为高则进入下一个状态;然后进行模式选择,一共有3种模式,即检测外部引脚状态模式、I2C模式和SPI模式;在进入各自状态后将进行相关配置,最后确认芯片各状态正常后芯片将正常运行。

图3 芯片工作流程图

1.3输出频率计算

芯片CDCM6208的频率计算分为两种模式——引脚模式和编程模式,下面分别予以说明。

引脚模式:当SI_MODE[1:0]=10时,芯片工作在引脚模式,配置外部引脚PIN[4:0]不同的状态,从而输出不同标准、不同频率的时钟,这里不做详细讨论。

编程模式:当SI_MODE[1:0]=00、01时,芯片分别工作在SPI模式和I2C模式,这两种模式都是通过编程配置芯片寄存器的方式来控制输出不同的时钟频率,这种方式非常灵活,本文对此种方式输出频率的计算予以具体说明。

如图2所示,当锁相环工作在闭环模式,第一时钟输入端作为输入参考时钟时,锁相环的输出时钟计算公式为:

(1)

其中fPRI_REF为第一参考时钟端频率,R为输入模块第一时钟端的分频器。

当锁相环工作在闭环模式,第二时钟输入端作为输入参考时钟时,锁相环的输出时钟计算公式为:

(2)

其中fSEC_REF为第二参考时钟端频率,最终输出频率fOUT为:

(3)

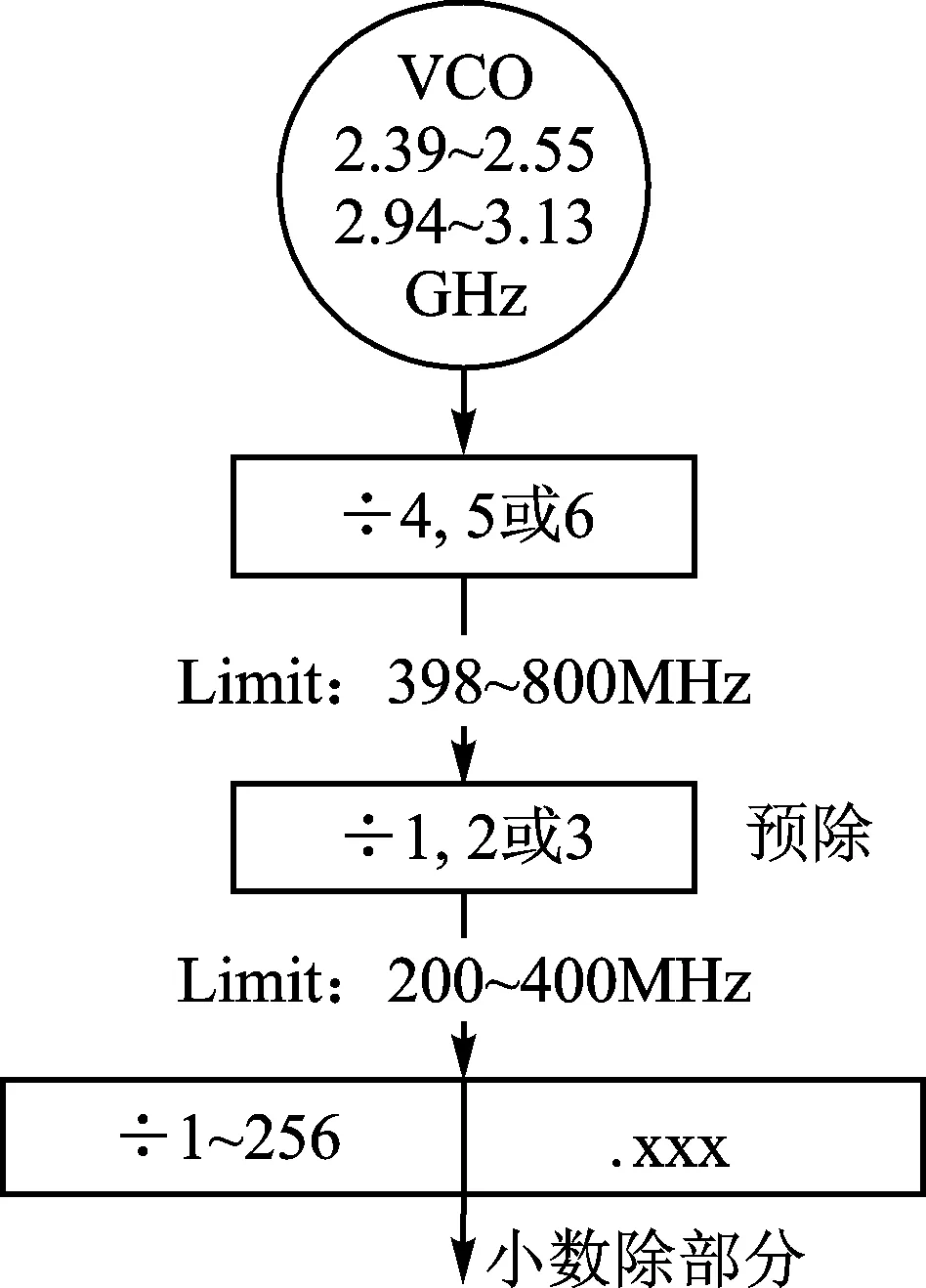

图4 小数分频输出端的计算流程

其中O为输出端分频器分频值,当式(3)使用PS_B时,fOUT为Y2、Y3、Y6、Y7端的频率,图4给出了小数分频输出端(Y4~Y7)的输出计算流程。整数分频输出端(Y0~Y3)的输出计算方式没有图4中的预除部分。

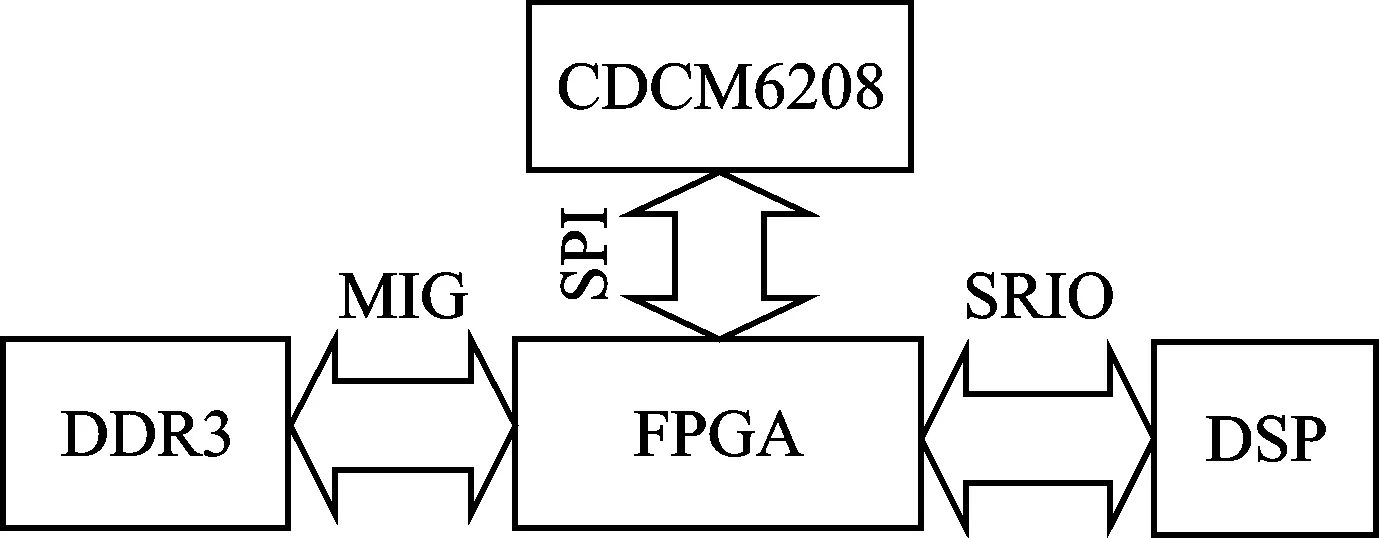

2实验平台搭建

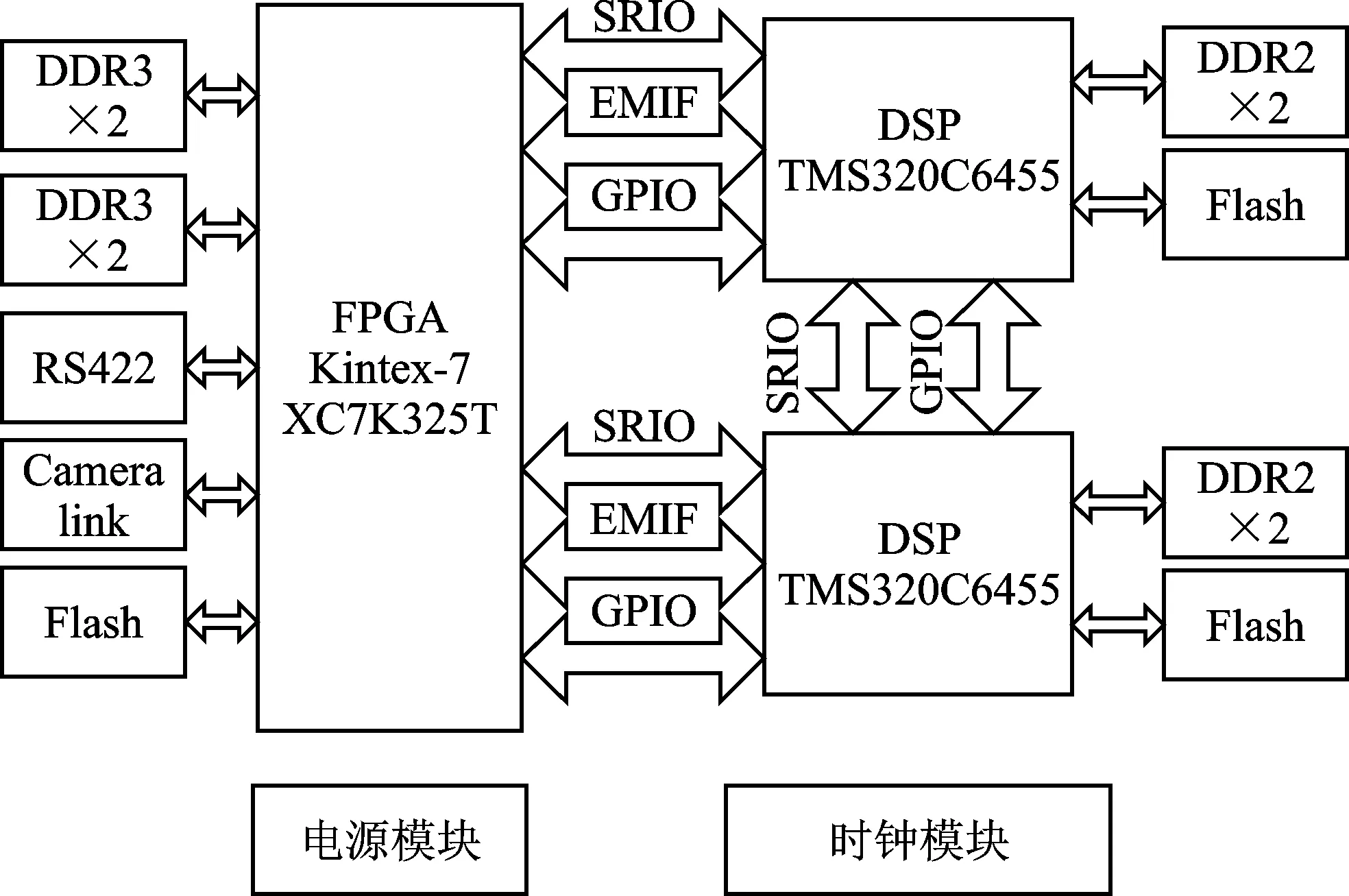

本文所使用的FPGA+DSP架构高速图像处理实验平台,FPGA采用Xilinx公司的XC7K325T,DSP采用TI公司的TMS320 C6455,高速差分时钟芯片采用TI公司的CDCM6208,具体实验平台框图如图5所示。

图5 实验所用硬件平台框图

2.1时钟芯片外围硬件电路设计

根据CDCM6208的工作需求,图6~8给出了芯片的外围设计电路,下面对各个设计方案予以介绍。

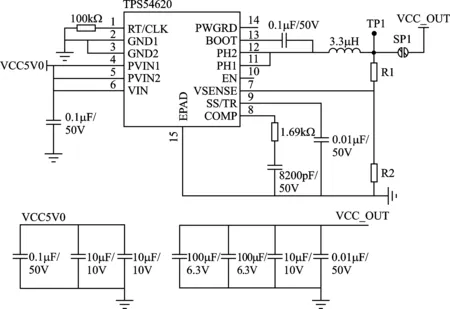

2.1.1电源设计

差分时钟芯片CDCM6208的工作电压为3.3 V,输出时钟的基准电压可为1.8 V、2.5 V、3.3 V,这些常用供电电压可以直接由高速图像处理系统的供电电源提供。这里介绍一种图像处理系统中常用的电源——TI公司的TPS54620,其输入电压VIN为4.7~17 V,输入电压PVIN范围为1.6~17 V,输出电流为6 A,输出参考电压为0.8 V,输出电压可通过R1、R2调节,计算公式为:

图6给出了系统电源典型设计。

图6 系统电源典型设计

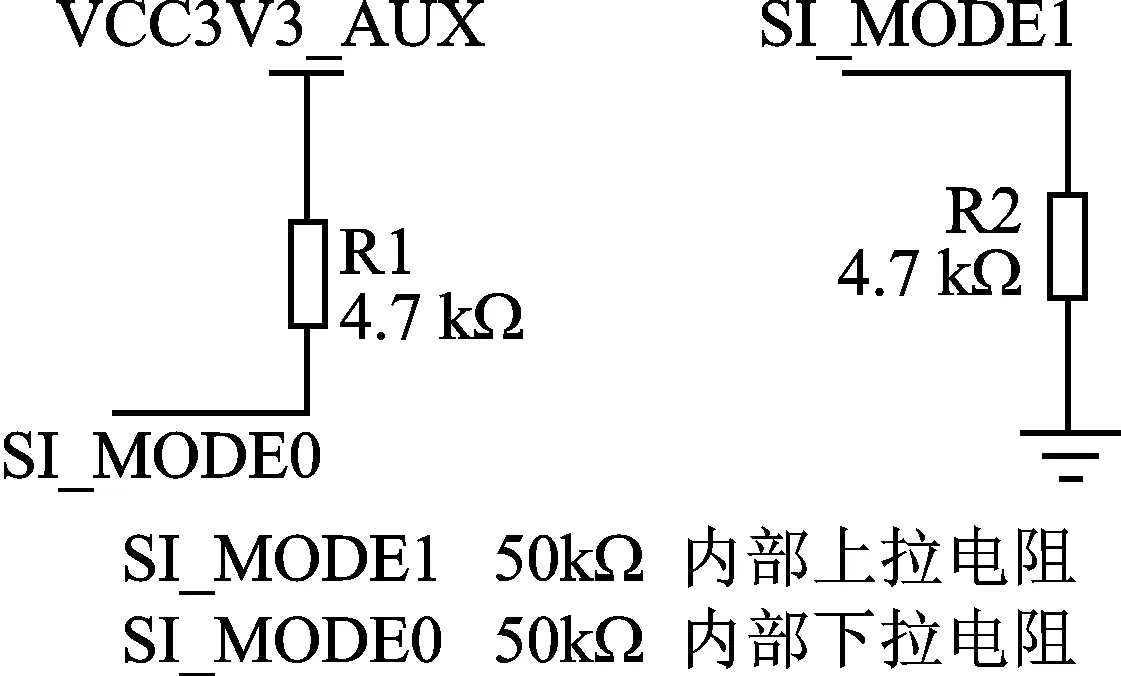

2.1.2工作模式选择

图7 CDCM6208工作模式设置

差分时钟芯片CDCM6208的模式选择有4种:SI_MODE[1:0]=00,芯片工作在SPI模式,SI_MODE[1:0]=01,芯片工作在I2C模式;SI_MODE[1:0]=10,芯片工作在PIN模式;SI_MODE[1:0]=11,模式保留。因为SI_MODE[1:0]引脚带内部上拉和下拉电阻,所以只需要将其加外部下拉和上拉电阻便可实现4种模式的选择切换,具体如图7所示。

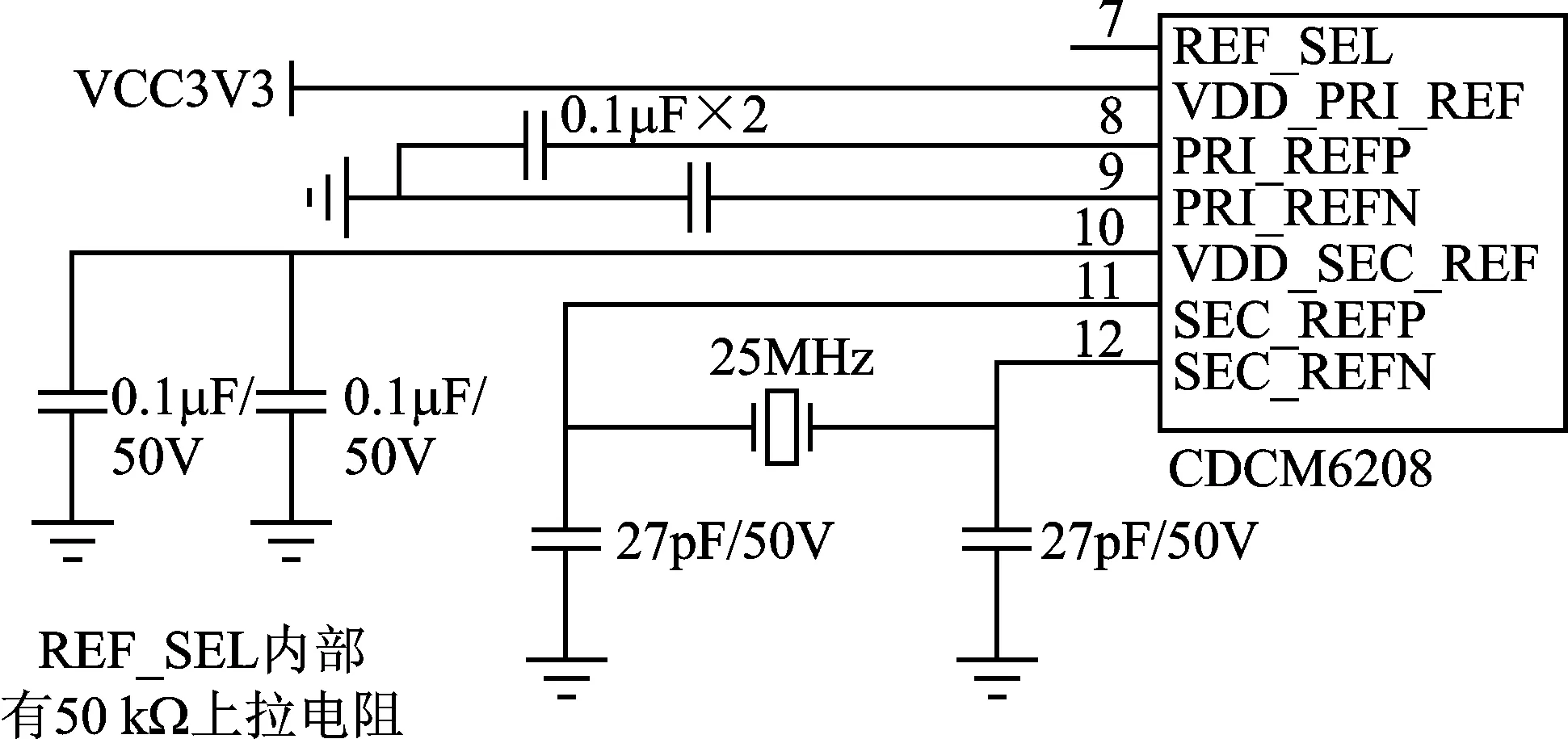

2.1.3外部参考时钟输入选择

在CDCM6208中,可通过REF_SEL引脚进行参考时钟源的选择:REF_SEL=0,选择VDD_PRI_REF作为参考时钟输入;REF_SEL=1,选择VDD_SEC_REF作为参考时钟输入,如图8所示,因为REF_SEL带内部上拉电阻,所以选择VDD_SEC_REF作为参考时钟输入。

图8 CDCM6208外部输入时钟设计

2.2编程配置

系统中CDCM6208时钟芯片的寄存器可由FPGA通过SPI接口进行编程配置。如图9所示,下面以这个典型应用为例设计出需要的差分时钟,如果假定SRIO的时钟为2.5 GHz,则FPGA的GTX时钟可为125 MHz,DSP的SRIO时钟可为156.25 MHz,这里DDR3的参考时钟为200 MHz。

图9 系统框图

根据式(1)和式(3),可以设定fPRE_REF=25 MHz,M=R=1,N=25,PS_A=4,PS_B=5,OY0=OY1=4,OY2=OY3=4,OY4=OY5=2.5,OY6=OY7=1.25,小数分频部分预缩放值为2。

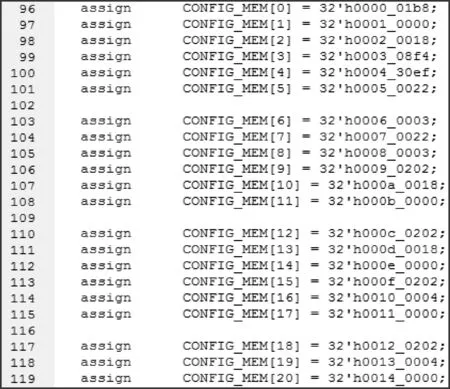

因此容易得到:fVCO=2 500 MHz,Y1~Y2=156.25 MHz,Y3~Y6=125 MHz,Y7~Y8=200 MHz。此外,这里假定所有输出的电平标准都为1.8 V,则CDCM6208的所有寄存器配置如图10所示。

图10 CDCM6208的寄存器配置

3实验验证

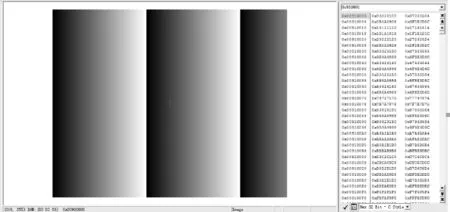

为了验证CDCM6208编程产生的高速差分时钟效果,在FPGA内模拟产生8位640×512的数据递增灰度图像,将产生的图像经过DDR3缓存一帧后,通过SRIO接口传输至DSP中显示,实验结果如图11所示,从图中可以看到图像无误码产生,证明CDCM6208编程产生的高速差分时钟非常稳定,适用于高速图像处理应用。

图11 实验结果显示

结语

参考文献

[1] 钟颖,张春侠,林玉野.基于DSP和 FPGA架构的嵌入式图像处理系统设计[J].电子设计工程,2011(12):21-24.

[2] 范超,赵琳,陈国.基于FPGA+DSP架构视频处理系统设计[J].电子技术,2014(6):52-54.

[3] 李二鹏,文开章,冯保红,等.石英晶体振荡器频率特性的测量与分析[J].测控技术,2010(1):81-83.

[4] 汪安民,韩道文.多核DSP的多路同步时钟信号设计[J].单片机和嵌入式系统应用,2014(5):15-17.

周全(硕士研究生),主要从事计算机辅助测试与传感器技术的研究;陈锡侯(教授),研究方向为计算机辅助测试技术与仪器应用。

Application of Programmable Clock Chip in High-speed Image Processing System

Zhou Quan,Chen Xihou

(Engineering Research Center of Mechanical Testing Technology and Equipment,Ministry of Education,Chongqing Key Laboratory of Time-grating Sensing and Advanced Testing Technology,Chongqing University of Technology,Chongqing 400054,China)

Abstract:With the image processing system for speed higher and higher,the stability and synchronization of the system clock are very critical,so one single clock crystal cannot meet with the high requirement any more.In order to solve this problem,a new type of programmable clock chip CDCM6208 is put forward,which can output multiplex differential signals.The output clock frequency of the chip can be adjusted by programming,that has the characteristics of stability,flexible and wide applicable scope.The actual effect is verified through the experiment in the image processing system.

Key words:high-speed image processing;differential clock;multiplexed output;programming control

中图分类号:TP336

文献标识码:A

收稿日期:(责任编辑:薛士然2015-12-29)