基于FPGA高速视频低压差分信号解码设计与实现

2016-06-23韦海成王淼军肖明霞

韦海成,魏 鑫,王淼军,肖明霞

(北方民族大学 电气与信息工程学院,宁夏 银川 750021)

基于FPGA高速视频低压差分信号解码设计与实现

韦海成,魏鑫,王淼军,肖明霞

(北方民族大学 电气与信息工程学院,宁夏 银川 750021)

摘要:针对高温和电磁干扰等复杂环境对高速视频低压差分信号解码能力的影响,提出了一种高可靠性的FPGA解码解决方案。通过改善板上阻抗匹配、提高解码模块所在单元供电稳定性、增加解码程序的约束条件等措施,将FPGA串行解码理论频率从280 MHz提高到316 MHz,提高了12.86%。实验表明,改进后的设计能够在55 ℃高温和大电磁干扰的复杂环境下对视频数据进行正确解码,实现稳定的图像显示。

关键词:FPGA;低压差分信号;解码设计;视频传输

随着技术的发展,平板显示器的显示分辨率和灰度级不断提高,显示器件和接口之间低成本、高速度、高可靠性的数字视频信息传输已成为当前视频传输研究的一个关键技术。

现有的各类视频设备中,传统的TTL或CMOS信号传输方式由于存在高噪声敏感、低传输速率和短传输距离等缺陷,已经不能满足现代显示设备的数据传输需求。因此,基于高速差分传输方式的低压差分信号接口(Low Voltage Differential Signal,LVDS)、数字视频接口(Digital Video Interface,DVI)、高清度多媒体接口(High Definition Multimedia Interface,HDMI)和显示接口(Display Port,DP)等接口编解码技术在视频显示领域得到了广泛的应用[1]。

这些现阶段被广泛应用的接口方式从本质上讲属于视频差分信号传输方式,都需要解决高速视频差分信号的解码问题。通过FPGA实现高速LVDS解码设计方案将为此领域相关技术应用和IC芯片设计奠定坚实的基础[2]。

本文将介绍一种基于FPGA的LVDS解码方案,该方案通过软硬件调试和改进,提高了在高温和大电磁干扰环境下的解码性能,实现了复杂应用环境下高速稳定的视频差分信号传输。

1高速视频LVDS解码设计

LVDS是一种电流模式驱动的数据传输方式,传输数据时采用3.5 mA的电流源驱动差分线对形成驱动电流,并通过100 Ω的终端电阻形成350 mV的信号,从而产生“1”和“0”的逻辑状态。这种传输方式具有极快过渡时间,最高理论传输速率可以达到1 Gbit/s[3]。

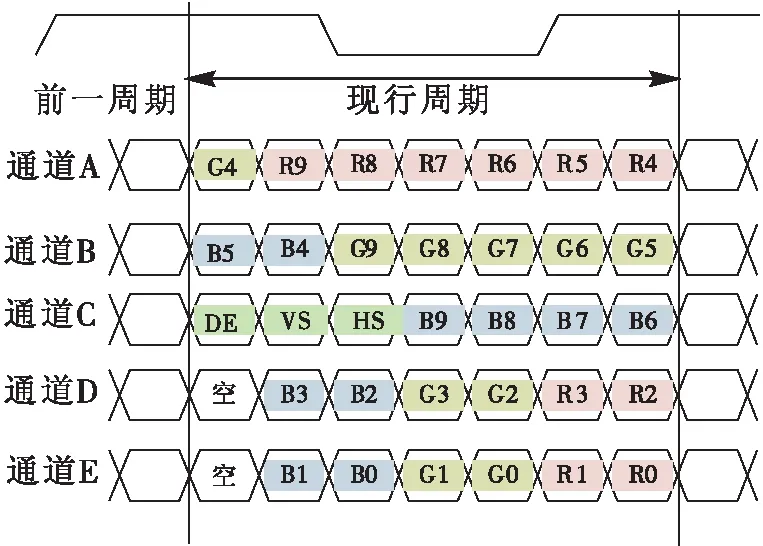

LVDS技术应用在视频传输领域时,为了节省传输线的数量,提高传输效率,信号的传输多采用多路复用的形式[4]。以10位1 024灰度级的高清LVDS解码电路为例,其工作时的视频时钟频率为75 MHz,按设定的LVDS一对差分传输线在一个时钟周期需要传输7个数据,见图1。每对LVDS传输线的数据传输频率必须达到525 MHz,由于传输过程中上下时钟沿均可进行数据传输,解码时钟频率需要达到262.5 MHz。因此,整个解码设计的关键就是要通过软硬件设计过程,解决高速数据传输过程中的误码问题,提高设计的健壮性,使得整个数据传输更为稳定。

图1 10位色彩深度的LVDS编码图

高速视频LVDS信号在硬件设计上需要解决电源的稳定性、差分走线的相似性以及板上阻抗匹配等问题。前期实验中发现,FPGA使用的芯片核心电压值、差分信号线的间距及长度、PCB走线的板上阻抗以及端接电阻的阻抗匹配等因素都会对LVDS解码产生影响。

例如,FPGA核心电压纹波必须小于5%;LVDS引脚所在BANK的电源和地附近需要增加滤波电容,保持供电的稳定性;LVDS差分信号必须走等长线;端接电阻的阻值需要和差分传输线阻抗匹配,并尽可能靠近接收端等。

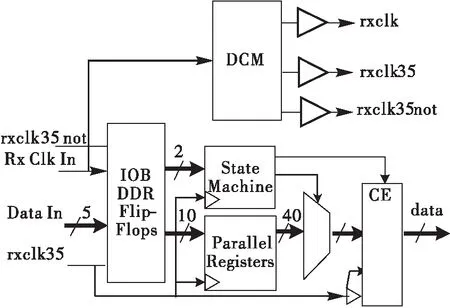

当硬件设计满足高速差分信号设计需求后,解码速度和稳定性提升的关键问题就在于FPGA的代码设计。LVDS接收解码模块主要由数字时钟管理、状态机、并行寄存器、DDR触发器等模块构成,见图2。

图2 LVDS接收解码模块

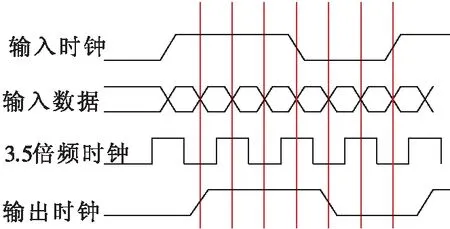

整个设计代码采用VHDL语言实现。解码过程首先将视频输入的75 MHz时钟频率作为基准,将此基准频率经过PLL模块3.5倍频后产生262.5 MHz的单端解码时钟。在此基础上,利用单端解码时钟将相应的5对差分输入的数据信号在串行输入单元中通过DDR触发器进行解码,形成单端数值信号[5],解码波形见图3。在获得时钟和数值信号之间时序关系后,经过并行寄存器的串并转换,形成75 MHz的35路并行数据。

图3 LVDS接收解码波形图

2高速视频LVDS解码测试

随着显示技术应用领域不断拓展,许多显示器件都要工作在高温、大电磁干扰的复杂条件下。因此,上述LVDS解码设计也需要将实际电路进行复杂的环境温度、共模和差模电压等条件下解码的可靠性和稳定性测试。

LVDS解码的环境温度实验系统构成主要包括VG835视频信号源、恒温箱、LVDS解码电路板以及平板显示器构成。实验中,环境温度通过恒温箱进行控制,恒温箱的温度从25~55 ℃,每次升高5 ℃并保持该温度10 min后进行显示图像稳定性测试,测试图像采用相邻像素变化剧烈的灰度渐变图像。采用该图案主要考虑该图像进行LVDS解码时,电路负载最大,解码过程容易出现错误,也就更能验证所设计解码系统的可靠性。

测试结果表明:当恒温箱环境温度为25 ℃时,所有解码过程均稳定正常;当温度不断升高达到50 ℃时,就会偶尔出现译码错误;当温度达到55 ℃时,译码错误增加,特别是图像的行、场同步信号译码错误增加,使得显示图像紊乱,图像出现纵向和横向的抖动,无法实现正常的显示。

LVDS解码程序的抗共模和差模电压干扰测试系统由码流仪、示波器、LVDS解码电路板以及平板显示器构成。测试在25 ℃环境温度下进行,使用全屏蔽信号线作为信号输入引线,并采用码流仪作为输入差分信号源,编码前时钟频率为80 MHz。

整个测试分两组,第一组保持通道共模电压1.2 V不变,以40 mV为间隔调整通道的差模电压,测试差模电压对解码的影响;第二组保持差模电压400 mV不变,以100 mV为间隔调整通道的共模电压,测试共模电压对解码的影响。

测试发现:当共模电压不变时,差模电压高于500 mV时,通道解码会出现错误;差模电压在400 mV以内时,时钟和数据信号之间存在1.3 ns的延迟。如果差模电压不变,共模电压上升到1.6 V时,会出现解码错误。

3高速视频LVDS解码测试结果分析

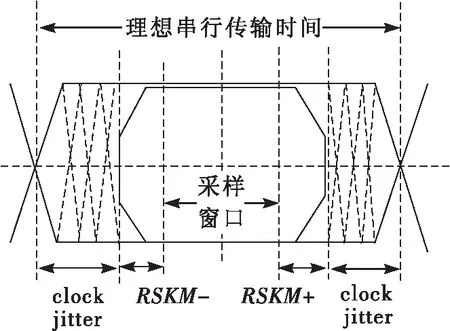

分析上述实验中环境温度和电压变化使得解码出现错误的主要原因在于接收过程中的时序接收偏移余量(RSKM)受到了环境的影响变差。

FPGA内部的解串器要在单位间隔时间窗口正确采集输入数据时才能够正确解码,即通过LVDS输入的时钟产生定时选通信号,通过该信号来进行信号采集。

而实际上,LVDS输入的数据和时钟信号受到环境影响在每个时钟周期的波形都会有差异,这种信号周期性的差异积聚起来就形成了一定的偏移范围,即时钟偏移量(Clock Jitter)。要保证解码时采集的数据正确,就必须满足数据窗口内时钟信号采集数据所需的建立和保持时间,保证数据和时钟边沿对应关系尽量稳定,使得数据在采样窗口内被正确采样,见图4。

图4 串行传输的时钟沿采样过程

理想情况下,该时钟选通信号位于数据脉冲的中间,不会出现误码现象,在复杂环境条件下,内部和外部条件会使抖动增加,RSKM靠近采样窗口的关闭点,从而产生数据误码。

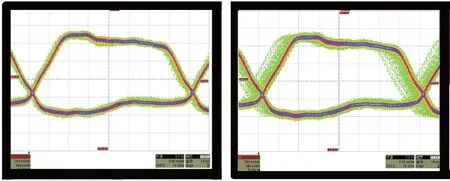

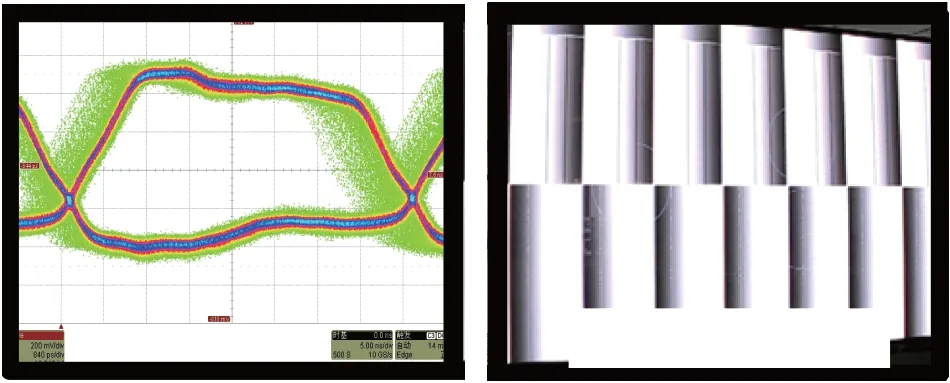

为了进一步分析上述结果,实验采用示波器对信号的时钟和数据时序关系进行了眼图分析。眼图可显示每个时钟周期数据波形的瞬间值并累计显示,各周期波形叠加后会在眼图中形成眼孔。在无抖动噪声和电平变化理想情况下,波形无失真,眼孔开启得最大。当电平变化时,波形出现失真,引起眼孔闭合。因此,眼孔开的大表示信号的幅度和时间余量能够满足要求,如果眼孔变窄,则表明信号抖动大,误码率上升。通过测试眼图就可以分析高速传输数据的质量和RSKM。

以环境温度变化为例,眼图测试结果如图5 所示:在温度从25 ℃不断升高过程中,眼图开启情况不断变化。环境温度为30 ℃时,几乎看不到信号的抖动,测试的信号没有解码错误(图5a);环境温度上升到50 ℃时,可以看到信号抖动增加,测试信号偶尔就会出现解码错误(图5b);环境温度上升到55 ℃时,信号抖动加剧,被测的视频信号出现了大量的解码错误(图5c)。此时,显示图像画面出现了剧烈的抖动(图5d)。同样,差分信号的共模电压和差模电压变化也会在眼图上产生相应的变化。

a 30 ℃眼图 b 50 ℃眼图

c 55 ℃眼图 d 解码不正确的图像图5 不同温度下LVDS眼图及显示图像

4实验改进后结果

上述实验表明,采用基于FPGA的LVDS解码进行复杂环境下高速视频信息传输时,环境温度、差模和共模信号的幅度变化等环境因素均有可能引起解码错误。

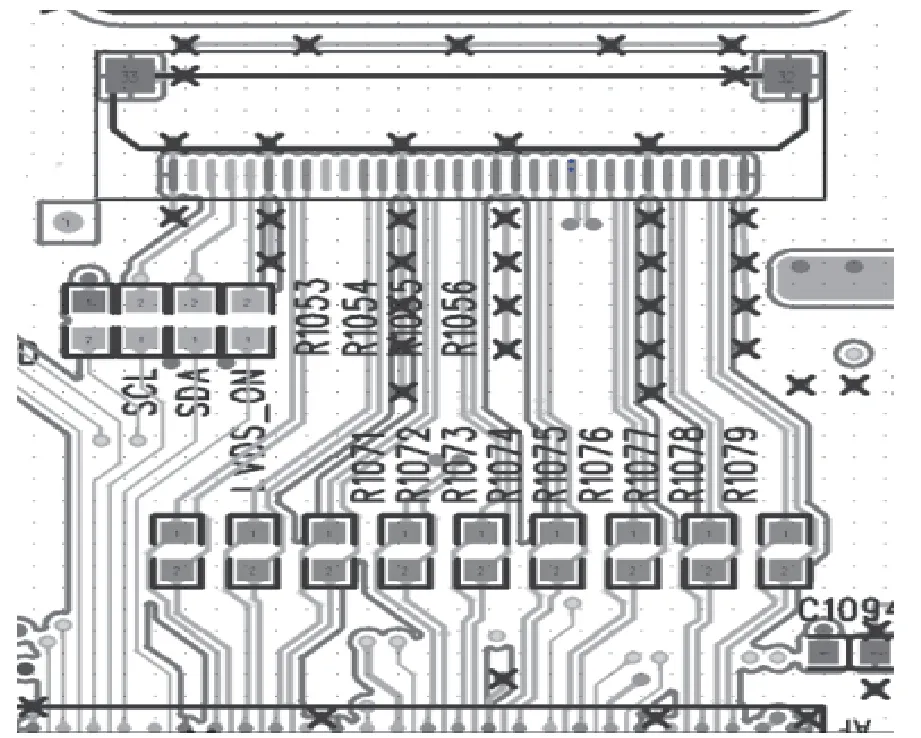

为了进一步提高解码的正确率和稳定性,本文主要从以下方面进行了改进:硬件方面,调整信号采用差分线路布线时所使用的分布电阻,使得板上阻抗匹配;增加FPGA在解码模块周围的电容,减少电源纹波对解码的影响;对传输线增加了上下拉电阻调整共模电平,尽量张开眼图;对所有信号传输中不使用的管脚进行虚地处理,以增强FPGA的接收能力。整个修改见图6。

图6 10位LVDS硬件电路设计(照片)

软件方面,加强了编译时的时序约束条件,并调整相关的管脚设定,使得整个解码过程的布局布线更符合时序要求。

通过上述处理后,整个芯片的理论解码频率从80 MHz提升到90.3 MHz,即可以将差分信号的传输频率从280 MHz提升到316 MHz,设计支持的频率提升了12.86 %,见图7。

图7 新的设计约束后理论解码频率

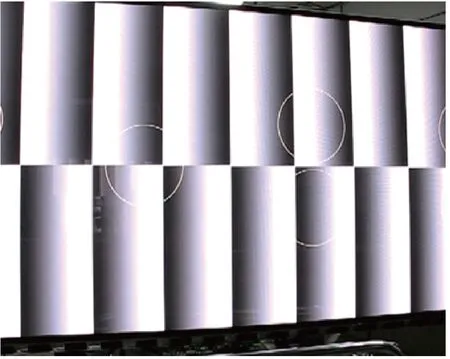

设计修改后,再次进行复杂环境下的实验。实验结果表明,新的设计能够稳定地工作在环境温度为55 ℃情况下。相对于原先设计,信号的共模电压提高了100 mV,差模电压提高了40 mV,没有任何解码干扰出现,见图8。

图8 55 ℃显示正常的测试图像

5结论

随着现代社会发展,显示终端的应用越来越广泛,这就对复杂环境下的显示信号的传输提出了挑战。为了实现高分辨率显示设备在高温、强电磁干扰环境下的正常显示,需要解决高速视频低压差分信号在复杂环境下解码的可靠性和稳定性问题。本文设计了一套稳定的LVDS解码软硬件解决方案。通过改善电路板阻抗匹配、增加约束条件,将理论传输解码频率从280 MHz提高到316 MHz,提高了12.86%,将视频时钟传输频率从80 MHz提高到了90.3 MHz,实现了视频信号在55 ℃高温、强电磁干扰环境下高速稳定的传输,提高了显示设备的应用范围。

参考文献:

[1]贾培勇, 朱春光. DisplayPort 数字接口及发展趋势[J]. 电视技术, 2007, 31(11): 60-63.

[2]杨佩, 张丽娜, 张洵颖, 等. LVDS 中 8B/10B 编码解码器的设计与实现[J]. 微电子学与计算机, 2014, 5(31):41-44.

[3]张飙, 徐和飞, 牛秦洲. LVDS 接口 LED 显示屏数据处理系统设计[J]. 液晶与显示, 2008, 23 (6): 736-743.

[4]杨磊, 任龙, 刘庆, 等. 基于 FPGA 的大视场图像实时拼接技术的研究与实现[J]. 红外与激光工程, 2015, 6 (44):1929-1935.

[5]袁金保, 杜亚军, 杨雪松. 超大容量视听媒体综合处理设备中的关键技术[J]. 电视技术, 2014, 38 (20): 51-54.

韦海成(1974— ),博士,研究生导师,主要从事视频显示技术研究;

魏鑫(1992— ),硕士生,主研FPGA硬件设计及实现技术;

王淼军(1989— ),硕士生,主研FPGA软件设计及实现技术;

肖明霞(1978— ),硕士,副教授,主要从事视频图像处理技术。

责任编辑:闫雯雯

Design and realization of low voltage differential signal decoding based on FPGA

WEI Haicheng, WEI Xin, WANG Miaojun, XIAO Mingxia

(SchoolofElectricalandInformationEngineering,BeifangUniversityofNationalities,Yinchuan750021,China)

Abstract:In order to solve the influence of complex environment such as high temperature and high electromagnetic interference on low voltage differential signal decoding, a method of high reliability of FPGA decoding is proposed. The impedance matching of the board and the stability of power to decoding module is improved, the time constraint of decoding module is increased. The experimental results show the decoding frequency of FPGA is improved from 280 MHz to 316 MHz, which is improved about 12.86%, temperature of correct decoding is improved to 55 ℃, and the display is stable.

Key words:FPGA;decode; LVDS; data transmission

中图分类号:TN919.8

文献标志码:A

DOI:10.16280/j.videoe.2016.02.012

基金项目:国家自然科学基金项目(61461001); 宁夏自然科学基金重点项目(NZ13083); 2015年度北方民族大学基本科研项目(2015JBK361); 北方民族大学国家自然科学基金前期培育项目(2013QZP09)

作者简介:

收稿日期:2015-08-23

文献引用格式:韦海成,魏鑫,王淼军,等.基于FPGA高速视频低压差分信号解码设计与实现[J].电视技术,2016,40(2):65-68.

WEI H C, WEI X, WANG M J,et al. Design and realization of low voltage differential signal decoding based on FPGA [J].Video engineering, 2016,40(2):65-68.