基于BIST的SRAM型FPGA测试技术分析

2016-06-18张灏曹亮上海航天电子技术研究所上海201109

张灏 曹亮 上海航天电子技术研究所 上海 201109

基于BIST的SRAM型FPGA测试技术分析

张灏曹亮上海航天电子技术研究所上海201109

【文章摘要】

深入研究和探讨FPGA芯片测试技术,这是生产者确保制造出高效可靠芯片的重要前提。因为FPGA具有可重复的编程性,这种方法在编程中,将在FPGA内部资源共同划分成为多个不同的内建自测试模块,通过多次配置和测试,对各个BIST模块测试路径进行更换,从而达到完全测试FPGA内部资源的效果。

【关键词】

BIST;SRAM型;FPGA;测试技术;分析

根据BIST思想,给出对FPGA之中CLB资源与互连资源同时展开检测故障和诊断故障的方法。在GIST测试向量发生器之中,输出相应分析器和GIST控制器之中,都利用了FPGA之中的CLB资源进行实现,在完成测试之后,可将这部分资源通过编程将其作为工作电路,这样就会减少成本。

1 SRAM中FPGA结构

SRAM型FPGA结构单元共由1个CLB模块、1个开关模块、2个直接与CLB相连接的局部连线模块所共同组成。其中CLB模块由三部分共同组合,即查找表、D触发器和多路复用器;局部互连线由两部分组成,即连接块、导线,其连接块内包括控制信号进出、CLB可编程互联点开关、可编程多路复用开关; SM为全局互连资源的关键一部分,SM由两部分组成,即导线、可编程十字点开关。

2 故障类型

目前,文中检测和诊断故障类型包括四种,即:线路开与关故障、固定开与关故障、测试延时路径故障。

①固定开与关的故障:通常情况下,在局部互连线的MUX-P导通晶体管与PIP-PS之中,在发生固定故障时,不管是SRAM为何值,导通晶体管宗师保持着一种固定开与关的形式;

②线开与短路的故障:通常在SM中发生,在SM导向部分出现断路,或者出现开路故障、SM导线间发生桥接,这都有可能出现线路故障。在PCP-PS之中,如果出现定关/开的故障,会致使出现开/短路故障。

③固定的0/1故障:这种故障通常都会出现在LUT之中,表现在LUT存储单元并未能存储出相应的数据;

④在CLB传播路径中,会出现延时故障。

在FPGA之中,这四种故障类型已经覆盖了将近百分之九十的故障类型,因此,深入测试这四种故障类型具有现实的作用。

3 配置测试

在全局连线资源中,应配置SM中PCPPS开关,并设置出与之相关的导线展开测试,并不需要利用任何一种CLB资源。在局部CLB与互连线相互连接,因此,在局部互连测试之前,CLB之前应是测试电路中一部分。局部互连测试也是与相关的CLB施加测试向量过程中,然后在对CLB输出响应进行分析。

对PCP-PS之中的PIP-PS展开分析,应用三种不同形式的测试配置,这样就能让SM得到更全面的测试,在CLB测试和局部互连线测试之中,因为它们之间编程开关其本质普遍是PIP-PS,因此采用这三种配置形式,除了对测试SM之外,也应对局部互连线和CLB展开测试。

4 BIST的具体测试方案

4.1设计测试方案

以10个CLB资源共作为1个测试模块,其在同一行之中相邻的2个测试模块,应共有利用1个TPG。为了能够测试整个FPGA,应对全部CLB资源都应进行设计。

4.2测试模块的设计

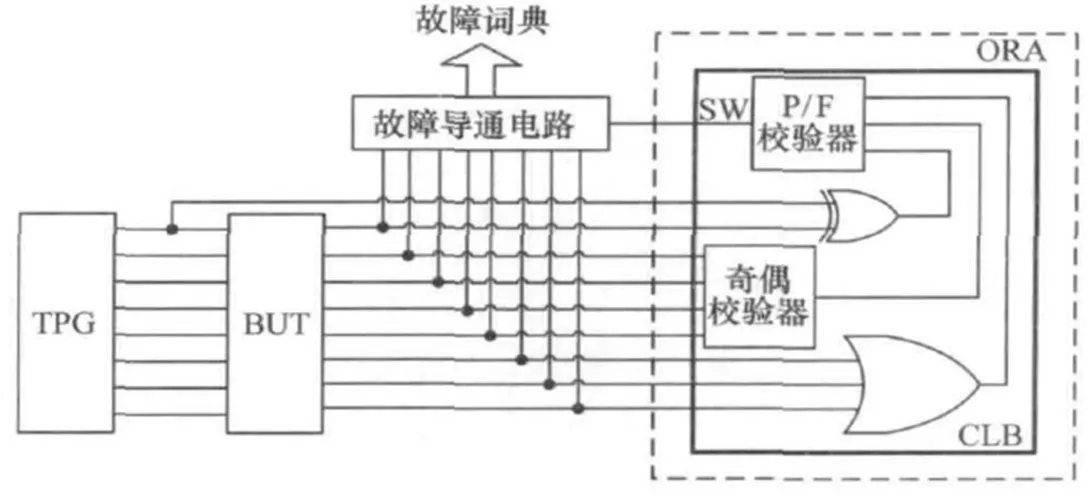

图1为一个设计方案中的测试模块结构图

如图1中,其TPG中可应用设计可控测试向量发生器的方法,如图1为ORA内部结构图,共包括两输出XOR。

图1 测试模块结构图

P/F校验器相当于一个门,在BUT输出出现故障时,很容易产生P/F信号,开启故障导通电路。如下为P/F布尔表达式:

其表达式为:SW=(bι-1⊕bι)∪(b1⊕b2⊕ b3⊕b4⊕bxro_4) ∪(b5+b6+b7)

式中,BUT的原始输出为bι(ι=0,1,2,……,7);BUT第1位输入的值为 bι-1; bι为BUT第1位输出的值,也就是bι是bι-1经过B UT最终输出结果; bxro_4是奇偶效验器的输出。

上述式子表现出在BUT中只要出现故障,P/F校验器便可以形成一个触发信号SW,将输出结果全部收入到故障词典之中。然后将整个诊断结果在校准电路输出之中,在FPGA外部充分显示出,这样才能实现对整个FPGA器件进行故障诊断。

5 测试程序

在所给定的GIST方法之中,将整个FPGA芯片编程作为多个测试模块,其每一个测试模块都由三部分组成,包括ORA、BUT、TPG。其中整个FPGA测试都应运用三种TC模式,应用不同的测试路径。在测试方案各个测试模块都已经完成测试之后,各测试模块之中被编程为CLB资源或者是ORA。在此基础上,实现对FPGA进行测试。如下为具体测试步骤:

5.1编程的配置

在FPGA编程构造由多个测试模块构成,其运用硬件语言编程会生成测试方案进行自动射击,其展示的分模块化设计由TPG模块、BUT模块和ORA模块共同组合而成。

5.2测试路径

在全部的TC测试路径之下,都是由1根线对全局互连线开路故障进行诊断,其中4根线主要利用在诊断CLB故障,还有3根线被用在短路故障诊断之中。

5.3检测故障

如下为FPGA故障检测的过程:

①全局互连线的故障。将TPG中第1位输入恒置为“1”,在出现开路故障,或者门输出恒是“1”。则检测开路故障。

② 局部互连线固定开/关的故障。在LUT与局部互连固定故障中,可经过在图1中奇偶校验器进行检测,在图2之中可知其4个CLB测试路径是同样的。也正是因为配置方式是相同,因此CLB和局部互连方式也是相同的。

③延时故障的检测。在BUT电路之中,施加出一个变化的触发沿,在预定时钟周期之内检测出此变化触沿是否有故障。

④全局互连线路,在设置测试向量中,让BUT与ORA接入,或者门的3位数据为“000" 。

5.4故障诊断

在ORA中,与测试方案BIST控制器共同组合完成。

将各个测试模模块之中,编程成为BUT中CLB资源编程为ORA,也可编程成为TPG,编程成为TPG或者是ORA中的CLB资源,可相应的转变成BUT,这样完成了整个FPGA测试。

6 结语

总而言之,经过12次配置芯片,这样就可以对FPGA中多种连线通道延时故障、开/短路故障,在编程开关过程中固定的开/关故障,查找表中稳定的0/1故障,很容易发现其故障覆盖率已达到100%。但FPGA测试技术在应用中还有很多不完善之处,还需要深入进行研究和分析。

【参考文献】

[1]谷銮,徐贵力,王友仁.FPGA动态可重构理论及其研究进展[J].计算机测量与控制,2007,(11).

[2]吕小巧.一种基于FPGA的改进遗传算法硬件设计研究[D].江西理工大学,2010.