基于多核处理器的弹载计算机低功耗设计研究

2016-06-02景德胜中航工业西安航空计算技术研究所陕西西安710068中国民航大学适航学院天津300300

景德胜(1.中航工业西安航空计算技术研究所,陕西西安710068;2.中国民航大学适航学院,天津300300)

基于多核处理器的弹载计算机低功耗设计研究

景德胜1,2

(1.中航工业西安航空计算技术研究所,陕西西安710068;2.中国民航大学适航学院,天津300300)

摘 要:低功耗是嵌入式计算机的发展趋势,是弹载计算机设计要解决的关键问题。以基于多核处理器的弹载计算机为例,介绍了功率消耗产生的原理,从处理器、软件设计、Cache设计和可编程逻辑设计等方面对影响弹载计算机系统功耗的因素进行了分析,并提出了低功耗设计的方法和技巧。

关键词:多核;弹载计算机;嵌入式系统;低功耗

0 引言

弹载计算机是实时嵌入式系统,用于接收、处理导引系统的信号,控制导弹飞行实现对攻击目标的检测、捕获和跟踪,是导弹制导系统的关键组成部分。随着技术的发展,新一代导弹要具备攻击高速、高机动目标的能力,具备全方位攻击的能力,同时对导弹的探测能力、反隐身和抗干扰能力都提出了更高的要求,使得弹载计算机需要处理的数据复杂度越来越大、实时性要求越来越高。

弹载计算机因应用环境特殊,安装在导弹狭小的制导舱内,发射后由导弹上电池供电,对系统功耗和产品尺寸提出了严格要求。高性能、低功耗成为实现弹载计算机功能需求的基础。基于单片异构体系架构的多核处理器以其优越的处理性能、灵活高速的存储结构和丰富的对外接口很好地解决了弹载计算机对高性能的要求,因此如何通过改进弹载计算机软硬件设计降低系统功耗,成为系统设计中需要研究和解决的重要问题。

1 影响功耗的因素

低功耗设计技术大致可以分为两类:静态技术和动态技术。静态技术是指从系统构造、工作原理方面着手,降低系统功耗,如选用低功耗器件,采用异步电路体系设计等;动态技术是通过改变系统的运行行为来达到降低系统功耗的目的,如在系统工作过程中,根据运行状况将器件从工作状态转入睡眠状态。弹载计算机由印制电路板、元器件和软件等组成,主要功耗由元器件中的集成电路产生。

CMOS反相器[1]是集成电路的重要组成部分,是所有集成芯片设计的核心,逻辑门、加法器、乘法器和微处理器等比较复杂电路的电气特性都可通过分析组成其CMOS反相器的特性得到,然后通过逻辑门和加法器等部件特性来分析处理器等的特性,CMOS反相器对分析集成电路延迟时间和功耗有重要意义。

图1 CMOS反相器原理图

图1是一个静态CMOS反相器的电路图,晶体管是一个具有无限关断电阻和有限导通电阻的开关。当Vin为高并等于VDD时,NMOS管导通、PMOS管截止,见图2(a)等效电路,此时输出Vout为0 V;当Vin为低等于0 V时,PMOS管导通、NMOS管截止,见图2(b)等效电路,此时输出Vout为高电平VDD,由此达到反相器的功能。

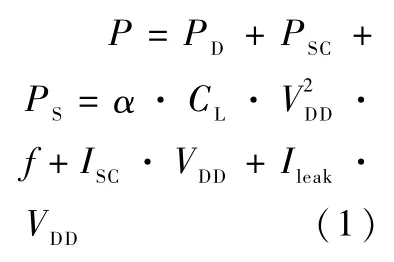

CMOS反相器的功耗包括动态功耗、静态功耗和短路功耗等三部分,总功耗组成见式(1)。

其中:PD是动态功耗,与电源电压VDD、负载电容CL、工作频率f和开关活动率α相关;PSC是短路功耗,在输入电平处于VTN至(VDD+ VTP)范围内时会使CMOS电路中的PMOS和NMOS晶体管都导通,产生短路电流ISC,从而引起开关过程中的附加短路功耗,短路功耗与(VDD-2VT)有强烈依赖关系;PS是静态功耗,理想情况下CMOS电路的静态功耗是零,但实际处于截止态的MOS晶体管存在泄漏电流Ileak,会引起一定静态功耗。在集成电路中,动态功耗是整个CMOS集成电路功耗的主要组成部分,占到90%以上,静态下漏电流所产生的功耗占总功耗的比例不足1%,几乎可以忽略。

图2 CMOS反相器开关模型

除集成电路占主要功耗外,有源开关器件在状态转换时,其纯电阻元件上、非理想元件等效电阻和印制板中连线等在工作中也会消耗一定能量。

2 低功耗设计技术

以使用TI多核处理器TMS320C6678的弹载计算机为例[2]。TMS320C6678整个系统由TeraNet将8个内核、网络协处理器、共享存储管理器、多核导航器、外设及其他功能部件连接起来,处理单元由8个相同的内核组成,互连网络TeraNet为分层结构的总线形式,且内核通过共享存储管理器共享容量为4 MB的共享存储器,从体系结构上看类似于并行计算机中的对称多处理机(SMP),该架构支持8位、16位、32位、64位、128位和256位数据,可根据功耗和性能等因素折中选择。

2.1软件设计

为了在有效发挥多核处理器系统的运算处理和数据传输能力的前提下,降低功耗,获得多核处理器实际应用时的最佳性能,要根据实际任务需要,考虑每个内核之间的任务分配和信息传输[3]。多核处理器任务执行主要有两种运行方式:主从方式和数据流方式。主从方式即一个核管理主任务,由主任务对其他核任务进行管理;数据流方式即任务按照数据的传输来运行,由一个任务推动另外一个运行,见图3。主从方式7各个内核工作情况差异较大,在完成相同任务情况下,无法通过降低整个处理器的时钟频率来降低处理器功耗;数据流方式每个内核工作情况比较统一,实时性高,与主从方式相比可适当选用较低的时钟频率,降低整个处理器的功耗,但数据流方式要求对整个任务的协同和并行工作流程非常清晰。

图3 基于多核处理器软件工作方式

软件设计中尽量使用中断方式代替查询方式,中断方式下处理器可以什么都不做,甚至可以进入等待模式或停止模式。而在查询方式下处理器必须不停地访问寄存器,造成很多额外功耗。用宏代替子程序,读RAM会比读FLASH带来更大功耗,处理器在调用子程序时,需要先保存现场,调用完毕后再恢复现场,弹栈压栈至少带来2次对RAM的操作,在编译宏时会展开,处理器执行时只是顺序执行指令,避免了弹栈压栈操作,且片内FLASH的大小完全可以满足编译后代码量的增加,编程时工作量几乎相同,低功耗性能突出的ARM在处理器设计上仅允许一次子程序调用。对于非必须实时计算的参数,使用常量或查表的方式替代处理器的实时计算。使用移位运算来代替乘除法运算等也可有效降低处理器的功耗。

2.2Cache设计

数据的时间和空间局部性是内存系统优化设计研究的重要部分[4],核心问题在于内存结构的优化无法适应每个应用程序。不同研究者关于Cache参数对处理器性能及功耗影响的相同分析结论为:Cache面积增大会降低失效率,但功耗会随之增大;减小Cache面积带来的高失效率和较大时间延迟依然会使整个系统功耗上升;增加Cache组相联度会增加Cache命中率,进而可以降低功耗。因此采用相关优化算法让Cache在运行时动态可重构,可取得较优的效能。弹载计算机应用程序一旦确定,执行相对单一和固定,考虑到弹载计算机的可靠性和执行任务的特点,对不同Cache空间的大小和组数的执行应用程序进行命中率仿真测试,根据仿真结果配置合适的Cache空间和组数,可降低Cache消耗的功率。

2.3可编程逻辑设计

可编程器件的选择对功耗影响较大[5],例如寄存器传输级(RTL)器件比门级器件可以减少更多的功耗。RTL级的转换可以在一个周期内判断出电路正在计算结果的部分是否为有用操作,被判定为在一个时钟周期内进行无用操作的时序或组合电路会被采用的门控时钟或睡眠模式关闭。可编程逻辑设计时,降低逻辑电路的时钟频率,仅保留必须在高速时钟域运行的逻辑电路;保持较小的逻辑电路面积,对无速度要求的逻辑电路进行优化设计;将电压降低到数据手册规定的最小值;避免I/O管脚上拉、下拉冲突等方法也可达到降低功耗的目的。

2.4 印制板设计

印制电路板是电子元器件的支撑体,是电气连接的提供者。为了降低在印制板上的功率耗散,印制板设计在满足电气连接的稳定性、电磁兼容和布局合理等要求的前提下,要对信号的走向及电源和地线网络进行整体规划,布线时要求走线尽可能短,线宽要根据器件本身和周边器件的情况进行考虑,尽量宽,走线拐角最好大于90°,尽量设计为具有一定尺寸的均匀圆弧线,相邻两面走线应避免相互平行,以减少寄生电容耦合。

2.5 其他设计

集成电路未使用引脚的处理方法也会影响功耗的差异[6],例如在集成电路未使用输入引脚上极易产生电荷积累,根据公式U=Q/C,式中Q为电量,C为电容,U为电压,当累积电荷达到一定程度时,就会产生影响输入引脚状态的电压,输入引脚逻辑状态变得不可控,当电平处在逻辑0和1的过渡区时,CMOS反相器的NMOS管和PMOS管都会导通,这将带来很大的功耗浪费,因此一定要对集成电路的未使用引脚进行上拉或下拉处理,此种处理方法也可使未使用的引脚处于一个固定逻辑状态。

3 总结

低功耗对弹载计算机十分重要,相关设计研究众多,随着处理器技术的发展,研究对象逐渐以基于多核处理器的弹载计算机为主。各种低功耗设计在弹载计算机上应用形式多样,但主要集中在体系架构设计、低功耗元器件的选用、供电管理和软件优化几个方面。体系架构设计应以异步设计为主,对性能和时序要求严格的部分采用同步设计;选择采用高K/金属栅和动态阈值等技术的CMOS器件,是降低功耗的最直接办法;选用具有电源调节或低功耗模式的处理器等器件,可在不增加太大工作量的情况下,通过供电管理的方式降低功耗;软件的设计优劣对整个弹载计算机的运行十分重要,合理调节各个部件的运行状况,在满足性能要求的情况下可通过减少电路的活动时间降低功耗。

弹载计算机应用对象特殊,对性能、可靠性和实时性等有非常严格的要求,弹载计算机是否能良好工作直接决定导弹执行任务的成败,因此设计者必须根据实际应用要求剪裁使用低功耗设计技术。

参考文献

[1]RABAEY JM.数字集成电路—电路、系统与设计[M].周润德,译.北京:电子工业出版社,2010.

[2]汪安民,张松灿.TMS320C6000DSP实用技术与开发案例[M].北京:人民邮电出版社,2008.

[3]王江.多核系统中提升启动速度之策略[J].电子技术应用,2014,40(3):25-28.

[4]何勇,肖斌,陈章龙,等.一种低功耗的动态可重构Cache设计[J].计算机应用与软件,2009,26(8):247-250.

[5]张伟栋,李涛.一种基于FPGA的高集成度技术研究设计[J].微型机与应用,2015,34(4):11-13,25.

[6]张兴,杜刚,王源,等.超低功耗集成电路技术[J].中国科学,2012,42(12):1544-1558.

景德胜(1985 -),男,本科,工程师,主要研究方向:弹载嵌入式计算机。

引用格式:景德胜.基于多核处理器的弹载计算机低功耗设计研究[J].微型机与应用,2016,35(10):28-29,32.

Research about low power design ofmissile-borne computer based on multi-core processor

Jing Desheng1,2

(1.Xi'an ACTRI,AVIC,Xi'an 710068,China;2.College of Airworthiness,CAUC,Tianjin 300300,China)

Abstrac t:Low power consumption is the development trend of embedded computer,and the key issue to be resolved in the design ofmissileborne computer.This paper introduces the elements which cause power consumption,analyzes the factors of power consumption from processor,software design,Cache assign and so on,and describes the methods and tactics about the low power consumption system design.

Key words:multi-core;missile-borne computer;embedded system;low power

作者简介:

收稿日期:(2016-01-25)

中图分类号:TP368.1

文献标识码:A

DOI:10.19358 /j.issn.1674-7720.2016.09.010