一种数字遥测接口容差测试方法及实现

2016-06-01安卫钰韩笑冬王志富

安卫钰 韩笑冬 王志富

(中国空间技术研究院通信卫星事业部,北京 100094)

一种数字遥测接口容差测试方法及实现

安卫钰 韩笑冬 王志富

(中国空间技术研究院通信卫星事业部,北京 100094)

通过对卫星常用数字接口电路及其传输特性分析,研究了影响接口传输性能的时延、幅值和上升沿特性,提出了一种数字遥测传输接口容差测试方法并研制了测试设备,可以对数字信号进行时延、电平幅值和上升沿的拉偏,实现了接口容差指标的定量测试。通过对卫星单机设备接口拉偏试验,验证了测试方法的正确性和测试设备的实用性。

卫星;数字接口;容差;测试方法

1 引言

卫星从研制到发射,须要经过多个阶段的测试验证,由于各阶段的环境温度和电缆规格不同,会使单机设备间的数字传输接口发生不匹配现象,影响遥测遥控信息的正常传输。尤其是设备热试验期间,由于环境温度的剧烈变化,信号的传输特性随之变化,时序竞争现象时有发生,使单机间无法正常通信,影响卫星完成任务。

对接口电路容差指标进行分析和测试,提高接口在极限环境下的工作性能,可以有效地保证整星信息流的正常传输。国内外均对电路容差进行过研究分析,通过提取关键特性参数,使用仿真工具分析系统累积误差,然后运用数字化技术进行迭代设计,提高系统的设计裕度[1-3]。但是这些方法只适用于设计阶段,无法对硬件进行实测,由于仿真工具的理想化,实际电路与设计值存在偏差。本文提出了一种对数字遥测电路容差定量测试的方法,适用于遥测视频信号接口和RS422差分接口,通过硬件设备对电路关键特性参数进行拉偏测试,模仿多种工况下星上设备单机接口的传输性能,可在整星集成测试前发现潜在的接口不匹配现象。

本文对容差测试机理进行了研究,分析了传统容差分析方法的利弊,论述了接口容差测试设备的实现原理和关键技术,通过该设备对星上单机设备的验证试验,论证了测试方法的有效性。

2 容差分析与测试原理

目前,通用的容差分析方法是计算各种工况下电路的性能参数、输入量和元器件参数之间的关系,使用仿真软件对电路进行最坏情况分析或蒙特卡罗分析[4],求出电路输出性能参数的偏差范围,找出对电路敏感度影响较大的参数并进行控制,使电路满足要求。如性能参数较差则修改电路设计,重新进行容差分析直到满足指标要求。但是单机一旦生产完成后,缺少容差指标验证方法,由于仿真工具中元器件的参数与实际值会有偏差,导致单机实际状态与仿真设计的理想电路有差异,在环境恶劣情况下会发生接口不匹配现象。

为了实现对卫星数字接口的容差测试,本文提出了容差定量测试的方法,须要研制测试设备对特定接口电路进行最坏情况试验。对模拟数字遥测传输信号,进行时延拉偏、电平拉偏和上升沿拉偏,时序拉偏精度20ns,幅值拉偏精度50mV,上升沿拉偏精度100ns,接口正常工作时拉偏参数的上下限即为接口的容差值。通过多路信号比较分析,可以对多路信号之间的时序关系进行测试。

以图1所示的一种典型的数字遥测传输接口时序为例。门控信号有效时在时钟的下降沿采集数据信号,理想情况下门控和时钟信号的上升沿是对齐的,实际情况下两个信号到来时间并不是对齐的,信号的上升沿、幅值也略有不同,不同的工况会使数据采集电路进入不同的逻辑状态,引起数据传输的不稳定。容差定量测试方法可以对电路进行最坏情况试验,使被测电路处于温度、信号电压、上升沿和延时等主要因素均为上下限的条件下,测试电路性能参数偏差。

3 测试设备实现方案

3.1 系统方案

测试设备是基于现场可编程门阵列(FPGA)和数字信号处理器(DSP)相结合的嵌入式硬件平台[5],设计了专用时延、幅值和上升沿的拉偏电路,利用上位机(PC机)软件控制电路拉偏参数。

为了实现对接口信号的拉偏,须要对信号进行多级处理。在FPGA中通过内部处理逻辑生成标准时序信号,并接收DSP传送的拉偏设置参数,根据时延拉偏参数对多路信号的时序关系进行调整,以时钟同步信号为基准,调整其它信号与时钟同步信号之间的延时量(可超前或滞后),FPGA通过外部输出接口将信号送出,此时信号幅值为3.3V。接着对信号进行幅值转换,达到与星上设备接口匹配和幅值拉偏的目的。最后,对接口信号的上升沿时间进行调整,通过可变阻容网络实现。测试设备原理如图2所示,主要由上位机、控制管理模块、信号幅值转换模块、阻容网络模块、锂电池、精密时钟基准源等组成。

上位机与DSP通过隔离串口总线通信,它提供用户操作界面,用于设置系统工作模式、拉偏参数、显示接收数据等功能,分为配置和工作模式。运行在配置模式时,进行接口类型的选择和拉偏值设置,将配置信息发送给控制管理模块,控制管理模块响应并回传,上位机对回传数据进行判断,正确后发出开始执行指令。运行在工作模式时,进行数据双向收发,同时接收控制管理模块传来的遥测数据和向控制管理模块发送指令数据。

3.2 时延拉偏方法

控制管理模块实现系统的核心功能,使用FPGA模拟数字量接口时序并对不同信号之间的延时关系进行调整;DSP完成与上位机的通信,将配置信息发送给FPGA处理。FPGA使用XILINX公司Spartan 6芯片XC6SLX100,外部时钟采用稳定度为1×10-6的恒温晶振[6],频率为50MHz。

接口的时延拉偏在FPGA中实现,FPGA内部采用级联方式:第一级根据具体的通信协议,为信号设置状态机,产生时钟信号与门控信号对齐的时序。时钟由FPGA内部的直接数字式频率合成器(DDS)产生,频率控制字位宽为32bit,按照上位机设置的时钟频率,计算出DDS模块的频率控制字,得到规定频率的时钟信号。门控信号的周期为1024个时钟周期,高电平持续时间为第M到第N个时钟周期(M和N可由上位机设置),对时钟从0开始计数,门控信号状态机初始态输出为0;计数达到M时,在时钟的上升沿门控转入输出为1状态;计数达到N时,在时钟的上升沿门控转入输出为0状态;计数达到1024后,对计数器清零,门控转为初始态;继续对时钟进行计数,产生周期性的门控信号。

第二级在每路信号后面设置延时器,FPGA采用50MHz频率,内部设置最小延时单元为20ns,计算信号延时需要的最小延时单元个数,当上位机设置门控信号超前时钟信号时,将时钟信号延时相应的节拍数;当上位机设置门控滞后时钟时,将门控信号延时相应的节拍数。因此,信号时延的精度可达到20ns。

3.3 幅值拉偏电路

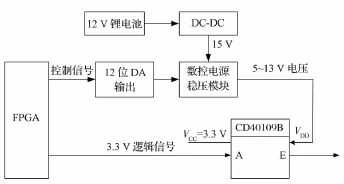

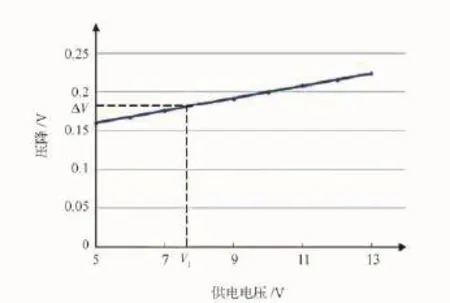

星上接口电路分为单端接口和差分接口。针对单端接口,使用数字控制电源[7]对CD40109B电源转换芯片的输出端供电电压进行调节,实现方式如图3所示,其中VCC代表芯片输入端供电电压,VDD代表输出端供电电压。数控电源提供5~13V电压的精确调节功能,12位数模转换(DA)控制器对数控电源进行控制,控制分辨率可以达到15V/4096=3.66mV。通过改变输出端的电源电压可以实现输出信号的幅值变化,但是由于限流电阻和芯片内部场效应管特性,输出信号相对供电电压存在压降,为此测试了不同供电电压下输出信号的压降值,绘制了压降补偿曲线,如图4所示。将压降和其对应的补偿值制成表格存入DSP存储区,DSP软件调用此表对接收到的上位机设置值进行补偿,例如,接收到的信号电压设置值为V1,查询表格得到补偿值ΔV,将补偿后的电压值V1+ΔV传输给FPGA,FPGA据此设置供电电压值。

通过对幅值拉偏设置进行补偿,提高了幅值拉偏的精度。由于电源纹波和地线杂波的干扰,经测试,设备的电压幅值输出精度为50mV。

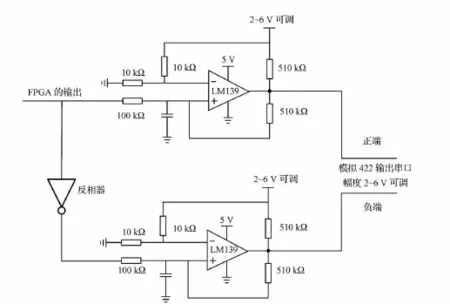

星上差分电路主要采用422差分驱动芯片,芯片正常工作供电电压范围为4.5~5.5V,仅改变芯片电压无法实现大范围的幅值拉偏,所以提出了一种专用的改变差分电平输出的方法,如图5所示。FPGA输出的逻辑电平一路经过比较器输出,另一路经过反相后再经过相同的比较器电路,实现2~6V的幅值输出范围。

图3 单端接口拉偏方式Fig.3 Deflection method of single circuit

图4 压降补偿曲线Fig.4 Compensation graph of voltage

图5 差分电路拉偏方式Fig.5 Deflection method of difference circuit

3.4 上升沿拉偏电路

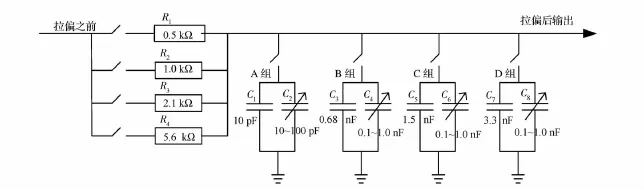

星上单机对上升沿时间拉偏需求为0.1~100.0μs,通过一种可变阻容网络来实现信号上升沿的改变。使用继电器开关控制接入电路中的电阻和电容值,调整电路的时间常数,可以改变输出信号的上升沿时间,如图6所示。本设计中上升沿时间定义为信号幅值从10%到90%之间的时间间隔,为2.2倍的时间常数。

图6中,设计了4组电阻和4组电容单元,每组电容单元均由一个电容和一个可变电容器并联组成,可变电容调节方式为手动调节。A组为精调电容单元,电容调节范围(C1+C2)为20~110pF,调节精度为0.1pF,配合4组电阻,可实现的上升沿调节范围为0.02~1.36μs;B、C、D组实现大范围的上升沿参数调整,使用的可调电容器(C4,C6,C8)范围为100~1000pF,调节精度为10pF,通过继电器的接合实现了800~8500pF的容值调整范围,配合4组电阻,上升沿调节范围为0.88~105.09μs。因此,满足了星上单机拉偏需要的上升沿范围。

由于B、C、D组的可变电容调节精度较差,在进行较大时间上升沿精调时,须接入A组电容单元。使用示波器观察输出信号的上升沿,手动调节C2旋钮改变电容值,待上升沿满足精度要求。上升沿时间最长(100μs),拉偏精度最差,理论计算误差小于10ns,但是由于电路板的寄生感抗、容抗和示波器的测量误差,可实现的拉偏精度优于100ns。

图6 接口边沿拉偏示意图Fig.6 Circuit of interface rise time deflection

3.5 星地接口安全设计

接口容差的硬件测试方法考验接口在极端情况下的传输性能,会带来一定的测试风险,因此测试系统的可靠性和安全性设计是重要内容,也是测试方法能否最终得到应用的有效保证[8-9]。安全设计须要考虑限流限压保护和接口隔离。在电源输出端采用固态限流器进行限流,在信号输出端并联稳压二极管进行限压,保证不会有过流过压信号进入星上设备。

供电和接地是接口隔离设计的主要考虑因素。本设计采用12V锂电池供电,避免了将市电220V高电压及其地线干扰引入星上设备的风险,并由隔离电源将12V电压转换为设备内部所需电压。计算机和功能模块之间通过磁耦隔离芯片通信[10],可以实现2500Vrms的有效绝缘电压。

通过以上设计可以对接口电路进行保护,保证测试系统与星上设备的隔离,使得测试系统发生故障时不会影响到星上设备。

4 容差测试方法验证

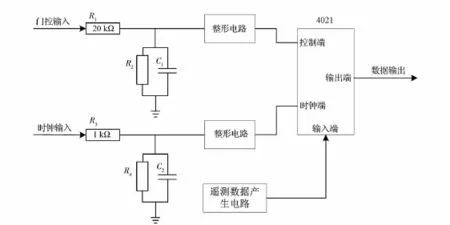

为了验证本文提出的接口容差测试方法,在某卫星型号单机设备上进行了应用。针对该单机的遥测数字量传输接口,分别通过蒙特卡罗仿真方法和硬件测试方法分析容差指标,接口时序关系如图1所示,接口电路示意如图7所示,该单机接收门控和时钟信号,输出遥测数据。

图7 遥测传输接口电路示意图Fig.7 Circuit of telemetry transmission interface

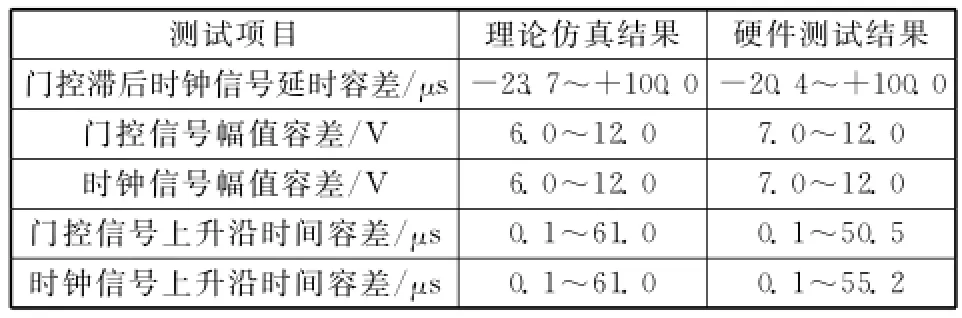

使用Multisim软件对电路进行仿真分析,使用接口容差测试设备对实际电路进行测试,分别得到了接口的容差指标,分析对比见表1。由表1可见,理论仿真结果和电路实测结果存在误差,对接口电路按本文方法进行硬件实测是有必要的。

接口容差测试设备对多个卫星型号的单机设备进行了验证试验,试验结果表明:时序延时、幅值和上升沿条件的恶化,均会影响信号传输,在真空高低温情况下,容差指标会发生相应偏移。通过接口容差测试系统验证,满足容差指标要求的单机设备,在整星总装测试中均未发生接口不匹配现象。

表1 理论分析与硬件测试结果对比Table 1 Contract of theory analyze and hardware test

5 结束语

本文分析了对卫星数字传输接口进行容差测试的必要性,传统的电路容差仿真方法存在较大误差,因此提出了对接口容差进行硬件测试的方法,并研制了相关测试设备。遥测接口容差测试设备基于嵌入式平台实现,采用最坏情况试验法,对遥测信号进行大范围和高精度的拉偏测试。通过理论分析与硬件测试方法对比,证明了硬件测试方法的有效性。本测试方法已实际应用于卫星单机间遥测接口设计,有效避免了接口不匹配现象,并对卫星其它数字接口容差测试具有推广应用的意义。

(

)

[1]Isabel Gonzalez,Ismael Sanchez.Statistical tolerance synthesis with correlated variables[J].Mechanism and Machine Theory,2009,44(6):1097-1107

[2]尹峰,王巍,梁涛.基于关键特性的数字化容差分配技术研究[J].航空制造技术,2011(22):53-56 Yin Feng,Wang Wei,Liang Tao.Research of digital tolerance distribution technology based on key characteristics[J].Aeronautical Manufacturing Technology,2011(22):53-56(in Chinese)

[3]李红,付兴武.基于容差分析的电路参数中心值设计研究[J].现代电子技术,2005,28(23):88-90 Li Hong,Fu Xingwu.Research of central value design of circuit parameter based on tolerance analysis[J].Modern Electronics Technique,2005,28(23):88-90(in Chinese)

[4]刘维罡,沈颂华,骆明珠.航空电源系统的容差分析及仿真研究[J].测控技术,2007,26(6):79-82 Liu Weigang,Shen Songhua,Luo Mingzhu.Circuit tolerance analysis and simulation study for aviation power system[J].Measurement &Control Technology,2007,26(6):79-82(in Chinese)

[5]李杨,孙玉国,金鑫.基于嵌入式逻辑分析仪的FPGA测试[J].仪器仪表学报,2006,27(6):2372-2373 Li Yang,Sun Yuguo,Jin Xin.FPGA signal extraction based on embedded logic analyzer[J].Chinese Journal of Scientific Instrument,2006,27(6):2372-2373(in Chinese)

[6]卢祥弘,陈儒军,何展翔.基于FPGA的恒温晶振频率校准系统的设计[J].电子技术应用,2010(7):101-104 Lu Xianghong,Chen Rujun,He Zhanxiang.The design of frequency calibration system for OCXO based on FPGA[J].Application of Electronic Technique,2010(7):101-104(in Chinese)

[7]胡辉,杨花雨.基于单片机控制的数控电源设计[J].商丘职业技术学院学报,2013,12(5):60-61 Hu Hui,Yang Huayu.Design of digital power source based on single chip microcomputer[J].Journal of Shangqiu Vocational and Technical College,2013,12(5):60-61(in Chinese)

[8]焦荣惠,李砥擎,陈粤.一种卫星低频接口自动测试系统[J].航天器工程,2014,23(4):115-119 Jiao Ronghui,Li Diqing,Chen Yue.An automatic test system of satellite low frequency interface[J].Spacecraft Engineering,2014,23(4):115-119(in Chinese)

[9]崔海涛,于曦.复杂电磁环境下RS422接口保护电路的实现[J].航空计算技术,2011,41(6):119-124 Cui Haitao,Yu Xi.Design and achievement for a kid of protection electrocircuit to RS422interface[J].Aeronautical Computing Technique,2011,41(6):119-124(in Chinese)

[10]郑采君,肖原.新型磁耦合隔离电路设计[J].电子设计工程,2011,19(4):162-166 Zheng Caijun,Xiao Yuan.Design of new magnetic coupling isolating circuit[J].Electronic Design Engineering,2011,19(4):162-166(in Chinese)

(编辑:李多)

A Tolerance Test Method for Digital Telemetry Interface and Its Implementation

AN Weiyu HAN Xiaodong WANG Zhifu

(Institute of Telecommunication Satellite,China Academy of Space Technology,Beijing 100094,China)

A test method of digital telemetry interface is introduced by analyzing the character of common interface circuit and researching the schedule,voltage and rise time of signal transmission.Test equipment is invented.It has the capability of producing schedule deflection,voltage deflection and rise time deflection.So,it can measure the interface tolerance quantitatively.A deflection test of satellite units verifies the validity of the test method and the practicality of the equipment.

satellite;digital interface;tolerance;test method

V416

A

10.3969/j.issn.1673-8748.2016.02.019

2015-09-10;

2015-12-29

国家重大航天工程

安卫钰,男,硕士,工程师,研究方向为航天器总体设计。Email:anweiyuan@126.com。