3D叠层封装集成电路的芯片分离技术

2016-05-18林晓玲梁朝辉温祺俊

林晓玲,梁朝辉,温祺俊

(1.工业和信息化部电子第五研究所,广东 广州 510610;2.电子元器件可靠性物理及其应用技术重点实验室,广东 广州 510610)

3D叠层封装集成电路的芯片分离技术

林晓玲1,2,梁朝辉2,温祺俊2

(1.工业和信息化部电子第五研究所,广东广州510610;2.电子元器件可靠性物理及其应用技术重点实验室,广东广州510610)

摘要:3D叠层封装是高性能器件的一种重要的封装形式,其鲜明的特点为器件的物理分析带来了新的挑战。介绍了一种以微米级区域研磨法为主、化学腐蚀法为辅的芯片分离技术,包括制样方法及技术流程,并给出了实际的应用案例。该技术实现了3D叠层芯片封装器件内部多层芯片的逐层暴露及非顶层芯片中缺陷的物理观察分析,有助于确定最终的失效原因,防止失效的重复出现,对于提高集成度高、容量大的器件的可靠性具有重要的意义。

关键词:3D叠层封装;集成电路;芯片分离技术;区域研磨法;化学腐蚀法

0 引言

采用立体空间实现多芯片互连的3D叠层芯片封装技术,可以在不改变封装体尺寸的前提下,在同一个封装体内于垂直方向利用引线键合或者穿透硅通孔TSV互连等方式叠放两个或以上的芯片。3D叠层芯片封装集成电路能够在提高电路性能的同时,极大地降低电路的功耗,因而成为了高性能器件的新宠[1-3]。

对于全新的3D叠层封装集成电路,有时需通过破坏性的物理分析,检查其内部结构,这就需要将电路内部的多层芯片逐层地暴露,并对各层的内部结构进行目检,以便验证其内部材料、设计和结构是否符合适用的设计文件或其他规定的要求[4]。3D叠层封装集成电路若在使用的过程中出现失效,则缺陷可能存在于多层芯片的某一层中(非顶层芯片)。此时,若想对该缺陷进行物理分析或进一步地对芯片级缺陷进行定位,则均需要在将电路开封并去除该缺陷所在芯片层次之上的芯片之后才可进行。但是,由于芯片的材质为硅(Si),无法采用化学腐蚀法去除,即使是用氢氟酸(HF)浸泡,也不能将其腐蚀去除。而机械开封法主要是用于对陶瓷盖板封装或者金属壳封装的器件进行开封,通过磨或撬相结合的方法将封装外壳材料去除,露出封装内腔,但该方法无法对封装腔体内的芯片进行局部处理并确保引线不受到损坏。因此,传统的化学腐蚀或机械开封法均无法满足3D叠层封装集成电路非顶层芯片物理分析的需求[5-6]。如何将目标芯片之上的芯片去除,便成为了3D叠层封装集成电路失效分析/物理分析过程中遇到的棘手问题。

本文结合3D叠层封装的结构特点,介绍了一种以微米级区域研磨技术为主、化学腐蚀法为辅的芯片分离技术,包括其制样方法和技术流程。该技术实现了3D叠层芯片封装器件内部多层芯片的逐层暴露及非顶层芯片中缺陷的物理观察分析,对于提高集成度高、容量大的器件的可靠性具有重大的意义。

1 芯片分离技术的制样方法及流程

利用芯片分离技术将叠层芯片分离的示意图如图1所示。

要想暴露非顶层芯片,除了需要去除封装材料之外,还需要去除上层芯片及芯片之间的粘结剂。因此,芯片分离技术,需要多步骤的配合,才能确保3D器件内部下层芯片的成功暴露。本文采用的芯片分离技术包括区域研磨法和化学腐蚀法两部分,涉及区域研磨前的准备工作(包括样品固定、检查样品平面是否平整(关乎研磨的平整度等问题)、芯片内部结构初步分析和研磨工具选择等)和研磨过程(包括负载施加、研磨终点监测和研磨与化学腐蚀法的搭配等)两部分内容。

图1 利用芯片分离技术将叠层芯片分离的示意图

3D叠层封装器件的芯片分离方法的技术流程如图2所示,具体包括以下几个步骤。

a)确定研磨区域及其面积

利用声学扫描显微检测法观察3D叠层芯片封装集成电路的内部结构,包括器件内部芯片的层数和芯片面积的大小,并确定研磨区域及其面积。

b)固定

用热熔蜡将3D叠层芯片封装集成电路固定在研磨台上。该方法避免了采用夹具夹紧固定时夹具对封装内部芯片造成的受迫破裂或者翘曲损伤,使研磨时样品的厚度、尺寸不受约束。

c)研磨

根据步骤a)所确定的研磨区域及其面积,选择研磨钻头、研磨力度、研磨深度和研磨速度,去除研磨区域的封装材料和芯片,研磨至目标芯片表面覆盖的保护层。若研磨面积为3~6 mm2,则研磨钻头的长度应为1mm;若研磨面积为7~15 mm2,则研磨钻头的长度应为3 mm;若研磨面积大于15 mm2,则研磨钻头的长度应为5 mm。

此处所指的研磨应为步进式研磨,即步进施加研磨力度。对于同一种材质,初始时力度较大,例如:第一次研磨总研磨厚度的1/4~1/2,随着研磨的进行,力度逐渐地减少。研磨力度是指通过刻度旋钮设置向下研磨的厚度而施加相应的力,研磨力度决定了每次研磨去除的厚度。而研磨方向可设置为:XY方向、X方向或Y方向。

d)化学腐蚀

采用化学腐蚀法,去除步骤c)所述的目标芯片表面覆盖的保护层。

图2 芯片分离方法的技术流程图

2 芯片分离过程的注意事项

在芯片分离的过程中,应注意以下几个事项。

a)固定初期,应采用表面多点测量的方法

使用热熔蜡将3D叠层芯片封装集成电器固定在研磨台上的过程中,由于热熔蜡的受热流动性,在冷却时可能造成器件表面不平整,从而导致后续研磨时器件表面出现高低不平的现象。因此,在固定初期,需采用表面多点测量的方法,以确保样品在研磨台面上的平整度。

b)对研磨过程进行严格的监控

研磨不足将无法暴露芯片的内部结构,研磨过度又会损坏芯片并丢失证据。由于失效样品的重要性和稀缺性,所以必须降低研磨风险。为了避免研磨不足和研磨过度,必须对研磨过程进行严格的监控。在研磨的过程当中,需不时地通过显微观察监测研磨终点。试验过程中发现,通过观察各种材料被研磨时的颜色变化情况可以有效地判断研磨终点,及时地了解样品内部结构的变化情况。因此,3D叠层封装的内部芯片逐层暴露的规律大概如下:未被研磨的塑封料呈黑色;被研磨过的塑封料呈浅灰色,且形貌细致,如图3所示。硅片(例如:芯片与芯片之间起支撑作用的垫片)在未被研磨之前,光滑细致,呈光亮的镜面状,如图4所示;被研磨之后,颜色呈浅灰色,而且,由于其硬度大,被研磨后,明显地会变粗糙很多,如图5所示。当上层硅片被研磨到很薄一层时,透过该薄层可看到下层芯片的内部结构,如图6所示;继续研磨,可看到第二层芯片上的保护层,呈橙黄色透明状,透过该保护层,可更清楚地看到下层芯片的内部结构,如图7所示。

显微观察研磨终点监测法不仅摆脱了对样品数量的依赖,还进一步地确保了研磨区域的大小和深度可控,避免了过度研磨或研磨不足的情况。

图3 经研磨后的塑封料的形貌图

图4 未被研磨的硅片的形貌图

图5 经研磨后的硅片的形貌图

图6 上层硅片被研磨至一薄层时,透过该薄层可看到的下层芯片的内部结构的形貌

图7 透过芯片表面覆盖的保护膜看到的下层芯片的内部结构形貌

3 芯片分离技术在3 D叠层封装集成电路中的应用实例

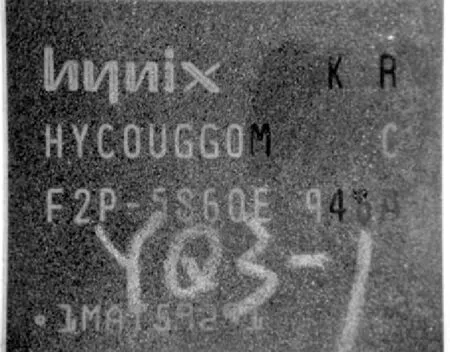

以内含NAND Flash和Mobile SDRAM两个芯片(两层芯片采用十字交叉型叠层形式)的Htnix叠层封装存储器为例,其外观如图8所示,通过分离暴露第二层芯片(下层芯片)来说明区域研磨法和化学腐蚀法相结合的芯片分离技术在3D叠层封装集成电路中的实际应用,具体过程如下所述。

a)确定研磨区域及其面积

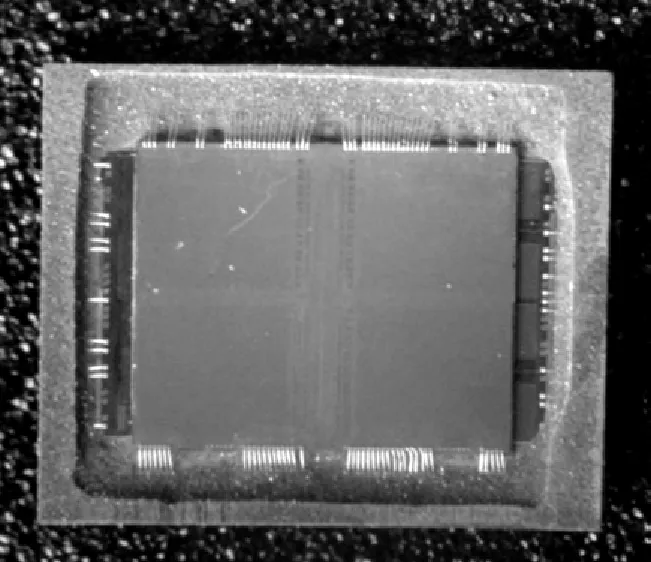

利用声学扫描显微镜检测存储器的内部结构,如图9所示,存储器为十字交叉型双边引线封装;确定研磨区域为封装材料和第一层芯片,面积约为8 mm;同时测量存储器初始厚度约为1 mm,根据经验,通常最上层的封装材料的厚度约占存储器总厚度的1/3,从而为确定后续研磨步骤中研磨封装材料的研磨力度提供了参考。

b)固定

将存储器用热融蜡固定在研磨台上。

c)研磨

根据步骤a)确定的研磨区域及其面积,选择长度为3 mm的研磨钻头,利用金相显微镜监测研磨进度,同时采用步进式研磨,初始研磨力度设置为向下研磨100 μm,从X、Y两个研磨方向进行研磨直至研磨到第二层芯片表面覆盖的保护层时停止研磨。

d)化学腐蚀

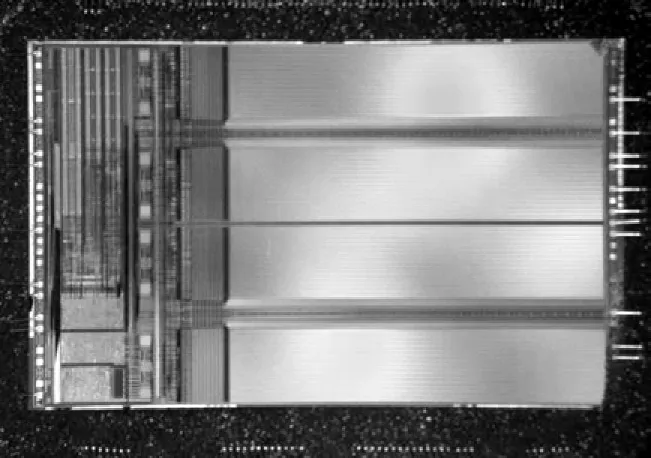

采用化学腐蚀法去除步骤c)中提到的第二层芯片表面覆盖的保护层,即可露出清晰完整的第二层芯片的表面。利用金相显微镜仔细检测器件,观察第二层芯片的内部结构、芯片上的键合引线,得到的结图如图10-14所示。从图10-14可以看出:采用本文所述的分离方法得到的目标芯片(下层芯片)的内部结构及其键合引线未受损,从而成功地实现了对下层芯片内部结构及键合引线的观察分析。

图8 器件的正面形貌

图9 存储器的内部结构

图10 第一层(顶层)芯片的形貌图

图11 去除第二层芯片(下层芯片)表面的保护层之后的芯片的形貌

图12 下层芯片的局部形貌图

图13 下层芯片上的键合引线

4 结束语

本文介绍了一种3D叠层芯片封装器件的芯片分离方法,该方法以区域研磨技术为主、化学腐蚀法为辅,实现了3D叠层芯片封装器件内部多层芯片的逐层暴露,解决了3D叠层芯片封装器件非顶层芯片物理分析难的问题,还可使一些3D叠层芯片封装的失效器件的失效分析得以顺利完成,对于确定3D叠层封装集成电路最终的失效原因及机理,防止失效的重复出现,提高器件的可靠性具有重要的意义。

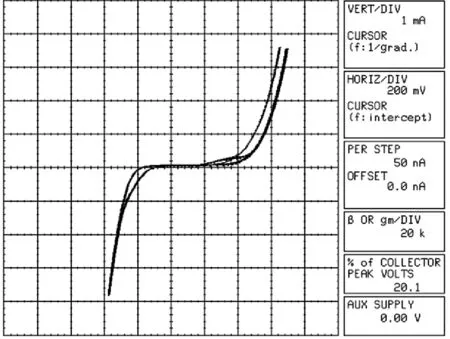

图14 下层芯片的某个管脚的IV曲线

参考文献:

[1]邓丹,吴丰顺,周龙早,等. 3D封装及其最新研究进展[J] .微纲电子技术,2010,47(7):443-450.

[2]夏艳. 3 D集成的发展现状与趋势[J] .中国集成电路,2011(7):23-28.

[3]顾靖,王珺,陆震,等.芯片叠层封装的失效分析和热应力模拟[J] .半导体学报,2005,26(6):1273-1277.

[4]国防科学技术工业委员会.微电子器件试验方法和程序:GJB 548A-96 [S] .

[5]孔学东,恩云飞.电子元器件失效分析与典型案例[M] .北京:国防工业出版社,2006:260.

[6]恩云飞,来萍,李少平.电子元器件失效分析技术[M] .北京:电子工业出版社,2015:453.

The Chip Seperation Technology of 3D Stacked Package IC

LIN Xiao-ling1,2,LIANG Chao-hui2,WEN Qi-jun2

(1. CEPREI,Guangzhou 510610,China;2. Science and Technologt Laboratort on Reliabilitt Phtsics and Application of Electronic Component,Guangzhou 510610,China)

Abstract:3D stacked package is one of the important packages for high-performance devices,whose specificitt brings new challenge to the phtsical analtsis of devices. A chip separation technology based on the micro-level regional grinding method and chemical etching method is introduced,including its sample preparation method and technique process,and a practical application example is given. The chip separation technologt realizes the exposure of the internal multilater chip later bt later and the phtsical analtsis of the defects in the non-top chip of the 3D stacked chip packaging device,which is helpful to determine the ultimate failure cause and to prevent the duplication of the failure. Besides,it has important significance for improving the reliabilitt of high integration and large capacitt devices.

Key words:3D stacked package;IC;chip separation technologt;regional grinding method;chemical etching method

作者简介:林晓玲(1978-),女,广东揭阳人,工业和信息化部电子第五研究所电子元器件可靠性物理及其应用技术重点实验室高级工程师,博士,主要从事微电子可靠性物理、IC失效分析技术等研究工作。

收稿日期:2015-10-15

doi:10.3969/j.issn.1672-5468.2016.02.008

中图分类号:TN 405

文献标志码:A

文章编号:1672-5468(2016)02-0036-05