高速信号抽取抗混叠滤波器的设计

2016-05-14李汉阳

李汉阳

摘要:在通信系统中,常见数字接收机解调器中经常会遇到高速信号抽取的问题,这就会用到多速率数字信号处理技术。在抽取前,需要设计合适的抗混叠滤波器对信号进行滤波处理。在抽取倍数较大的情况下,滤波器阶数较多,其延迟时间和硬件消耗较大。本文提出了一种级联滤波结构,按照文中的参数,在同样的滤波效果下,方案复杂度降低了90.7%。

关键词:高速率信号 抗混叠 滤波器

中图分类号:TP274 文献标识码:A 文章编号:1007-9416(2016)05-0000-00

通信系统中,常见数字接收机解调器中经常会遇到高速信号抽取的问题,这就会用到多速率数字信号处理技术。在抽取前,需要设计合适的抗混叠滤波器对信号进行滤波处理。在抽取倍数较大的情况下,滤波器阶数较多,其延迟时间和硬件消耗较大。本文提出了一种级联滤波结构,在同样的滤波效果下,降低了信号处理的方案复杂度。

1参数设置

为了更好地描述上述问题,本文以以下的参数为例进行分析。令接收端接收到载波频率为30MHz的模拟信号,ADC芯片以24MHz的采样频率对模拟信号进行带通采样,采样数据进入解调器,进行的6MHz的数字正交下变频,信号带宽为50KHz,正交下变频后信号采样率为24MHz。24MHz的信号需要经过100倍降采样后采样率为240KHz的信号,处理后再次经过40倍采样用于其他处理。

2 100倍抽取方案设计

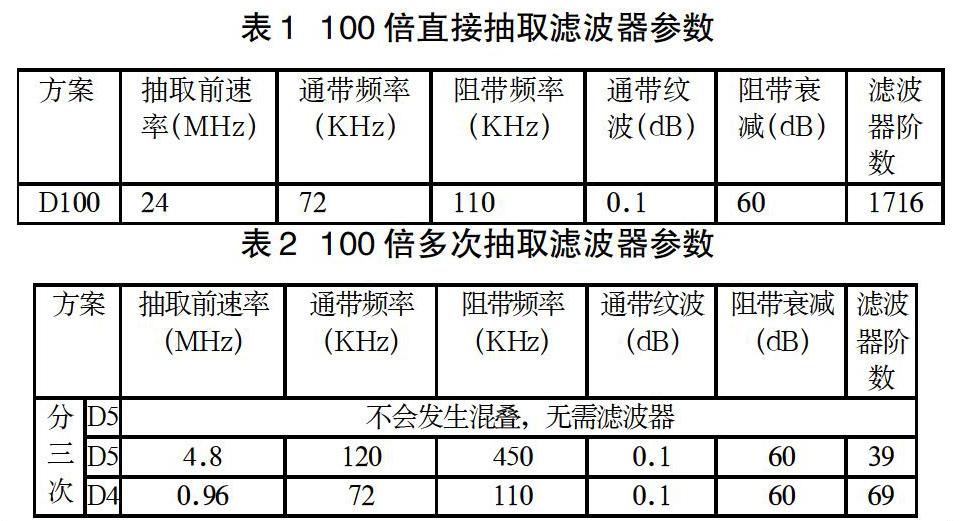

解调器涉及到多速率数字信号处理技术,100倍降采样及40倍降采样都需要考虑信号的混叠问题,需要设计合适的抗混叠滤波器在抽取前对信号进行滤波处理。首先讨论100倍降采样滤波器设计。抽取前采样率为24MHz,抽取比例100,抽取后采样率为240KHz。由s上节的参数可知,倍抽取前抗混叠滤波器阻带频率不能大于120KHz,从而保证抽取后信号不会发生混叠。利用Matlab滤波器设计和分析工具fdatool对滤波器进行设计,参数设置见表1。

由表1可知,在24MHz的采样率下,一次性实现100倍降采样需要抗混叠滤波器阶数为1716,意味着输入数据要与滤波器系数做1716次乘法及加法,硬件资源消耗大,滤波器延迟时间长。

为了解决上述的多次乘法的问题,可将抽取过程分解为5*5*4倍抽取的级联实现100倍降采样过程:第一次倍抽取无需抗混叠滤波器(信号截止频率为2.4MHz,噪声最大带宽为0.5MHz,小于截止频率);第二次倍抽取仅需要39阶滤波器;第三次倍抽取仅需要69阶滤波器;对比以上两种方案,第二种级联方案实现简单,资源消耗小。其参数设置见表2。通过计算可知,采用级联结构后,所需的乘法次数为39+69=108次,其方案复杂度降低了93.7%。

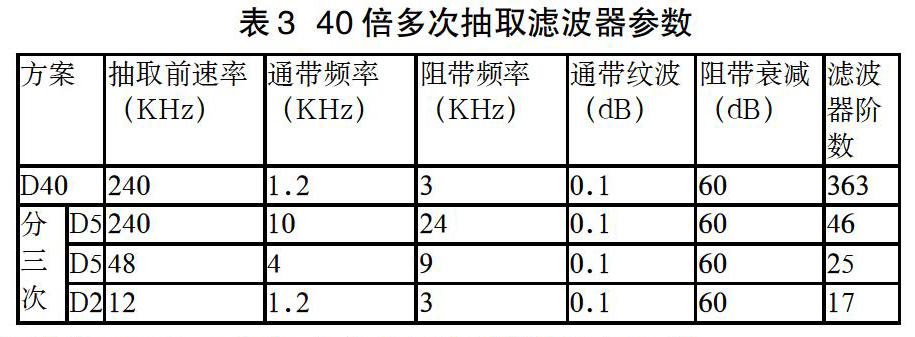

3 40倍抽取过程

从以上可以看出,采用级联结构的滤波器比直接抽取滤波器阶数小,设计简单,节省硬件资源。100倍抽取采用5*5*4倍抽取级联的形式完成,40倍抽取则采用5*5*2倍抽取级联的形式完成,其参数设置见表3所示。可知,40倍的抽取采用多级级联结构后,方案复杂度降低了(363-46-25-17)/363=75.7%。总体方案复杂度降低了90.5%。

4 其他降低复杂度的方案

此外,可以将5倍、4倍、2倍抽取利用多相滤波实现,不仅降低对实时处理的要求因此,而且模块可以实现复用,提高效率。工程应用中,当系统设计对资源要求比较高时,可以选择使用半带滤波器和CIC滤波器实现滤波及抽取过程。对于40倍抽取来说,可以采用CIC滤波器实现5倍抽取,三级半带滤波器级联实现8倍抽取,每级滤波器系数10阶左右,资源消耗低,计算速度快;若系统对实时处理要求很高,则建议采用多相滤波结构,增加系统的实时处理能力及吞吐量。

5结语

本文提出了一种级联滤波结构,在同样的滤波效果下,将100倍抽取采用5*5*4倍抽取级联的形式完成,40倍抽取采用5*5*2倍抽取级联的形式完成,对两种抽取分别降低了93.7%和75.7%,总体方案复杂度降低了90.7%,很好地减少了资源的消耗并降低了信号处理的延迟时间。

参考文献

[1]严慧,于继明.基于Matlab的IIR数字滤波器设计[J].软件导刊,2013,01:110-113.

[2]吕幼新,郑立岗,王丽华.基于多相滤波的宽带数字化接收机技术[J].电子科技大学学报,2003,02:133-136.

[3]尚文明. Sigma-Delta ADC数字抽取滤波器的设计与优化[D].电子科技大学,2013.

[4]姜岩峰,张东,于明.数字接收机中CIC滤波器的设计[J].电子测量与仪器学报,2011,08:671-675.

[5]韩计海,吴炳洋.基于MATLAB的高性能半带滤波器设计[J].信息化研究,2009,06:24-28.