基于FPGA正交扫频信号源的设计

2016-05-14吴强罗淑萍

吴强 罗淑萍

摘 要 正交扫频信号源是现代电子系统的重要组成部分,其广泛用于许多领域。本文以PFGA为平台,采用直接数字频率合成技术(DDS技术),基于Verilog HDL描述语言设计一正交扫频信号源,其频率可设置。利用Quartus II软件编写程序、编译检查以及综合测试,最终在示波器中观察到频率可调的正交信号源。实验表明其正交扫频信号源其系统运行可靠,集成度高,抗干扰性强等特点。

【关键词】正交扫频信号;FPGA;DDS

1 引言

传统方法设计的正交扫频信号源有着频率不稳定,精度不高,不易扩展等诸多弊端,随着EDA技术的发展,设计的产品朝着微型化,速度快方向发展。本文设计一种基于FPGA正交扫频信号源的电路,是一种用EDA技术实现扫频功能的装置,具有外围电路少、集成度高、可靠性强等特点。论文主要利用DDS技术,通过相位累加器累加相位、ROM存储波形数据、D/A转换器将数字量转换成模拟量,最终实现正交信号的设计。通过采集和处理数据来控制和产生需要的波形及其参数指标,实现可调波形、波形频率和幅度、扫频范围和频率步进值的信号源。

2 系统的总体设计

本论文采用DDS技术,采用FPGA平台,设计一正交扫频信号源。其正交扫频信号源主要指标如下:

(1)频率范围为1MHz~40MHz,频率稳定度≤10-4;频率可设置,最小设置单位100kHz。

(2)可以通过扫频方式输出,扫频范围可以根据需要自由设置,频率步进值可以自由调试,该步进值最小单位颗粒度为100KHz。

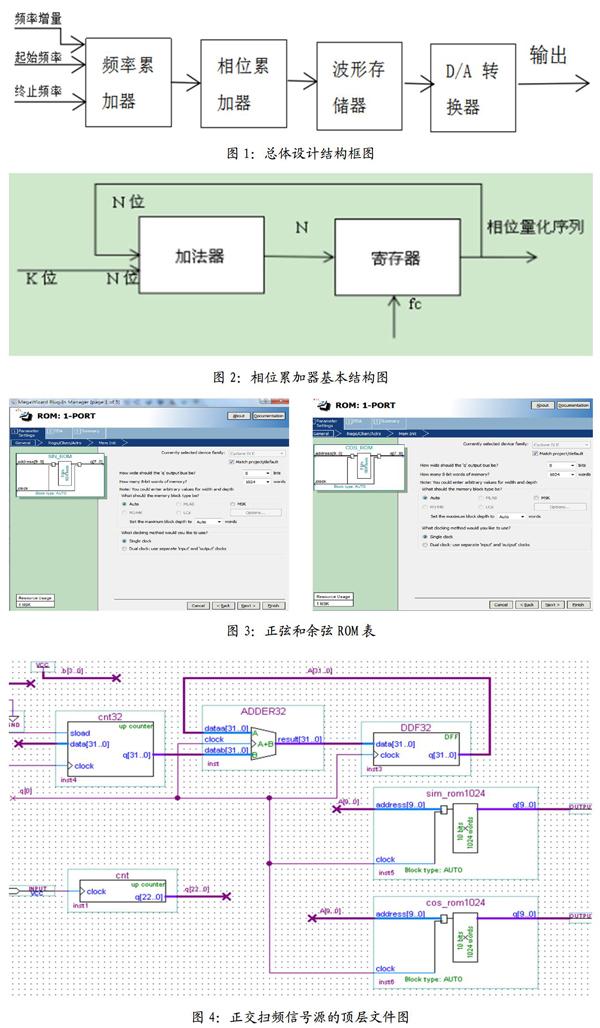

正交扫频信号源其主要由频率累加器、相位累加器、波形存储器和DAC数模转换器构成,该总体设计方案图如图1所示。电路的设计思路为:基准频率采用系统内部时钟进行分频,以供后续电路提供时钟,先用两个ROM存储波形数据,然后设计两个相位累加器,一个是正弦波,另一个是余弦波的。其次通过调整相位累加器和调节扫描信号的频率值和相位值。最终经过D/A转换器方式将输出的数据结果转换成模拟量,进行实时观察两个正交信号。

3 正交扫频信号源的实现

3.1 频率累加器的实现

频率累加器实现扫频信号源的频率控制字,其频率累加器的输出即为相位累加器的数据位宽。根据扫频信号源输出频率的范围及扫频信号源频率步进值,可计算出频率累加器输出的频率位宽。将得到的频率值转换成32位的二进制值,再得到的数据存入数据存储器ROM中。

3.2 相位累加器的实现

相位累加器是整个DDS的核心,由加法器和寄存器构成,其作用完成相位累加功能。相位累加器的功能实际上是相当于一个以频率累加器输出频率为步进值进行计数,如图2所示。其工作原量是频率累加器输出K位(32位)作为加法器的一个输入端,寄存器的输出作为加法器的另一个输入端,加法器的输出给寄存器的输入端。在下一个时钟信号来临时,寄存器在时钟信号的作用下,把寄存器的输出反馈到加法器的另一个输入端中,以便和频率累加器的输出K相加。这样相位累加器实现了对频率累加器输出的频率进行线累加。

3.3 存储波形设计和D/A模块设计

利用Q uartus II软件自带的LPM宏功能模块来设计正弦波和余弦波的数据ROM功能。系统定制好的ROM寻址就是相位累加器的输出数据值。设计好的正弦和余弦波的ROM如下图所示。波形存储器输出的数据通过D/A转换器转换成为模拟信号输出。

3.4 正交扫频信号源的顶层文件设计

本设计是基于FPGA的硬件正交扫频信号源电路,用ALTERA公司的 Cyclone IV系列 EP4CE6E22C8作为开发板,在Quartus II 开发环境下设计。硬件正交扫频信号源电路顶层文件设计是以图形化形式体现,设计了ROM存储波形、相位累加器和D/A转换器其顶层文件如图4所示。

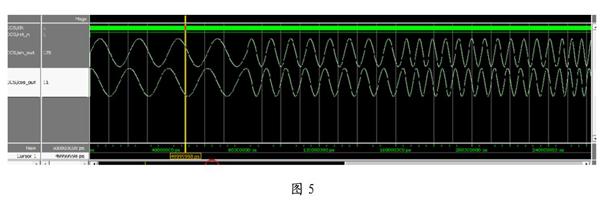

对顶层文件进行仿真运行后,可得到正交扫频信号源的输出波形,其输出波形如图5所示。

4 结束语

本系统设计是基于FPGA的正交扫频信号源的设计,采用EDA技术设计,简单实用,成本较低,基本达到了设计要求。

参与文献

[1]李平.基于FPGA的扫频信号发生器的设计与实现[D].云南大学,2014(06).

[2]李菊.改进型DDS的FPGA设计及验[J].无线电技术,2006.

[3]潘松,陈龙,黄继业.EDA技术与Verilog HDL(第2版)[M].北京:清华大学出版社,2013(04).

作者简介

吴强(1983-),男,汉族,江西省宁都县人。硕士研究生学历。现为赣南师范学院科技学院讲师。

罗淑萍,女,汉族,现为赣南师范学院科技学院电子信息工程专业本科生。

作者单位

赣南师范大学科技学院 江西省赣州市 341000