IEEE 1588 精确时钟同步系统仿真平台研究与实现

2016-05-06赵勇高彦杰

赵勇 高彦杰

【摘要】对IEEE 1588精确时钟同步协议进行了深入地研究,建立了一个相对完整的时钟同步仿真平台,并与IEEE1588硬件系统的同步结果比较,表明该仿真平台能够比较准确地反映实际硬件同步系统所取得的时间同步精度,为进一步研究同步精度及收敛时间提供了一个简单有效的仿真工具。

【关键词】 晶振漂移 IEEE 1588 精确时钟同步

引言

如今工业控制系统应用越来越多,系统规模越来越大,对于各个子系统间的时间同步精度要求也越来越高。因此高精度的时间同步实现方案成为一大需求。IEEE 1588协议因其能达到微秒级的同步精度而得到越来越广泛的应用。从IEEE 1588协议提出至今,关于其的研究已有很多,但大都以硬件平台为主,软件平台较少,且一般都是针对协议某一方面的研究,例如Zdenek Chaloupka[1]提出了一种基于时钟的IEEE 1588协议仿真模型,它仅局限于协议中报文时间戳产生部分。

本文对文献[1]的工作进行了扩展和完善,建立了一个完整的IEEE 1588时间同步仿真平台,它完整地反映了协议的同步工作过程,并且将仿真得到的同步精度与硬件平台的结果做了对比,验证了仿真平台的有效性。

一、同步系统分析与建模

基于IEEE 1588协议的时钟同步系统模型如图1所示,整个同步系统分为三个主要模块:主从时钟晶振模块、IEEE 1588协议模块、从时钟伺服控制模块。首先由主从时钟晶振模块产生相应的主从时钟频率;其次IEEE 1588协议模块根据主从时钟频率和协议得到主从时钟消息交换的四个时间戳;最后从时钟伺服控制模块通过利用时间戳计算出主从时钟偏移,调整从时钟时间完成与主时钟的同步。

1.1主从时钟晶振模块

本文采用了公认的幂率谱晶振模型[2]。对于一个晶振频率源,设标称频率为f0,瞬时频率为f,定义瞬时相对频率偏差(晶振噪声)为 y (t):y(t)=(f-f0)/f0,在幂率谱晶振模型中,y(t)的功率谱密度可表示为,

1.2 IEEE 1588协议模块

IEEE 1588协议框图如图3所示。需要注意,该模块有三个时间参考:主时钟晶振频率,从时钟晶振频率和理想时钟频率,主时钟以Tpck为周期发送同步报文,Tpck是以主时钟频率(fM)为参考的量,相对应的以时钟频率(fS)为参考时间量为Δs[n],和以理想频率(fR)量为Δs[n]。它们的关系如下:

Ψ[n]表示理想时间量。vM,S[n] 表示经换算得到的相应主从时间量。IEEE 1588协议主从时钟模型如图4所示。

1.3从时钟伺服控制模块

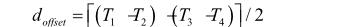

从时钟伺服控制系统对协议模块中的四个时间戳进行计

算得到主从时钟延迟:dm2s=T1-T2;从主时钟延迟:ds2m=T3-T4;假设传播延迟对称,得到从时钟偏移量:

将从时钟偏移量doffset通过PI控制器后对从时钟进行调整,使其达到与主时钟同步。

二、仿真平台验证

为了检验仿真平台的有效性,将仿真结果与现有公开文献[3]相比较。其是基于硬件的IEEE 1588时间与频率同步系统,其主要参数设置如下:主从时钟晶振为50 MHZ,±50 ppm的晶振;同步周期:125 ms。图5为收敛后(时间>1000 s)从时钟误差曲线doffset及其分布图。从图中得出从时钟最终同步误差值约为±20 ns,参考文献[3]中的同步精度约为±33 ns。

通过上面的验证对比,本软件仿真平台能够比较精确地反映实际硬件同步精度。

三、总结与展望

本文提出了一个相对完整的IEEE 1588时钟同步仿真平台,并将其与硬件的同步系统进行对比验证,结果表明本仿真平台能够比较精确地反映实际硬件系统所能够达到的同步精度,为进一步研究同步精度及收敛时间提供了一个简单有效的仿真工具。

参 考 文 献

[1] Zdenek Chaloupka, Nayef Alsindi, James Aweya. Efficient and Precise Simulation Model of Synchronization Clocks in Packet Networks[J]. CAMAD,2013:79-83.

[2]尚红娟. 时间频率同步的优化控制方法研究[D]. 西安:西安科技大学,2010.

[3] Sven Meier, Hans Weibel, Karl Weber. IEEE 1588 Syntonization and Synchronization Functions Completely Realized in Hardware[J]. ISPCS,2008.