基于FPGA的皮秒计数设计*

2016-05-04唐海峰赵建军吴光敏吴亚平

唐海峰,赵建军,吴光敏,吴亚平,赵 恩

(昆明理工大学 理学院,云南 昆明 650500)

基于FPGA的皮秒计数设计*

唐海峰,赵建军,吴光敏,吴亚平,赵恩

(昆明理工大学 理学院,云南 昆明 650500)

摘要:在实际的现场可编程门阵列(FPGA)设计中,对纳秒以下的时间计数至今没有很好的方法进行处理。在以往的FPGA实现中,往往采用官方提供的DCM或PLL对时钟信号进行倍频处理。上述方法由于受到硬件资源的约束,用户不能随心所欲地对时钟信号进行多次处理,原因在于器件内部的DCM有限。提出了以IODELA原语为基础的方法进行时间计数设计,采用Verilog HDL硬件描述语言对皮秒进行计数操作,以Xilinx官方的Zedboard开发板和Virtex5开发板、以IODELAY原语与IDELAY原语为基础对纳秒以下的时间进行操作。经过功能仿真与板级验证,成功地实现了对于75 ps~4 ns(主频250 MHz的频率)的高精度计数功能。皮秒计数的实现,对于时间测量电路中细时间(主频频率<4 ns的时间,即75 ps~4 ns的时间)的生成,以及对于进行FPGA纳秒级别以下的时钟操作产生了巨大且深远的作用。目前,该单元已经成功地应用在了时间测量电路的设计上。

关键词:现场可编程门阵列;原语;皮秒计数;功能仿真;倍频

现场可编程门阵列(Field-Programmable Gate Array, FPGA)中使用的晶振为MHz频率,时钟周期即为ns级别。在FPGA中要完成对一个信号的倍频只能利用IP核对其进行倍频操作,而没有办法像分频处理一样利用Verilog/VHDL代码对它直接进行操作[1];但是在FPGA中资源是有限的,PLL/DCM的IP核也是有限的,并不能一直对其进行随意次的倍频操作。本设计利用Xilinx公司提供的原语直接对FPGA进行ps级别的操作,完成了直接利用代码进行源时钟的倍频操作,根据需求的不同可以最大倍频到75 ps。倍频范围为75 ps至主频时钟。

1基于Zedboard开发板的皮秒计数设计

Zedboard开发板是近年Xilinx公司推出的产品。该开发板采用Xilinx 7系列芯片XC7Z020封装为CLG484,等级速度为-1。Zedboard具有2个ARM9的硬核,用户可以单独对FPGA进行设计,也可以与ARM进行协同设计[2]。在视频处理、电动机控制和以太网通信等方面得到了广泛的应用。Zedboard开发板的实物图如图1所示,本设计因为只进行FPGA操作而不需要用到ARM,所以应将JP7、JP8、JP9、JP10和JP11接到低电平,JP3和JP6不接短路帽[3]。

图1 Zedboard开发板实物图

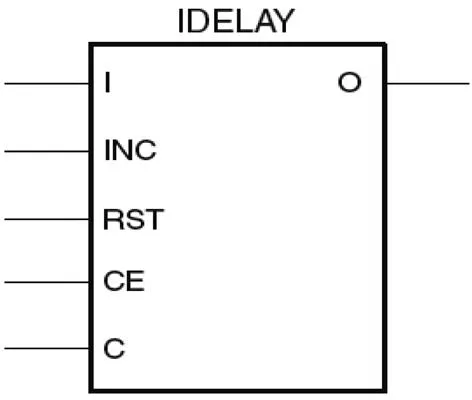

在Xilinx官方提供的用户手册上可以找到关于IDELAY原语的介绍。在Artix 7系列芯片中,每个用户I/O管脚的输入通路都有一个IDELAY模块。IDELAY具有可控制31个抽头延迟线,每个抽头的延迟为75 ps,且与进程、电压和温度特性无关。IDELAY原语的RTL模块图如图2所示。

图2 IDELAY原语RTL模型

在图2中,端口I为来自于IOB的串行输入数据的单比特输入信号,其中,端口I应由外部信号输入,不能由FPGA自身产生的信号作为I口的输入。简单而言,就是在顶层模块端口I应为input。输入C端口为时钟输入信号。INC端口用于增加或减少延迟抽头数。CE端口为是否能使延迟抽头数量增加或减少的功能。RST端口为复位延迟链的延迟抽头数。O端口为单比特输出信号。IDELAY具有3种操作:1)零保持时间延迟模式(IDELAY_TYPE = DEFAULT),在没有DCM的情况下使用全局时钟采集数据,用这种延时单元提供“非正保持时间”;2)固定延迟模式(IDELAY_TYPE = FIXED),通过属性值IDELAY_VALUE确定tap数从而确定延迟时间;3)可变延迟模式(IDELAY_TYPE = VARIABLE),通过控制信号CE和INC来改变延迟时间。本文采用固定延迟模式IDELAY = FIXED来进行75 ps的计数。由于采用的时钟频率为2 ns,所以本文要到达由75 ps~2 ns的计数,设定IDELAY_VALUE的值为i,其中i值为0~26,当i为26时,计数到1 950 ps。对IDELAY进行完例化后,根据用户手册的要求还应对原语IDELAYCTRL进行例化。IDELAYVTRL原语的RTL模型如图3所示。

图3 IDELAYCTRL原语的RTL模型

在图3中,RST端口为复位端口,当RST为高时,开始工作,REFCLK提供了一个参考时钟,校准IDELAY模块在同一时钟区域。RDY端口表示在特定区域的IODELAY模块准备就绪。在例化中RST置为高,其他2管脚悬空。完成上述所有设计后,应用Modelsim软件对其仿真产生波形(见图4)。

由图4可以观察到第1位比第0位滞后75 ps,第2位比第1位滞后75 ps,依次类推直到第26位。

2基于Virtex5开发板的皮秒计数设计

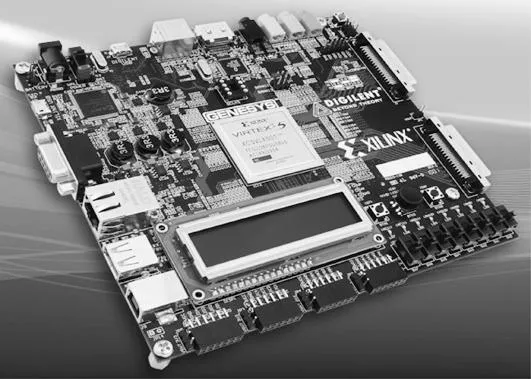

Virtex5开发板属于Xilinx公司Virtex系列芯片,XC5VLX50T封装为ff1136,等级速度为-1。此款开发板并没携带硬核只能单独进行FPGA的设计,但这个开发板的IOB资源比Zedboard开发板资源多。采用时钟频率为250 MHz,所以要到达75 ps~4 ns的设计要求。Virtex5开发板的实物图如图5所示。

图5 Virtex5开发板实物图

根据Xilinx官方提供的Virtex5系列的用户手册,可以观察到IODELAY的原语介绍,V5开发板并没有IDELAY的原语。其中,IODELAY原语相对于IDELAY原语而言,多了一种配置方式,可以将IODELAY配置成ODELAY的方式进行延迟,其余的和IDELAY的无太大差别。在ODELAY的方式下,输入管脚不再必须由外端输入,可以由FPGA内部的信号产生。在工程量很大的情况下,大大减少了外接输入管脚的麻烦。IODELAY原语的RTL模型如图6所示。

图6 IODELAY原语的RTL模型

在图6中,IDATAIN为来自IOB的IODELAY数据输入信号,ODATAIN为来自OSERDES/OLOGIC的IODELAY模式的输入信号,DATAIN为FPGA内部资源的IODELAY数据输入。DATAOUT为经过IODELAY延迟后的输出数据。T端口可以控制IODELAY是作为IDELAY模式还是作为ODELAY模式。CE为启动递增或递减功能。INC为Tap延迟的递增/递减数。RST将IODELAY单元复位到预设定值。C为可变模式下使用的时钟输入。IODELAY仍选择固定延迟模式,由ODATAIN进行信号的输入。在ODELAY模式下可以不必例化IDELAYVTRL原语。利用Modelsim进行仿真后与图4完全一样。其中,应注意在ODELAY模式下输出DATAOUT端口在顶层模块中应作为输出端口[4]。

3对原语延迟后进行优化处理

由图4可以清楚地看出,后一位数据相对于前一位数据延迟了75 ps。利用后一位与前一位相异或处理,可以得到波形(见图7)[5-6]。

图7 进过优化后的皮秒计数

在图7中可以清楚地看到,时钟信号被分为了M等份,相当于把时钟信号倍频了M等份,清楚表现了纳秒以下的时钟操作。

4总结

本文基于Zedboard和V5开发板进行了纳秒以下时间的计数,提出了一种基于原语的方式进行皮秒计数的一种方式,为TDC等许多方面的设计提供了一种参考。本文完成了纳秒级别以下的计数,为很多FPGA无法处理皮秒时钟提供了参考。

参考文献

[1] 张泽,刘慧慧,田涛,等. 基于Verilog的FPGA整数分频器设计[J]. 北京:新技术新工艺,2015(4):40-42.

[2] 陆佳华,潘祖龙,彭竞宇. 嵌入式系统软硬件协调设计实战指南[M]. 北京:机械工业出版社,2014.

[3] 何宾. Xilinx All Programmable Zynq-7000 SOC设计指南[M]. 北京:清华大学出版社,2013.

[4] 何宾. Xilinx可编程逻辑器件设计技术详解[M]. 北京:清华大学出版社,2010.

[5] 夏宇闻. Verilog数字系统设计交叉[M]. 北京:北京航空航天大学出版社,2013.

[6] 宋建. 基于Fpga的精密时间-数字转换电路研究[D]. 合肥:中国科学技术大学,2007.

* 国家自然基金资助项目(11103069)

责任编辑彭光宇

Picosecond Counting Design Based on FPGA

TANG Haifeng, ZHAO Jianjun, WU Guangmin, WU Yaping, ZHAO En

(Kunming University of Science and Technology, Kunming 650500, China)

Abstract:In the actual FPGA design, there are not very good methods for counting under nanosecondtime. The implementation of the clock signal frequency doubling is usually used in official DCM or PLL.Due to the constraints of the hardware resources, the above method could not make the user deal with the clock signal for many times in free.The reason is that the numbers of DCM are limited in the internal device. Put forward a method to design time count based on the IODELA. Use hardware description language of Verilog HDL to count picosecond. Operate under nanosecond time based on IODELAY primitive and IDELAY primitive with Xilinx official Zedboard development board and Virtex5 development board. Propose a method of counting under nanosecond time based on primitive. Through the function simulation and board level validation, it is successful in implementation for 75 ps to 4 ns (main frequency 250 MHZ frequency) of high precision counting function. Implementation of picosecond count is very important for time measurement circuit of fine time (frequency frequency under 4 ns time is that time of the 75 ps to 4 ns), as well as for the FPGA nanosecond level below the clock operation. At present, the unit has been successfully used in the design of time measurement circuit.

Key words:field programmable gate array, primitive, picosecond count, functional simulation, frequency doubling

收稿日期:2015-06-23

通信作者:赵建军

作者简介:唐海峰(1988-),男,硕士研究生,主要从事嵌入式等方面的研究。

中图分类号:TN 40

文献标志码:A