一种低误码率的调制解调系统设计

2016-05-03西华师范大学电子信息工程学院肖顺文

西华师范大学电子信息工程学院 杨 湲 肖顺文

一种低误码率的调制解调系统设计

西华师范大学电子信息工程学院杨湲肖顺文

【摘要】根据FSK调制解调的原理,设计了调制解调系统,并在此系统上增加了信号跟踪模块,使得解调具有低门限特性,因此降低了数字信号解调时的误码率。本系统调制模块采用频率键控法设计,信号跟踪模块采用类似锁相环的方法实现,解调模块利用过零检测法实现,调制解调模块在之前的设计中已做出,本文主要着重实现信号跟踪以及低误码率解调功能。仿真结果表明:在调制解调系统加上信号跟踪模块以后,解调信号波形具有低误码率,高稳定性的特点。

【关键词】移频键控;信号跟踪;过零检测法;低误码率

0 前言

由于数字信号在传输过程中容易受干扰,干扰后容易产生误码现象,因此为了降低误码率,设计了信号跟踪模块。本文的调制解调模块均是采用文献[1]的设计即FSK调制模块和过零检测法实现的解调模块[2,3]。在之前的设计基础上,添加了信号跟踪模块,信号跟踪模块的输出与调制信号保持同步,实现了信号的跟踪功能,使解调模块具有低门限特性,降低了解调的误码率,使本设计系统具有更高的稳定性,优化了之前设计的调制解调系统,同时本设计中调制、跟踪、解调系统均采用顶层方法实现,简化了设计的复杂性、加快了设计与运行速度[1,4,5,6]。

1 调制、跟踪、解调原理

本设计中调制解调系统采用文献[1]的设计,即调制利用数字基带信号去控制选择开关来改变输出的频率成分,从而实现FSK调制[1,7],而解调则采用易于实现的过零检测法,即在一个单位时间内,检测信号波形通过零电平轴的次数来判断相关的频率成分[1,8]。本设计中难点就是实现信号跟踪,信号跟踪模块是在锁相环的理论基础上优化产生的。跟踪模块类似锁相环,却不同于锁相环的结构,其本质即是实现位同步,根据鉴相器输出的结果,不断地调整跟踪模块的输出,使跟踪模块的输出与调制信号保持同步[6,9]。由于本设计采用高频传输数字信号,低频成分较少,为了减少了仿真运行时间,因此本设计中没有加入低通滤波电路。信号跟踪模块是由鉴相器、双向时钟源、脉冲加减控制电路、以及2分频器构成。其中鉴相器是由异或门组成,双向时钟源是由D触发器和一些门电路构成,脉冲控制电路、2分频电路均是采用文本设计[6,10]。尤其是脉冲控制电路,它不同于锁相环的脉控电路,它是由一些逻辑关系采用文本设计组成,能够更好的实现脉冲加减。

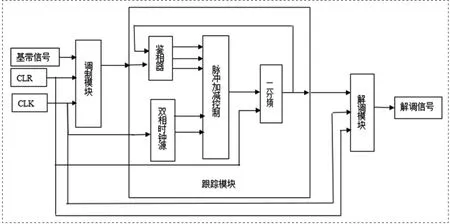

2 调制、跟踪、解调电路结构

调制、跟踪、解调电路结构如图1所示,基带信号输入到调制模块,在CLK,CLR信号作用下,输出调制信号。调制信号输入到跟踪模块,在CLK作用下,跟踪模块便产生一个与调制信号保持同步的跟踪信号,跟踪信号输入到解调器中,在CLK,CLR作用下,输出解调信号。采用跟踪信号作为解调模块的输入信号,使得解调模块具有低门限特性,降低了解调时的误码率[4]。

图1 调制、跟踪、解调电路结构

3 调制、跟踪、解调硬件电路

3.1跟踪模块设计

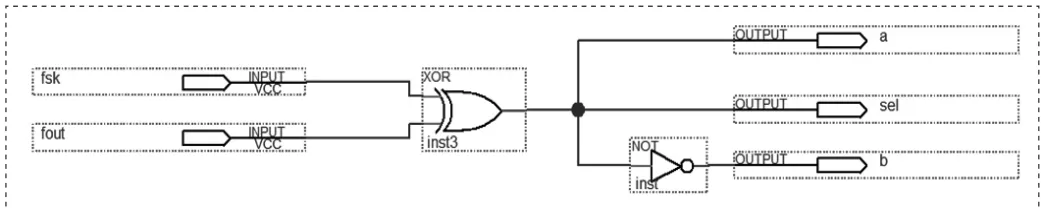

3.1.1鉴相器设计

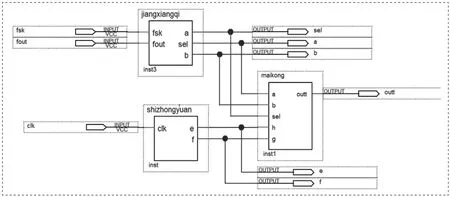

鉴相器是由一个异或门构成,原理图及仿真模块如图2所示,fsk为调制器输出的调制信号,fout为跟踪模块输出的反馈信号,sel为相位差信号,a、b为输出的超前、滞后信号[11,12]。

图2 鉴相器原理图

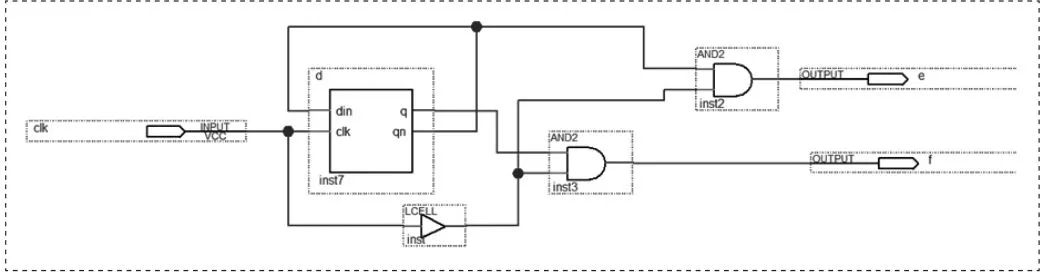

3.1.2时钟源模块设计

时钟源模块的作用是产生两路相位差为180度,占空比为25%的高频信号,给脉冲加减模块提供两个信号输入端[13]。其原理图以及仿真模块如图3所示,CLK为时钟信号输入端,e、f分别为两路相差为180度的高频信号输出端。

图3 时钟源原理图

3.1.3脉冲加减控制模块设计

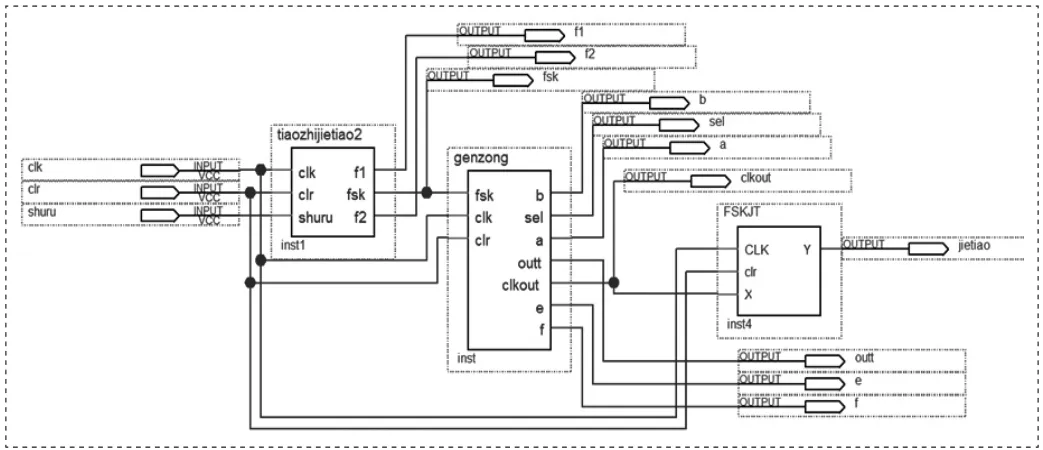

脉冲加减控制模块是由鉴相器、时钟源、脉冲加减设计逻辑(脉控模块)组成,脉控模块在a、b、sel、e、f信号的作用下控制脉冲的加减。其原理图以及仿真模块如图4所示,outt为输出的进行了加减变化的脉冲信号[14,15]。

图4 脉冲加减控制原理图

3.1.4跟踪模块构建设计

跟踪模块是由脉冲加减控制模块与2分频模块组成,2分频电路将脉冲加减控制模块输出的outt信号进行2分频,其原理图以及仿真模块如图5所示,clkout为输出的跟踪信号,也为脉冲加减控制模块的反馈信号。

图5 跟踪模块原理图

3.2调制、跟踪、解调系统设计

解调模块是采用文献[1]中的解调设计,调制、跟踪、解调原理图如图6所示,jietiao为输出的解调信号。

图6 调制、跟踪、解调模块原理图

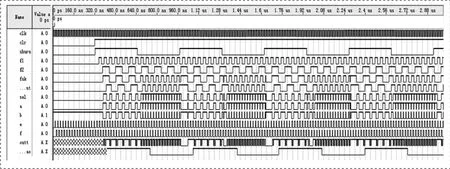

4 调制、跟踪、解调仿真结果

调制、跟踪、解调设计仿真图如图7所示,跟踪模块输出的clkout信号在CLK、CLR作用下经过解调模块,输出jietiao信号。从仿真图看出,输出信号和输入信号波形完全一致,误码率低,系统具有非常高的稳定性。

图7 调制、跟踪、解调仿真结果

5 结论

本设计是在之前的调制解调系统上,增加了信号跟踪模块,信号跟踪实现了对调制信号的同步功能,降低了解调时由于干扰而产生的误码现象的概率,优化了系统的结构,并且提高了系统稳定性。

参考文献

[1]杨湲,肖顺文,邹贵祥,易欢,李怡琳.基于FPGA的FSK调制解调系统设计[J].数字技术与应用,2014:161-164.

[2]张志聪.2FSK解调器前端设计[D].四川成都:电子科技大学,2010:3-4.

[3]周志法,艾文,张尧琴.基于FPGA的2FSK数字信号调制解调[J].电子科技,2012,25(3):121-123.

[4]季仲梅,王大鸣.通信中的同步技术及应用[M].北京:清华大学出版社,2008.

[5]庞浩,姐云霄,王赞基.一种新型的全数字锁相环[J].中国电机工程学报,2003:38-39.

[6]帅旗.基于FPGA的全数字锁相环的设计与实现[D].大连:大连理工大学,2013:6-16.

[7]段吉海,黄智伟.数字通信系统建模与设计[M].北京:电子工业出版社,2004.

[8]周志法,艾文,张尧琴.基于FPGA的2FSK数字信号调制解调[J].电子科技,2012,25(3):121-123.

[9]杨小牛,楼才义,徐建良.软件无线电技术与应用[M].北京:北京理工大学出版社,2010.

[10]张成.基于的全数字锁相环的设计与实现[D].合肥:合肥工业大学,2010:5-13.

[11]周群.基于FPGA技术的相位频率跟踪方法的研究[D].北京:北京化工大学,2009:45-46.

[12]王华军.基于FPGA的新型全数字锁相环的设计与实现[D].成都:电子科技大学,2015:11-15.

[13]严冬.基于VHDL语言的数字锁相环的设计与实现[J].中国科技论文在线,2007,5(2):436-437.

[14]王杰敏,杨虹.全数字锁相环的设计[J].通信电源技术,2009,26(3): 40-41.

[15]蒲晓婷.全数字锁相环的设计及分析[J].现代电子技术,2008,5: 173-174.

杨湲(1991—),女,四川广安人,西华师范大学电子信息工程学院硕士究生,主要从事软件无线电、EDA、SOPC等应用技术方面的研究工作。

肖顺文(1970—),男,四川金堂人,西华师范大学电子信息工程学院教授,主要从事软件无线电、EDA、SOPC等应用技术方面的研究工作。

(1)二阶RLC仿真电路的构建

利用Multisim10.0分别搭建RLC串联电路中电容电压、电感电压测试电路和电流测试电路分别如图2所示,图2中示波器XSC1的通道A测试电容电压,通道B测试电感电压,示波器XSC2的通道A测试电流给定L=1H,C=1F。

搭建电路时,在Multisim元件库中选择相应元件及测试仪器,构建测试电路,通过改变电阻R的取值,研究三种情况下的电路特性。

通讯作者:

作者简介:

基金项目:四川省教育厅科研基金重点项目(15ZA0145)。