基于可编程逻辑器件的G.703接口与以太网数据转换模块的设计

2016-04-24董小东

董小东

(国家知识产权局专利局专利审查协作四川中心,四川 成都 610000)

基于可编程逻辑器件的G.703接口与以太网数据转换模块的设计

董小东

(国家知识产权局专利局专利审查协作四川中心,四川 成都 610000)

G.703是电力系统、部队系统等国有大型系统中数据传输网络中普遍的接口标准,而以太网则是当今现有的最通用的通信协议标准,二者之间的通讯接口转换具有较强的实用价值和意义。为此,提出一种基于可编程逻辑器件的接口转换模块的设计,主要包括转换模块电路的硬件电路开发、逻辑算法设计。该接口转换模块的逻辑部分采用可编程逻辑器件进行设计,具有处理速度快、控制灵活、便于升级维护等特点,应用效果良好。

G.703;以太网;可编程逻辑器件;硬件设计;逻辑设计

G.703是电力系统、部队系统等国有大型系统中数据传输网络中普遍的接口标准,而以太网则是当今现有的最通用的通信协议标准[1],二者之间的通讯接口转换具有较强的实用价值和意义。G.703是将DCE(数字通信设备)连接到数据高速同步通信服务的(ITU)建议,G.703协议对各种速率的接口分别定义了功能特性和电气特性[2]。作为现代电信传输网使用的最为通用的传输标准接口,具有广阔的适用基础。以太网由于其成本低廉,分布广泛成为IP网中应用最多的实现方式[3]。实现G.703接口和以太网的数据转换,可以大大提升电信网与IP网的语音及其他数据融合,实现不同网络之间的资源共享优势互补。

1 系统设计

1.1 设计概述

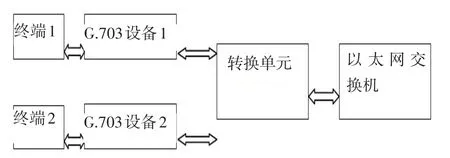

图1是接口转换模块的通用应用场所,符合G.703协议的硬件设备。G.703设备通过转换模块与以太网交换机输出的以太网数据进行数据转换,极大地方便了用户在不同网络之间的数据传输。针对市场中现有的转换模块基于微处理器实现转换功能,具有稳定性高、功能丰富的优点。与此同时,也带来了相当多的弊端,如产品开发周期长,成本难以控制,产品升级维护难度增大,降低产品的市场竞争力。为克服上述技术问题,本文选择可编程逻辑器件实现,利用可编程逻辑器件的硬件并行优势性能、较短的开发周期、低廉的开发成本、较强的稳定性以及升级维护的便利性等优点[4],大幅度提升该转换模块的市场竞争力。

图1 接口转换模块的通用应用场所

1.2 硬件设计

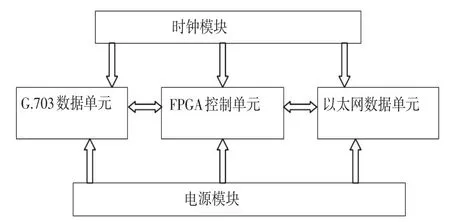

该转换模块主要采用以太网芯片、可编程逻辑器件和G.703接口芯片为主的硬件架构,实现多路G.703数据和以太网数据的转换处理。该转换模块的硬件结构如图2所示,包括核心处理单元、以太网业务单元、G.703业务数据单元、电源单元、时钟单元和复位单元。

图2 转换模块的硬件结构

选取可编程逻辑器件FPGA作为核心控制单元。其中,Altera和Xilinx是提供可编程逻辑器件的器件公司,可提供多个层级的芯片进行选择,由于Altera公司的QuartusII开发界面友好[4],选择Altera的CycloneIII喜乐的EP3C55芯片作为FPGA数据处理芯片。该芯片具备55 856个逻辑单元、2 396个RAM以及156个嵌入式18× 18乘法器。选取美信半导体公司的低功耗的G.703芯片DS21348,支持实现T1、J1线路接口。该芯片具有多种工作模式,可充分满足多种设计需求[5]。选择博通公司的以太网业务芯片BCM5228,实现以太网业务的处理。作为数字电路必不可少的电源模块和时钟模块,性能稳定、技术成熟是选择芯片的主要参考,基于以上原因选取LT1640芯片作为电源芯片及ICS83081的时钟芯片。采用全球最大的电子设计技术、程序方法和服务供应商提供的EDA软件——Cadence进行硬件电路设计,Cadence 17.0是cadence公司推出的能够跨IC、封装及印制板系统设计高性能互联。由于该转换单元中的FPGA及以太网业务芯片属于BGA封装,考虑到产品的信号完整性,设计多层印制板进而实现更好的信号处理效果,而Ca⁃dence17.0可以满足具备多层印制板的工具需求,是设计该转换器印制板的首选EDA[6]。

1.3 逻辑设计

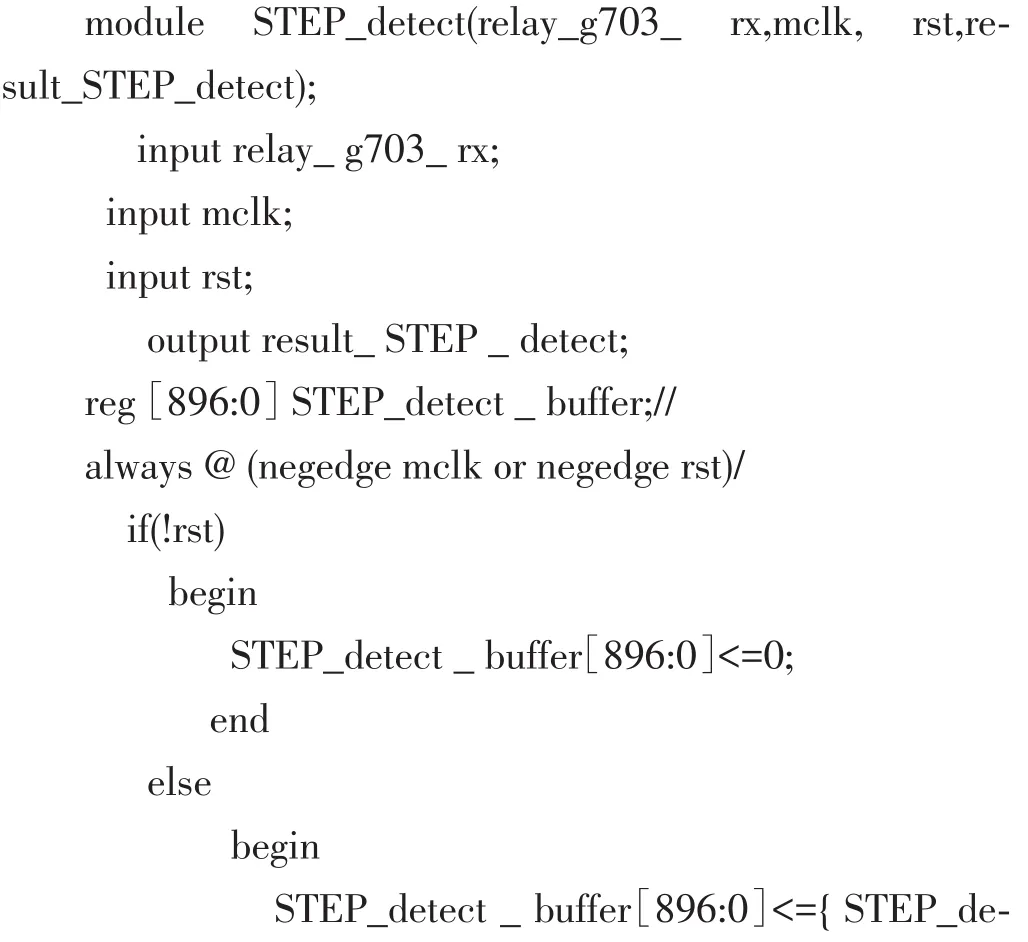

QuartusⅡ提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;芯片(电路)平面布局连线编辑;LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块;功能强大的逻辑综合工具。Verilog的设计初衷是成为一种基本语法与C语言相近的硬件描述语言[7]。本文的逻辑处理部分选择让电路设计人员更容易学习和接受的Verilog作为开发语言。基本逻辑处理流程如图3所示,为了更为高效地实现数据转换,选择自定义的G.703数据包格式包括包前导码、起始码、目的地址、数据源地址、数据长度及帧校验位。

图3 基本逻辑处理流程

G.703转换以太网数据包的逻辑处理过程为:接收G.703接口数据,判断数据包是否同步,如果该数据同步则对其安装标准以太网数据格式进行打包,其中包括添加数据包头、包类型及计算循环冗余码等处理。其中,数据包同步的处理过程如下:首先定义表示数据同步的标识码以及对端失步标识,对数据包头进行搜索,判断该包头是否具有同步标识码,如果具备该标识,则说明收发双向均为同步,则进行包头锁定,添加同步时间间隙,稳定同步状态。部分Verilog代码如下:

以太网转换G.703数据包的逻辑处理过程为:接收以太网数据,对该数据进行线路标识去除处理,进行串行数据转换至并行数据,验证处理后的以太网数据的目的地址及循环校验是否正确,将正确数据进行同步处理发送至G.703数据接收端,将错误数据进行丢弃,对代码编译仿真后进行单板调试。调试结果发现该转换单元转换效果明显优于现有产品。

2 结语

该G.703接口与以太网数据转换模块,通过Cadence公司的高效EDA开发工具进行多层印制板的设计,在保证信号完整性的前提下,最大程度地缩减了产品尺寸,根据Altera公司的可编程逻辑开发软件实现了数据业务的高效相互转换,缩短了开发周期,同时大大提升了系统升级维护的便利性。与此同时,随着可编程逻辑器件的进一步发展以及印制板生产工艺的提升,该转换器还有进一步提升的开发空间。

[1]王廷尧.以太网技术与应用[M].北京:人民邮电出版社,2005:1-25.

[2]雷祖康.10Base-T以太网数据到G.703E1的转换[J].产品与市场,2002(3):108-109.

[3]徐荣,龚倩,邓春胜.电信级以太网[M].北京:人民邮电出版社,2009:1-26.

[4]周孟然.CPLD/FPGA的开发与应用[M].徐州:中国矿业大学出版社,2007.

[5]MAXIM-IC.Application Note 324:T1/E1 Net-work inter⁃face Design[R].MAXIM-IC,2004.

[6]Howard W.Johnson,Martin Graham.High-Speed Digital Design:A Handbook Of Black[J].Prentice-Hall Inc.,1993(5):42-50.

[7]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2005.

Data Conversion Module Design of G.703 Interface and Ethernet Based on PLD

Dong Xiaodong

(Patent Examination Cooperation Center of the Patent Office,SIPO,Sichuan,Chengdu Sichuan 610000)

G.703 interface is the normal standard interface in the large communicate system,especially in the elec⁃tricity or army system.Ethernet is the most popular communicate protocol.There is stronger significant to make com⁃municate between them.Therefore,we designed the transform module based on PLD,which mainly included the hard⁃ware circuit development of the conversion module circuit and logic algorithm design.The logic part of the interface conversion module was designed with PLD,which has high processing rate,strong flexibility and update easily.It has good application effect.

G.703;ethernet;PLD:hardware design;logic design

TP391.1;TN79

A

1003-5168(2016)09-0029-03

2016-08-17

董小东(1983-),男,硕士,研究方向:语音识别。