基于FPGA的FSK信号发生器的设计

2016-04-22伊志勇哈尔滨工程大学信息与通信工程学院哈尔滨150001

刘 雨,伊志勇(哈尔滨工程大学 信息与通信工程学院,哈尔滨 150001)

基于FPGA的FSK信号发生器的设计

刘雨,伊志勇(哈尔滨工程大学 信息与通信工程学院,哈尔滨 150001)

摘要:介绍了FSK调制的理论基础,并且提出了一种基于现场可编辑门阵列(FPGA)和直接数字频率合成(DDS)技术的FSK数字调制系统硬件实现方法.总体设计采用了Xilinx FPGA为主控芯片并配合ISE和ModelSim等软件开发工具对整个系统进行设计、仿真和验证.本设计的实现方法简单新颖,系统可靠性高,同时可以将设计模块化,能较方便地移植用于其他基于FPGA 的数字通信系统,具有可移植性好、适用性高的优点.

关键词:DDS;FSK调制;FPGA

随着电子和电子设计自动化(EDA)技术的深入研究,DDS技术得到飞速发展,同时FPGA的设计有灵活、速度快等优点使得信号发生器的设计和实现更加容易和灵活[1].DDS与传统频率合成技术相比,具有频率分辨率高、频率切换速度快、频率改变时相位连续性保持不变和频率稳定度高等优点,因此极易实现信号的频率、相位和幅度控制[2].采用FPGA和DDS相结合的方式,使用单片FPGA实现FSK信号调制,具有全数字化易于集成的优点,节省了PCB面积,可灵活配置DDS参数[3].

1基于DDS的FSK调制技术

DDS是一种新的频率合成方法,在参考时钟的作用下,相位累加器对频率控制字进行线性累加,得到的相位码对波形存储器寻址,使之输出相应的幅度码,经过模数转换器得到相应的阶梯波,最后再通过低通滤波器对其进行平滑,得到所需频率的平滑连续的波形[4].

二进制移频键控(2FSK)是利用载波的频率变化来传递数字信息[5-6].在二进制情况下,0对应于载波f1,1对应载波f2,且载波之间的改变是瞬时完成的.2FSK信号波形可表示为:

(1)

二进制FSK信号,可通过模拟调频法来产生,也可以通过数字方式来产生,本设计采用的是模拟调频法,其原理图如图1所示.

图1 FSK调制原理框图

NCO1是由FPGA产生的频率为f0的正余弦基带信号,NCO2是由DAC5686产生频率为fc的正余弦信号,在数字序列控制下,选择送入Q路的基带信号是+sin2πf0t或者-sin2πf0t,从而在输出端得到cos2π(fc+f0)或者cos2π(fc-f0)t的信号.图2为FSK信号的频谱图,通过Matlab提供的randint函数产生概率相等的0,1序列,当产生0码时将其转化成-1,作为调制序列,仿真参数设定:

图2 FSK信号频谱图

1) 采样频率:fs=320 MHz;

2) NCO1频率:f0=3 MHz;

3) NCO2频率:fc=80 MHz.

2硬件实现方法

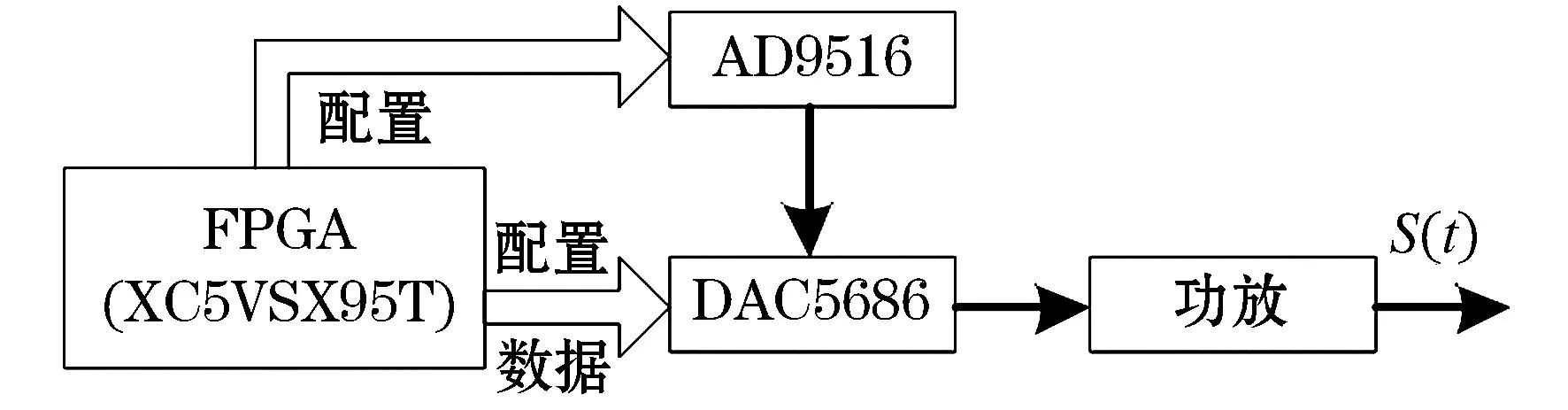

信号发生器硬件设计原理图如图3所示.其中AD9516为时钟芯片,经FPGA配置后产生320 MHz高速时钟供DAC5686工作.DAC5686是双通道16位高速数模转换器,有片内NCO,它通过32位的频率寄存器和16位的相位寄存器控制.

图3 硬件设计原理图

由取样定理可知,所产生信号的频率不能超过时钟频率的一半,在实际运用中,为保证信号的输出质量,输出频率不要高于时钟频率的1/3,以避免混叠或谐波落入有用输出频带内.本设计DAC5686片内NCO工作频率设置为320 MHz,输出频率设置为80 MHz,输出频率的计算公式为:

(2)

DAC5686提供了三种操作模式:双通道、单边带、正交调制.在正交调制模式下,可对正交输入信号进行插值滤波,经D/A变换后输出.基带I,Q分别通过图4中DA[15:0]和DB[15:0],以16位的数据形式、40MHz的数据速率送入DAC5686,经过8倍内插后与内部NCO进行混频,再经滤波后进行D/A变换,最后由IOUT1或IOUT2输出,输出信号的表达式为:

IOUT1=I(t)sinπfct+Q(t)cos2πfct

(3)

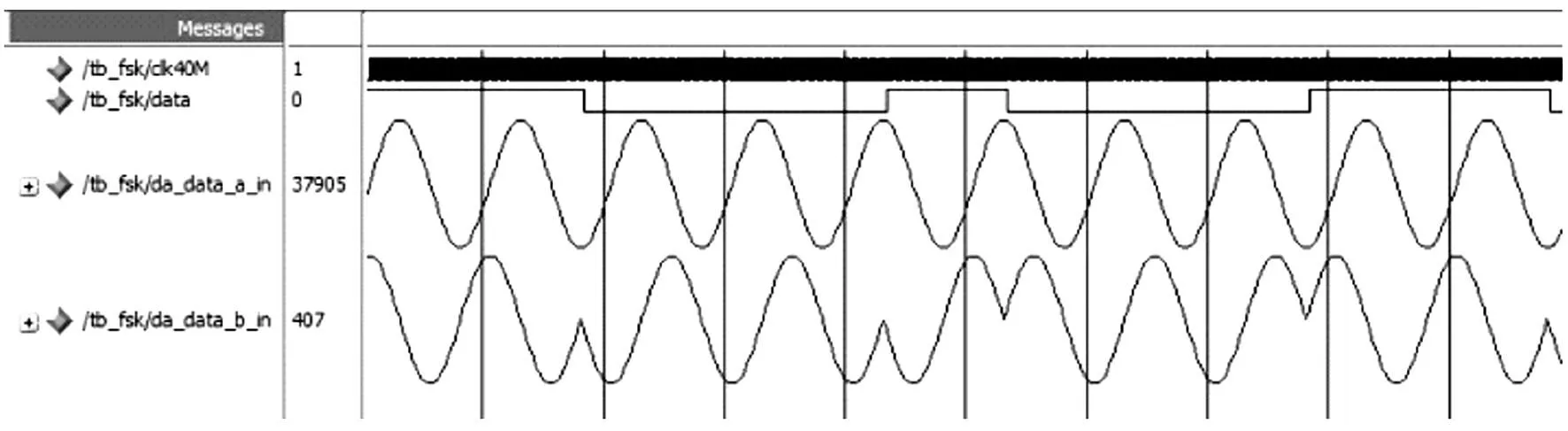

FPGA测试数据模块将产生0,1数字序列,此信号送入DAC模块用于控制DAC5686的I路和Q路数据;初始化将DAC5686中频设置为80MHz,正交调制模式.当选通“0”码时,DAC输出cos2π(fc+f0)t的余弦波;当选通“1”码时,DAC输出cos2π(fc-f0)t的余弦波.

图4 DAC5686正交模式工作原理图

图5 I,Q数据ModelSim仿真结果

3测试结果

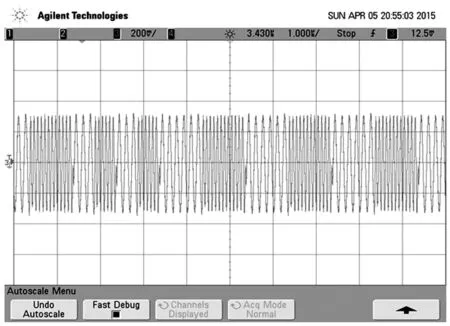

本设计采用了Verilog HDL语言,经过软件功能仿真验证,完成代码设计后,使用ISE开发工具进行综合与布局布线.此后,对系统进行了板级测试,将生成的配置文件下载到实验开发板上的FPGA 芯片实现设计,并进行相应的硬件调试.通过示波器观察系统输出的2FSK波形如图6所示.此时FSK信号的频率为77 MHz或者83 MHz.

图6 系统输出的2FSK信号波形

4结语

本文在理论研究分析的基础上,提出了一种基于 FPGA 的FSK数字调制系统设计方案,在代码设计完成的基础上,经过了功能仿真,最后在FPGA 实验开发板上完成了硬件实现与测试.该系统工作稳定,参数灵活可调,而且设计代码可移植性强.

参考文献:

[1]郑常胼. 基于FPGA和EDA硬件教学实验的设计与开发[D]. 天津: 天津大学, 2007.

[2]杨东霞, 巨永锋. 基于FPGA和DDS的数字调制信号发生器设计与实现[J]. 电子设计工程, 2013, 21(6): 90-93.

[3]田耘, 徐文波, 胡彬, 等. Xilinx ISE Design Suite 10.x FPGA 开发指南[M]. 北京: 人民邮电出版社, 2008. 1-12.

[4]张鑫. 基于FPGA的GNSS导航信号基带调制与控制技术研究[D]. 西安: 西安电子科技大学, 2011.

[5]孙志雄, 谢海霞. 基于FPGA的FSK调制解调器设计[J]. 现代电子技术, 2014, 09: 80-82.

[6]陈真,董丹丹.基于PMF的伪码捕获改进算法[J].哈尔滨商业大学学报:自然科学版,2015,31(4):477-480,485

Design of FSK signal generator based on FPGA

LIU Yu, YI Zhi-yong

(School of Information and Communication Engineering, Harbin Engineering University, Harbin 150001, China)

Abstract:The basic theory of FSK modulation was briefly introduced in this paper. A hardware implementation for FSK digital modulation system was put forward based on field-programmable-gate-array (FPGA) and direct digital synthesis (DDS) technology. The program used Xilinx FPGA as the main control chip, and design, simulate and verify the system by ISE and ModelSim software development tools. The implementation method of this design was simple and highly reliable. At the same time, it could be a modular design, easily transplanted to other digital communication system based on FPGA. Good portability and high applicability are also its advantages.

Key words:DDS;FSK modulator;FPGA

中图分类号:TN972

文献标识码:A

文章编号:1672-0946(2016)01-0064-03

作者简介:刘雨(1991-),男,硕士,研究方向:宽带信号的检测与识别.

基金项目:中央高校基本科研费专项基金(HEUCF140803)

收稿日期:2015-04-12.