基于FPGA的北斗导航电文译码器的研究与设计

2016-04-13郭里婷陈伟强

杨 坚,郭里婷,陈伟强

(福州大学 物理与信息工程学院,福建 福州 350002)

基于FPGA的北斗导航电文译码器的研究与设计

杨 坚,郭里婷,陈伟强

(福州大学 物理与信息工程学院,福建 福州 350002)

通过对北斗导航电文BCH纠错编译码方式的深入理解和研究,提出了一种基于并行数据处理的BCH译码器的设计方案。该方案利用FPGA对BCH电文进行并行处理,在一个时钟周期内实现电文译码,提高了BCH解码模块的译码效率;同时给出了系统各个模块的Modelsim仿真结果与分析,验证了设计的可行性。本设计对提高接收机的基带数据处理性能有一定的参考和指导意义。

北斗导航电文;BCH译码;并行处理;译码效率

0 引言

北斗卫星导航系统是中国正在实施的自主发展、独立运行的全球卫星导航系统,是继美国的全球定位系统(GPS)、俄罗斯的格洛纳斯卫星导航系统(GLONASS)之后第三个成熟的卫星导航系统[1]。2013年12月,《北斗系统公开服务性能规范(1.0版)》和《北斗系统空间信号接口控制文件(2.0版)》正式发布,意味着北斗卫星导航系统对区域提供的服务正式进入规范标准阶段。其中空间信号接口控制文件对北斗卫星导航系统的目标和B1I、B2I信号结构进行了详细定义[2]。

随着北斗系统的不断完善以及应用的深入,用户对北斗接收机的性能要求越来越高。为了提高接收机性能,设计方案必须考虑处理器的资源、速度以及存储空间等参数。如果接收机的大部分基带信号能够通过FPGA并行处理,那么对提高接收机的性能就具有非常大的意义。本文根据北斗导航电文BCH译码原理,提出了一种基于并行数据处理的快速BCH译码方式,并在FPGA系统上实现,提高了译码器效率。通过Modelsim对系统模块的功能仿真验证了设计的可行性,该设计方案具有一定的工程应用参考价值。

1 导航电文纠错编码数据格式

导航电文采取BCH(15,11,1)码加交织方式进行纠错[3]。BCH码位长为15 bit,信息位11 bit,纠错能力1 bit,其生成多项式为g(X)=X4+X+1。一组22 bit的导航电文数据码(表1所示),进入纠错编码系统后,按照每11 bit顺序分成两组后进行BCH(15,11,1)编码、交织操作,输出30 bit的交织编码。

表1 22 bit导航电文数据码结构

每两组 BCH(15,11,1)码按比特交错方式组成30 bit码长的交织码,30 bit码长的交织码编码结构如表2所示。

表2 30 bit交织码数据格式

2 导航电文纠错译码原理

接收机接收到数据码信息后按每1 bit顺序进行串/并变换,然后进行 BCH(15,11,1)纠错译码,再对交织部分按每11 bit顺序进行并/串变换,组成22 bit信息码,其译码流程如图1所示。

图1 译码原理框图

BCH(15,11,1)译码框图如图2所示,其中,初始时移位寄存器清零,BCH 码组逐位输入到除法电路和15级纠错缓存器中,当BCH 码的15位全部输入后,纠错信号ROM表利用除法电路的4级移位寄存器的状态D3、D2、D1、D0 查表,得到15位纠错信号与15级纠错缓存器里的值模二加,最后输出纠错后的信息码组[2,4]。纠错信号的ROM表详见参考文献[2]。

图2 BCH(15,11,1)译码框图

3 并行数据处理的纠错译码系统设计

3.1 系统总体方案

从传统的北斗导航电文BCH(15,11,1)译码原理(图2所示)可知,BCH译码器每一个时钟周期只处理一位码字,需采用频繁的循环移位实现译码,如果码组多了,将占用大量CPU资源并影响接收机对信号实时处理的要求[5]。鉴于传统译码方式的缺点,将图2所示原理框图进行改进,提出并行处理的一种运算方法。改进的纠错译码系统总体框图如图3所示。

图3 译码系统总体框图

考虑到数据是以数据流的格式输入到纠错译码系统中,所以直接将数据流给并行数据处理的译码单元并不现实。因此在单元前级加一级30 bit的串/并转换模块,将串行数据流转换成并行数据;为保证输出同样是数据流格式,译码单元后级再加一级22 bit的并/串转换模块。在实际应用过程中,为使信号保持同步状态,需要加入帧同步模块。并行处理的BCH译码系统,先将输入的30 bit的交织码数据流进行30 bit的串/并转换,输出30位并行的数据后输入BCH译码单元进行并行译码,在一个时钟周期输出22 bit的导航电文信息码进行后面的导航解算。

3.2 BCH并行译码单元设计

假设BCH译码模块(如图2所示)输入的15比特码为:{X1、X2、X3、X4…X13、X14、X15},那么根据图2的数据流动形式,BCH码与纠错信号标识{D3、D2、D1、D0}之间的关系可以表示为:

D0(0)=D1(0)=D2(0)=D3(0)=0

(1)

D0(i)=Xi⊕D3(i-1)

(2)

D1(i)=D0(i-1)⊕D3(i-1)

(3)

D2(i)=D1(i-1)

(4)

D3(i)=D2(i-1)

(5)

从最高位X1~X15顺序移位,最终得到BCH码对应的纠错标识信号{D3D2D1D0},上式中从i=1开始迭代运算,最后当i=15时,可以分别得到D3、D2、D1、D0的表达式[2,6]:

D3=X12⊕X9⊕X8⊕X6⊕X4⊕X3⊕X2⊕X1

(6)

D2=X13⊕X10⊕X9⊕X7⊕X5⊕X4⊕X3⊕X2

(7)

D1=X14⊕X11⊕X10⊕X8⊕X6⊕X5⊕X4⊕X3

(8)

D0=X15⊕X11⊕X8⊕X7⊕X5⊕X3⊕X2⊕X1

(9)

其中X1 X2…X14 X15表示15 bit的BCH码组。⊕代表模2加运算。

图4 并行结构译码

根据式(6)~(9),将图2的译码框图结构等效为图4所示并行数据处理的译码结构框图[7]。模块输入端数据采用15位的并行数据输入,在15位的数据输入之后,经过15通道的开关门组对输入的数据{X1、X2、X3…X14、X15}进行选择后进行模2运算得到相应的D3、D2、D1、D0值;其次根据纠错标识信号D3D2D1D0查找纠错标识信号对应的ROM表,得到15位的纠错信号;最后将所得15位纠错信号与输入的15位数据码进行模2运算后输出纠错译码。在FPGA系统中,该译码单元可以在一个周期内算出D3 D2 D1 D0,大大提高了运算速度。图5是并行译码单元的电路RTL视图。

图5 并行译码单元FPGA设计的RTL示意图

4 设计结果与仿真

本设计采用Verilog语言[8],在Quartus II 11.0开发软件平台下完成,仿真软件为Quartus II 11.0自带的Modelsim 6.6d版本。

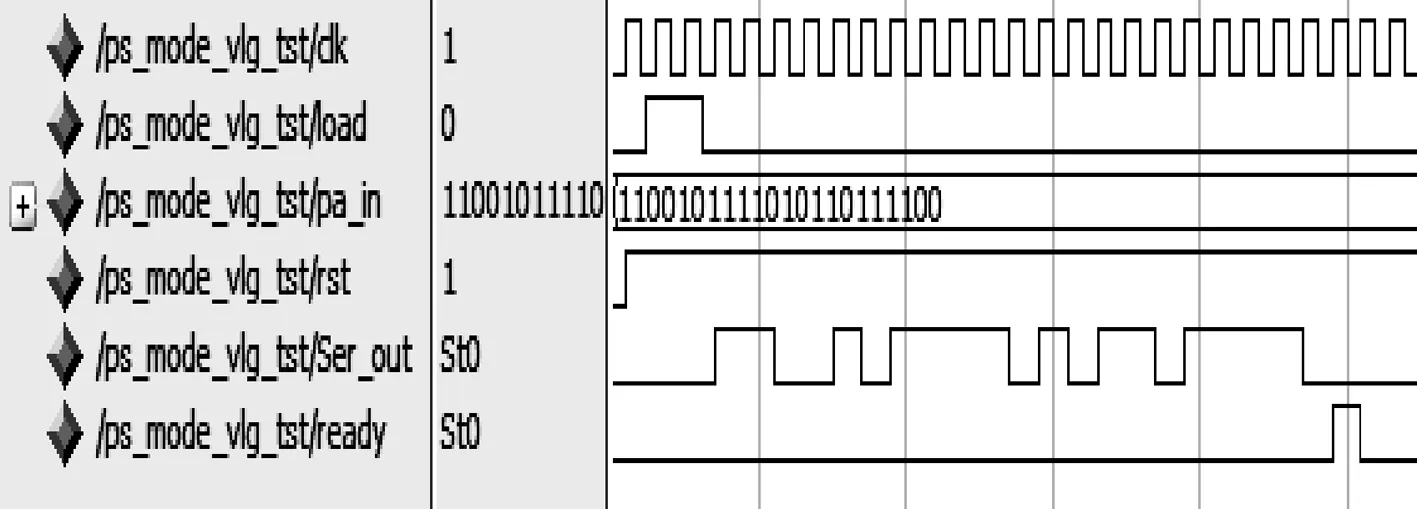

4.1 30 bit串/并转换器仿真

本设计30 bit串/并转换器目的在于将输入的一字数据流形式的30 bit交织编码转换成30 bit的并行数据输出。模块的Modelsim仿真图如图6所示。

图6 30 bit串/并转换器Modelsim仿真图

在系统时钟上升沿时将实际记录的卫星电文以数据流的形式从data_in输入,在完成30 bit的导航电文字段接收后,由data_out并行输出30 bit数据,同时在输出数据使能dout_en产生脉冲。

4.2 并行数据译码单元仿真

并行数据译码单元根据图4原理设计。实际设计中将两路的并行译码单元结构进行优化和合并,设计出支持30 bit的输入的并行译码单元,能够实现将30 bit并行输入的数据码进行22 bit BCH译码输出。其中30 bit交织码的解交织过程在模块内部实现。模块的Modelsim仿真图如图7所示。

图7 译码单元Modelsim仿真图

将实际测试得到的一个完整无误码的30 bit北斗导航电文字段作为仿真测试数据源并行输入。如图7所示,在一个时钟周期内,译码单元将并行30 bit数据解交织为or_data1和or_data2的两路15 bit数据,并根据本文设计的并行译码器分别计算出两路信号的纠错标识信号a、b。由于输入数据不存在误码,纠错标识信号和纠错信号re_data1、re_data2均为0,直接由两路数据中的11 bit信息位拼接得到22 bit数据输出data_out。

图8 译码单元纠错仿真

4.3 22 bit并/串转换器仿真

将译码单元的输出22 bit数据进行并/串转换为数据流输出到后级进行电文解算。若后级的处理器支持并行数据的输入,则并/串转换模块可以省去。模块的Modelsim仿真结果如图9所示。

图9 22 bit并/串转换模块Modelsim仿真图

北斗GEO卫星信号每比特电文长2 ms,一个导航字持续60 ms,非GEO卫星信号每比特电文长20 ms,一个导航字持续600 ms。传统译码器需要时刻记录导航电文比特流,通过复杂的移位实现译码,因此一台12路跟踪通道的接收机需要12路独立译码器。而本文设计的并行译码器译码周期短,只需在各通道增加串并转换模块和状态选择机制即可实现译码器的分时复用,提高了译码器使用效率。传统接收机和并行译码接收机的性能对比如表3所示。

表3 两种方式译码的性能对比

5 结论

经过仿真测试,验证了本文提出的基于FPGA的北斗导航电文译码器设计方案的可行性。该方案采用并行处理方式,在保证译码准确率的前提下有效提高了译码器的工作效率。此外,该译码器采用模块化设计,易于集成至接收机中,对北斗接收机译码模块设计有一定的参考意义。

[1] 邢金清,陈泓吉.北斗卫星导航系统现状及发展意义[J].黑龙江科技信息,2015(13):97.

[2] 中国卫星导航系统管理办公室.北斗卫星导航系统空间信号接口控制文件公开服务信号(2.0版)[Z].2013.

[3] 宁楠,鲍慧,宋文妙,等.一种基于FPGA的纠错编译码器的设计与实现[J].通信技术,2008,41(8):95-97,100.

[4] 王迪,郝士琦,朱斌,等.“北斗”2代B1I信号导航电文分析[J].航天电子对抗,2013,29(6):30-32.

[5] 连帅,闫利军,孙科,等.北斗2代卫星导航电文纠错校验设计与仿真[J].计算机测量与控制,2010,18(10):2344-2347.

[6] 蔺晓龙,何文涛,徐建华,等.多模 GNSS接收机中BCH(15,11,1)并行解码算法[J].微电子学与计算机,2014(2):50-53.

[7] 金婕,于敦山.高速并行BCH译码器的VLSI设计[J].北京大学学报(自然科学版),2009,45(2):233-237.

[8] 夏宇闻. Verilog数字系统设计教程[M].北京:北京航空航天大学出版社, 2008.

Research and design of the navigation message decoder based on FPGA

Yang Jian, Guo Liting,Chen Weiqiang

(College of Physics and Information Engineering, Fuzhou University, Fuzhou 350002,China)

Through the deep understanding and researching of the BCH error correcting codes, a design scheme of BCH decoder based on parallel data processing is proposed. The scheme uses FPGA to process BCH message in parallel, can realize message decoding in one clock cycle, which improves the efficiency of decoding of BCH decoding module. Also the scheme gives each module of the system with Modelsim simulation results and analysis to verify the feasibility of the design. The design has certain reference and guiding significance for improving the receive baseband data processing performance.

BDS navigation message;BCH decoding;;parallel processing;decoding efficiency

TN967.1;TN918.3

A

1674-7720(2016)01-0071-03

杨坚,郭里婷,陈伟强.基于FPGA的北斗导航电文译码器的研究与设计[J].微型机与应用,2016,35(1):71-73,80.

2015-08-15)

杨坚(1991-),男,硕士研究生,主要研究方向:卫星导航基带信号处理。

郭里婷(1976-),女,博士,副教授,主要研究方向:通信中的信号处理。

陈伟强(1989-),男,硕士,工程师,主要研究方向:卫星导航基带信号处理。

____________________