基于VHDL的高速数据链路设计应用*

2016-04-08范国生

范国生

(武汉市人民检察院信息网络中心 武汉 430015)

基于VHDL的高速数据链路设计应用*

范国生

(武汉市人民检察院信息网络中心武汉430015)

摘要为解决雷达系统中各子系统之间数据的实时、高速、可靠传输问题,设计了一种基于VHDL的高速数据传输链路方案。论文根据数据传输协议和数据传输时序关系,给出了设计思路和具体实现方法,并通过仿真和实际应用验证了该设计的可行性,该设计已成功应用于某型雷达上。

关键词高速数据传输链路; VHDL; 低压差分信号

Design and Application of High Speed Data Link Based on VHDL

FAN Guosheng

(Information Network Center, The People’s Procuratorate of Wuhan, Wuhan430015)

AbstractIn order to solve the real-time, high-speed, reliable transmission of data between the subsystems in the radar system, this paper describes the design of a high speed data transmission link based on VHDL. According to the data transmission protocol and data transmission timing relationship, this paper gives the design ideas and realization method, and the feasibility of the design is verified by simulation and practical application. The design has been successfully applied in a radar system.

Key Wordshigh speed data transmission link, VHDL, LVDS

Class NumberTN911

1引言

随着距离分辨力的提高和工作带宽的增加,现代雷达系统需要快速采集、准确传输大量的雷达回波信息并对这些信息进行处理和提取,雷达系统中各子系统之间要传送大量的数据,这些数据的实时、高速、可靠地传输成为构建现代雷达系统必须要解决的关键问题[1],而在现代数字系统互联数据传输中,传统的并行总线已不能满足高速数据传输的需求[2]。本文针对某型雷达的技术要求,设计了一种基于VHDL[3]的高速数据传输链路,电路功能在FPGA上实现,并通过仿真和实际应用,验证了设计的可行性。

2系统设计方案

2.1系统设计思路

传统的雷达系统一般都是运用共享总线结构式的并行总线来实现数据传输[4],由于并行共享总线在时序同步、信号偏移、抗干扰能力、设计复杂度和设计成本等方面存在一定的缺陷,传统的并行共享总线己经不能够满足等现代雷达对数据传输的需求,高速数据传输的实现方法转向了串行方式[5]。高速串行数据通讯通常把时钟信号嵌入到数据当中,在接收端使用时钟数据恢复,从数据中提取同步时钟信号来恢复数据,当输入数据和输入时钟不同步,不满足建立与保持时间要求,或串行链路只传输数据、无同步时钟,则给串行数据恢复带来困难[6~7]。

基于上述问题,本方案将数据和同步信号各采用独立链路,确保数据传输的可靠性和完整性。物理链路层的传输性能也是制约高速串行数据链路传输性能的关键因素之一,方案采用低压差分信号[8](Low Voltage Differential Signaling,LVDS)接口技术。LVDS传输接口具有高速率、低功耗、低噪声和低电磁干扰等优点,可实现数据的高速、可靠远距离传输[9~10]。

雷达信息数据和同步信号的处理用VHDL硬件描述语言程序设计,电路功能在FPGA上实现,物理链路层设计采用LVDS标准接口芯片,使得设计能灵活方便地融合到雷达系统整体设计中,实现了数据传输链路的模块化、可移植化。

2.2系统结构

图1 系统结构图

系统由发送模块、同步信号产生模块、LVDS电平转换模块、接收模块组成(见图1)。数据编码模块将回波信号数据、目标参数数据根据相应的传输协议编码为含有起始位和终止位的数据组,编码后的数据组在导前触发、同步时钟和帧同步信号的同步下经并串转换形成高速串行数据流。LVDS接口将数据流数字信号转变成差分信号,差分信号在物理链路上传输。接收模块在导前触发、同步时钟和帧同步信号的同步下接收串行数据,解码电路将接收的回波信号数据、目标参数数据按照相应的传输协议还原为原始数据。

3方案实现

3.1数据传输时序

数据传输时序如图2所示,本设计中数据信号和同步信号各占用独立链路,导前触发信号是雷达系统的主同步信号,雷达系统以此信号同步工作,同步信号产生模块在导前触发的同步下利用时钟信号产生帧同步信号,帧同步信号周期由数据宽度决定,本设计中数据宽度为8bits。数据在帧同步和时钟的同步下在数据链路中串行传输。

图2 高速数据链路时序图

3.2数据传输协议

方案中高速数据链路要传输的数据主要有回波信号数据和参数数据,参数包括目标的点迹信息(方位、距离、高度、杂波状态、时间等)和雷达当前的工作参数(方位、频率、波形、重复频率等)。回波信号数据占用一个数据传送链路,I路传送8bits正常回波信号,Q路传送8bits处理后回波信号。参数数据的传送占用一个数据链路,I路传送点迹信息,Q路传工作参数。

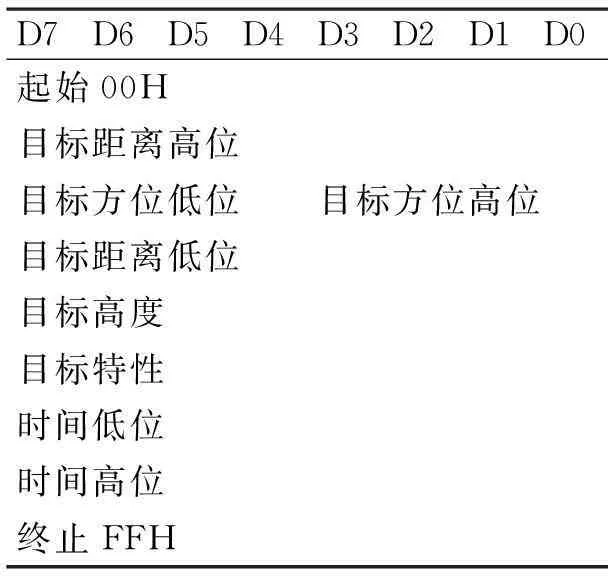

目标点迹数据传输协议如表1所示。

工作参数数据传输协议如表2所示。

3.3系统功能模块设计

系统用VHDL语言程序设计完成,电路功能在FPGA上实现,本文以工作参数数据传输为例,阐述高速数据链路方案设计实现过程。

表1 目标点迹数据传输协议

3.3.1发送模块设计

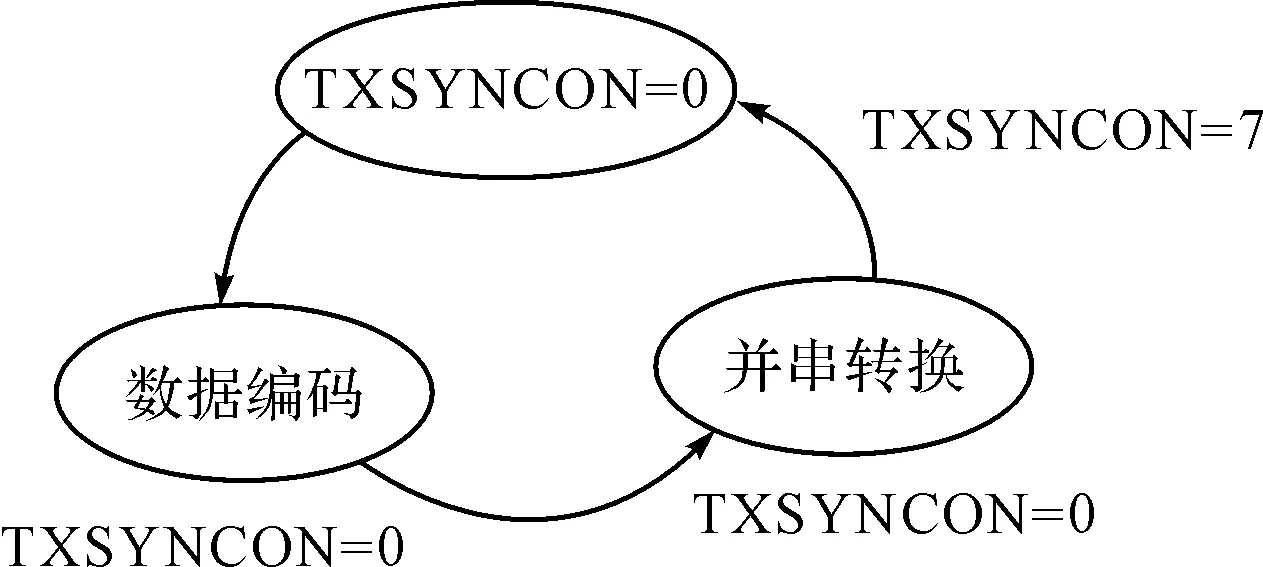

在发送模块程序设计中,设计一个TXSYNCON帧同步计数器,对帧同步信号计数,当计数满7(工作参数数据帧数)时TXSYNCON清零。可根据TXSYNCON计数值将电路设定为两种状态(见图3),计数值等于0时为数据编码状态,此状态下电路完成: 1) 将天线方位、工作参数按工作参数数据传输协议存入发送数据缓存器; 2) 起始位发送。计数值为1~7时为数据并串转换状态,此状态下电路完成工作参数及数据终止位数据串行发送。

表2 工作参数数据传输协议

图3 数据发送状态图

3.3.2接收模块设计

在接收模块程序设计中,数据串并转换和数据解码两个功能块同步并行工作,串并转换功能块实时接收数据,数据解码功能块根据传输协议对接收的数据解码还原。

· 数据串并转换:以帧同步为同步信号,每个时钟信号上升沿接收串行数据并存入数据缓存器,每个接收帧周期内缓存器中的数据即为发送端发送的工作参数数据组中的一帧数据,数据由串行转为并行。

· 数据解码:数据解码分为等待起始位和数据还原两种状态(见图4)。设计一个状态标记SYNflag,电路初始状态为SYNflag=0状态,即等待起始位状态,此状态下完成: 1) 判断数据还原状态下参数数据缓存中最后一帧数据是否为终止位,如果是终止位则按传输协议输出相应工作参数数据; 2) 等待接收数据起始位,一旦接收到起始位,置状态标记SYNflag为1,电路进入数据还原状态。数据还原状态下完成: 1) 设计一个RXSYNCON帧同步计数器,对帧同步信号TXSYN计数,计数器宽度根据工作参数数据组长度定制,计数器计满表示接收完一组数据,计数器清零,置状态标记SYNflag为0; 2) 将接收到的数据按帧存入参数数据缓存。

图4 数据解码状态图

4系统仿真及实际应用

4.1仿真测试分析

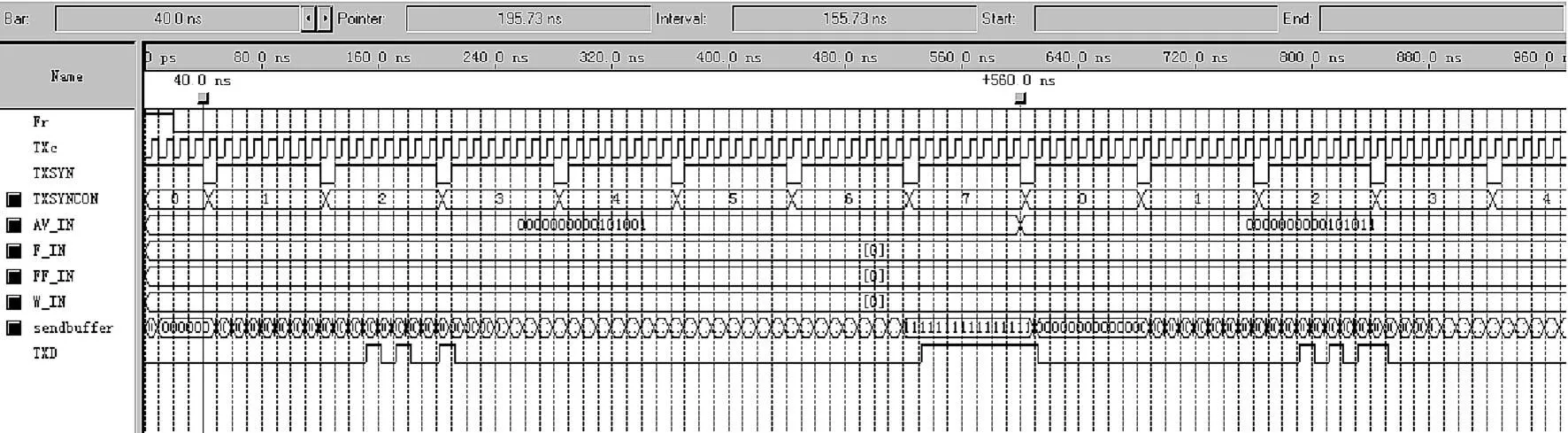

为了验证设计方案的正确性和可行性,在QuartusⅡ软件平台下对发送模块和接收模块进行时序仿真,仿真结果如图5和图6所示。

图5为工作参数发送仿真结果图。TXC为发送时钟信号,TXSYN为发送帧同步信号,TXSYNCON为帧同步计数器,AV_IN为天线方位数据,W_IN等为其它工作参数,TXD为发送的串行数据。图中显示两组工作参数发送结果,TXC时钟设定为100MHz,天线方位参数AV_IN设定为二进制数101001和101011,其它参数设定为0,图中仿真结果显示:TXSYNCON为0状态时,电路读入工作参数数据,TXSYNCON为1~7状态时,电路正确发送含起始位、参数位和终止位的TXD串行数据,仿真结果符合设计要求。

图5 发送模块仿真图

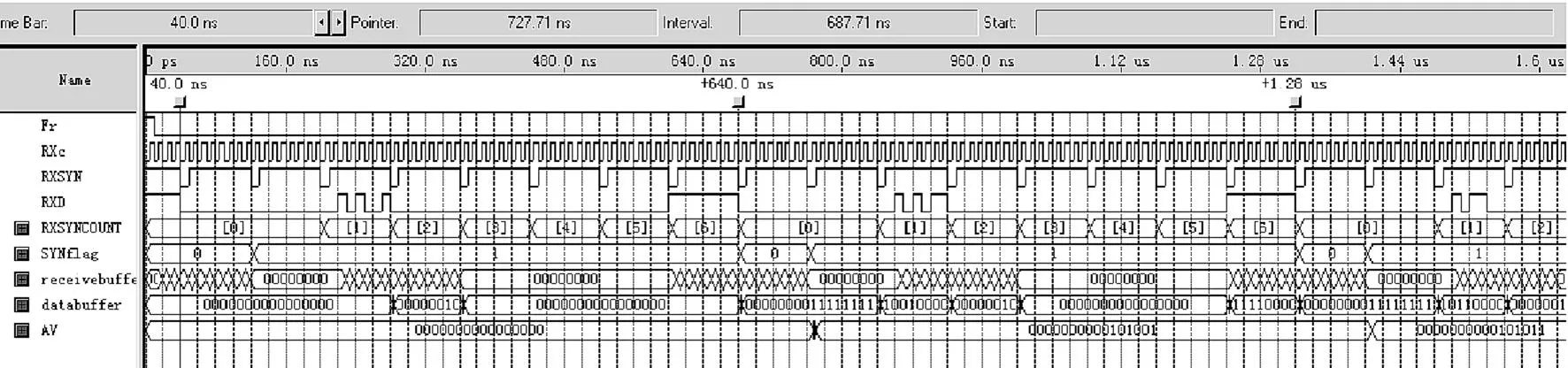

图6为工作参数接收仿真结果图。RXC为100MHz时钟信号,RXSYN为帧同步信号,RXD为串行接收数据,AV为接收的天线方位参数数据。仿真时电路接收两组发送模块发送的参数数据,AV输出值为101001和101011,仿真结果符合设计要求。

图6 接收模块仿真图

4.2实际应用效果

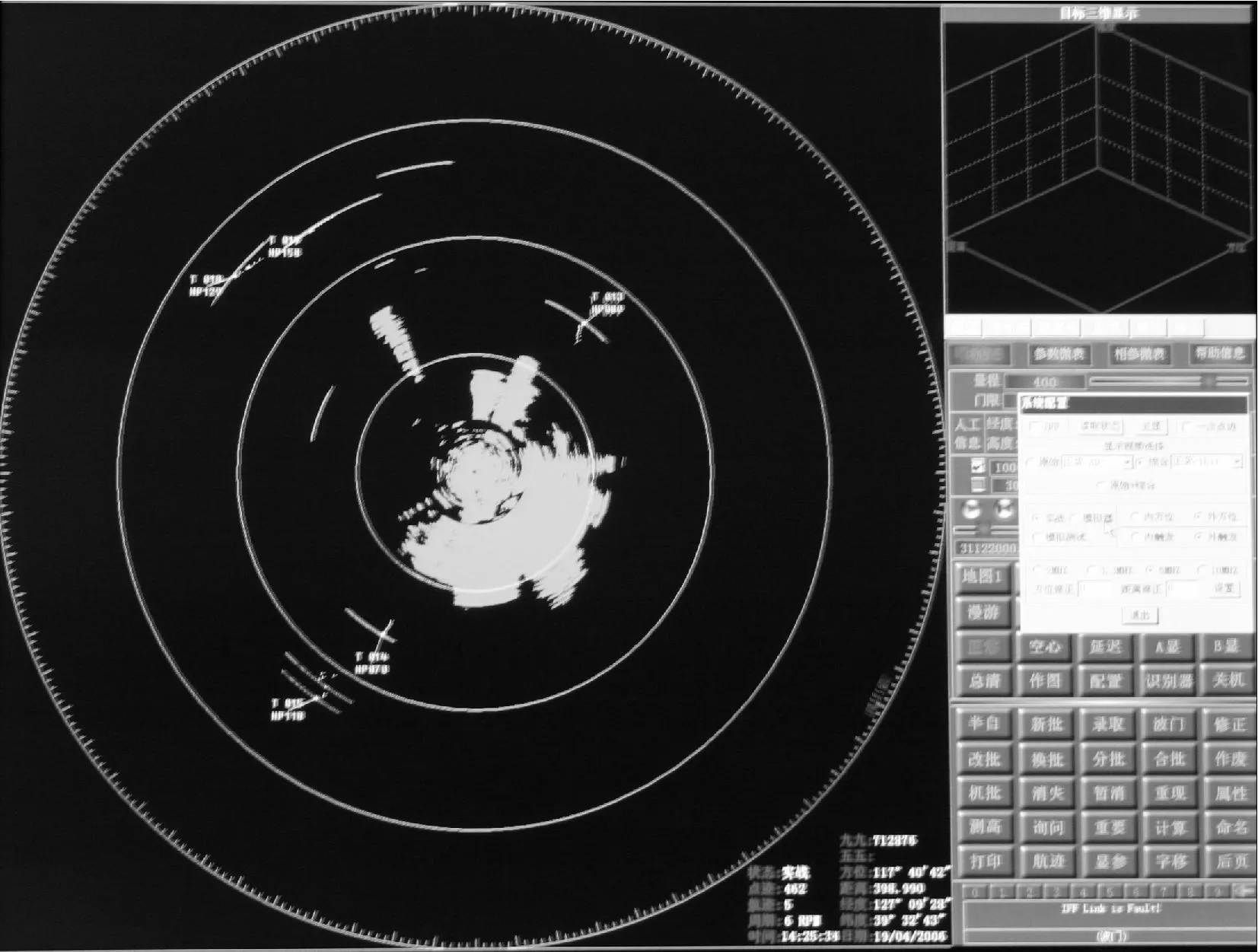

将设计应用于某雷达系统,雷达在正常工作状

态下探测目标,探测结果在雷达显示等终端设备上显示,终端显示结果如图7所示,图中显示了雷达回波信息和回波点迹以及工作参数信息。通过检飞等实践测试,结果证明:该设计符合要求。

图7 雷达终端显示

5结语

本文针对某型雷达技术要求设计的高速串行数据传输链路,解决了雷达系统中各子系统之间数据的实时、高速、可靠地传输问题,目前此设计已在该型雷达上得到了很好的实际应用,证明了设计具有一定的实用价值。

参 考 文 献

[1] 张克功,李和平,高鑫.基于千兆以太网的雷达数据可靠传输系统设计[J].自动化与仪表,2012(6):26-31.

[2] 李大鹏,李雯,王晓华.基于FPGA的高速LVDS接口的实现[J].航空计算技术,2012(5):115-118.

[3] 侯伯亨,刘凯,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].第三版.西安:西安电子科技大学出版社,2009:4.

[4] 邢乃福.雷达高速数据传输技术研究[D].成都:成都电子科技大学,2013.

[5] 谢丽斌.高速串行数据传输机制及其交换技术研究[D].西安:西安电子科技大学,2012.

[6] 曲伟,孙志安.基于FPGA实现高速串行链路数据恢复的方法[J].计算机测量与控制,2011,19(1):219-221.

[7] Xue LIU, Qing-xu DENG. High-speed, fixed-latency serial links with Xilinx FPGAs[J]. Journal of Zhejiang University-SCIENCE C(Computers&Electronics),2014,15(2):153-160.

[8] ANSI/TIA/EIA-644-A-2001. Electrical Characteristics of Low Voltage Differential Signaling(LVDS) Interface Circuits[S]. Arlington, VA: TELECOMMUNICATIONS INDUSTRY ASSOCIATION,2001.

[9] 李霄光.基于LVDS高速串行总线通信技术的研究[D].西安:西安电子科技大学,2012.

[10] 童子权,白锦玲.LVDS传输技术在高速数据采集系统中的应用[J].国外电子测量技术,2009,28(2):59-61.

中图分类号TN911

DOI:10.3969/j.issn.1672-9730.2016.01.017

作者简介:范国生,男,硕士,工程师,研究方向:计算机模拟仿真。

基金项目:检察技术(编号:JBKY20150620)资助。

*收稿日期:2015年7月1日,修回日期:2015年8月27日