基于Camera Link的数据采集与处理系统设计

2016-03-31周敬东周明刚黄云朋李敏慧

周敬东, 程 钗, 周明刚, 黄云朋, 李敏慧

(湖北工业大学农机工程研究设计院, 湖北 武汉 430068)

基于Camera Link的数据采集与处理系统设计

周敬东, 程钗, 周明刚, 黄云朋, 李敏慧

(湖北工业大学农机工程研究设计院, 湖北 武汉 430068)

[摘要]在色选领域中,针对高频相机要传输和处理的数据量大的特点,采用FPGA作为处理芯片,设计基于Camera Link标准的高频线阵CCD数据采集与处理系统。该系统运用FPGA芯片完成数据采集和时序控制,高性能DSP完成复杂的算法运算。阐述系统的整体设计思路、硬件结构和工作流程,包括Camera Link接口技术、高速缓存,FIFO接口技术以及图像输出控制等。该系统经过试验验证,能够稳定地实现图像数据的传输、存储与处理。

[关键词]图像采集; 图像处理; FPGA; FIFO; Camera Link

广泛应用于农产品色选、微电子、工业检测等领域的机器视觉技术,其大部分处理系统主要是基于PCI、USB数据采集系统[1]。这些数据采集系统通过上位机实现数据的实时处理和动态显示,成本高,体积大,难以适应一些特定的工作场合。随着图像处理数据量的增大,图像实时显示占用了大量的资源。而在FPGA的控制下,可通过串并转换和乒乓存储完成图像数据的采集,充分利用FPGA和DSP的内部资源优势,最终将数据传输给DSP处理[2]。

1Camera Link接口协议

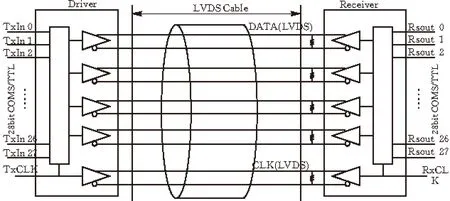

Camera Link[3-4]是在Channel Link技术基础上发展而来的。使用一个并转串驱动器和一个串转并接收传输数据,数据通过Cameralink电缆传输,接收器接收4 组 LVDS数据信号和1组LVDS时钟信号,将数据流转换回28位的COMS/TTL并行数据信号和1路时钟信号。由此可见,Channel Link使用5对线缆完成了28位数据信号和1路时钟信号的传输,减少了线缆的使用数量。

图1显示了Camera Link原理。

图 1 Camera Link原理图

2系统整体设计

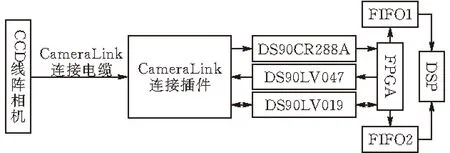

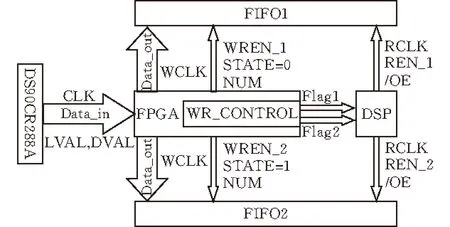

高速图像采集与处理系统的硬件结构如图2所示。在该系统中,首先由Camera Link接收器DS90CR288A[5]将相机输出的5对LVDS 信号转换成LVTTL信号,并通过Camera Link电缆将图像数据送入到FPGA中,FPGA对接收到的图像数据做预处理,然后把数据存入FIFO。图像数据在存入FIFO的过程中采用乒乓存储方式[6]循环存储两组FIFO,即当FIFO1写完一帧图像数据后,FPGA产生中断标识flag1,且DSP开始读FIFO1中的数据,写FIFO1时读FIFO2,写FIFO2时读FIFO1……此过程由FIFO控制器对其切换操作。根据设计,由于是写完数据后再由DSP读取数据,所以不会造成数据丢失。DSP读取FIFO中的24位数据并存入内存中以便后续复杂的算法处理。DSP处理完一组数据之后产生一个标识位,控制后面的执行机构动作。整个高速图像实时处理系统包括以下几个单元模块:Camera Link接口模块、FIFO控制器产生模块、DSP读取FIFO模块。

图 2 系统硬件框图

3系统关键模块设计

3.1Camera Link接口模块设计

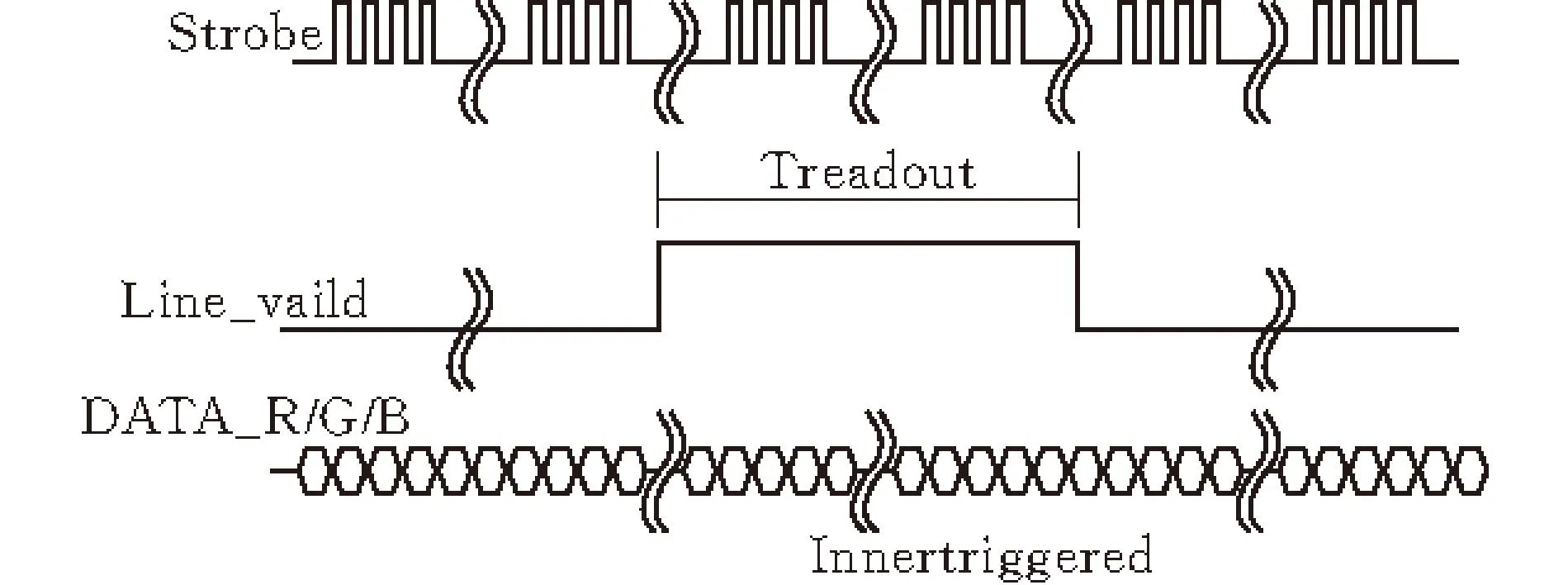

Camera Link采用LVDS信号传输,根据Camera Link协议标准,硬件电路接口要实现的功能包括5路LVDS信号转化为COMS/LVTTL信号、相机的控制、采集卡和相机的通讯,分别采用DS90CR288A、DS90LV047、DS90LV019来实现[7]。Camera Link信号分为图像数据信号、相机控制信号、异步串行通信信号,其中数据信号为28位,其中包括24位数据信号和4位使能信号。4位使能信号分别定义为:帧有效信号(FVAL),高有效,反向为帧同步信号;行有效信号(LVAL),高有效,其反向为行同步信号;数据有效信号(DVAL),只有在数据信号高时,输出的数据才是有效数据;保留信号(SPACE)。相机控制信号分别为外部同步信号(CC1)、像素重置信号(CC2)、向前信号(CC3)和保留信号(CC4);用于采集卡与相机之间的异步串行通信信号SerTC,用于相机和图像采集卡之间的异步串行通信SerTFG,根据工程需要和CCD线阵相机的具体设置(内触发等),本系统采用的是科亿公司的L1000线阵相机,设计只考虑数据传输的同步信号以及相机控制信号。图3为相机输出时序图。Strobe是像素输出同步时钟,Line_valid为行有效信号,DATA为数据信号,只有当行有效为高时,在像素输出同步时钟的上升沿采集到的数据才是有效数据。

图 3 相机输出图

3.2FIFO控制器设计

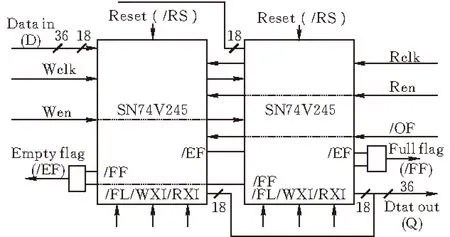

FIFO(First In Fist Out))是一种常用于数据缓存的电子器件,可应用于不同时钟域的高速数据采集、多处理器接口和视频信号的时序控制等领域。由于FIFO不需通过地址的操作,而是通过读写和其他的控制信号线,先进先出的方式读取数据,设计上相对简单,综合考虑存储时间和DSP读取时间等因素,本设计选用TI公司的SN74V245[8],该芯片容量为4096×18bit,最大随机存储时间为5 ns。因为FIFO要接收FPGA传来的24位数据,故对FIFO进行宽度扩展。扩展接口示意图如图4所示。

图 4 FIFO宽度扩展连接图

图 5 FIFO控制器原理框图

由于CCD线阵相机实时输出的数据量比较大,速度快,且实时性要求较高,因此系统采用两组FIFO交替存储。首先FPGA检测相机输出数据行有效信号Line_valid的上升沿,随后将接收到的图像数据缓存到FIFO1中。当缓存数据计数器NUM=2670时, FPGA将中断标识符Flag1置高一个时钟周期,DSP检测Flag1上升沿并开始读取,直至读空;同理,在读FIFO1的同时写FIFO2,而在读FIFO2时对FIFO1进行写操作。图5为FIFO控制器的设计框图。FPGA采集到的并行数据Data_in以及时钟信号CLK分别输入到两个FIFO中,FVAL、DVAL、NUM等信号输入到写控制器中,读写的切换由计数器num和状态标志信号state来控制,首先控制器写FIFO1,当num计数达到2670个像素点时,读切换标志寄存器Flag1置高一个时钟周期,写状态寄存器state通过检测Line_valid的上升沿取反,state=0时写fifo1,state=1时写fifo2,DSP检测到Flag1上升沿,开始读FIFO1;同时FPGA写FIFO2,检测到Flag2上升沿,开始读FIFO2,同时FPGA写FIFO1。数据就通过控制器无缝不间断地存储和传输(图5)。

3.3DSP数据接收与图像处理模块

本设计的系统硬件平台选用以TI公司的高性能DSP芯片TMS320F28335(简称28335)为核心芯片器件。28335是一款高性能 32 位 CPU,单精度浮点运算单元,采用哈佛流水线结构,能够快速执行中断响应,其主频高达150 MHz(6.67 ns 周期时间),16位或32位外部接口,多达2个控制器局域网(CAN)模块等。

系统上电后首先对变量进行初始化,再进行系统初始化,开启外部中断。当DSP接收到FPGA 的外部中断信号后,DSP调用色选函数DataReceive(),开始通过DMA方式读取FIFO中图像数据并存入DSP的内存中[9-10]。当达到处理行数时,DSP调用色选函数Colorsort();对每一个通道内R、G、B三个分量值均小于预定值的像素点归为背景,剩下的即为待处理像素点,将待处理像素点与上位机设定的R、G、B阈值比较,满足阈值的即为有效像素点。 所有通道待处理像素点完成比较后,计算出有效像素点数P与待处理像素点数q的比值m。其中所有待处理像素点表示通道内物料面积的大小,所有有效像素点表示通道内物料特征面积的大小。计算后n为通道内的物料特征面积占总面积的比值。将m与基准值n进行比较,判定是否输出控制信号驱动执行机构去除物料。

4仿真与测试

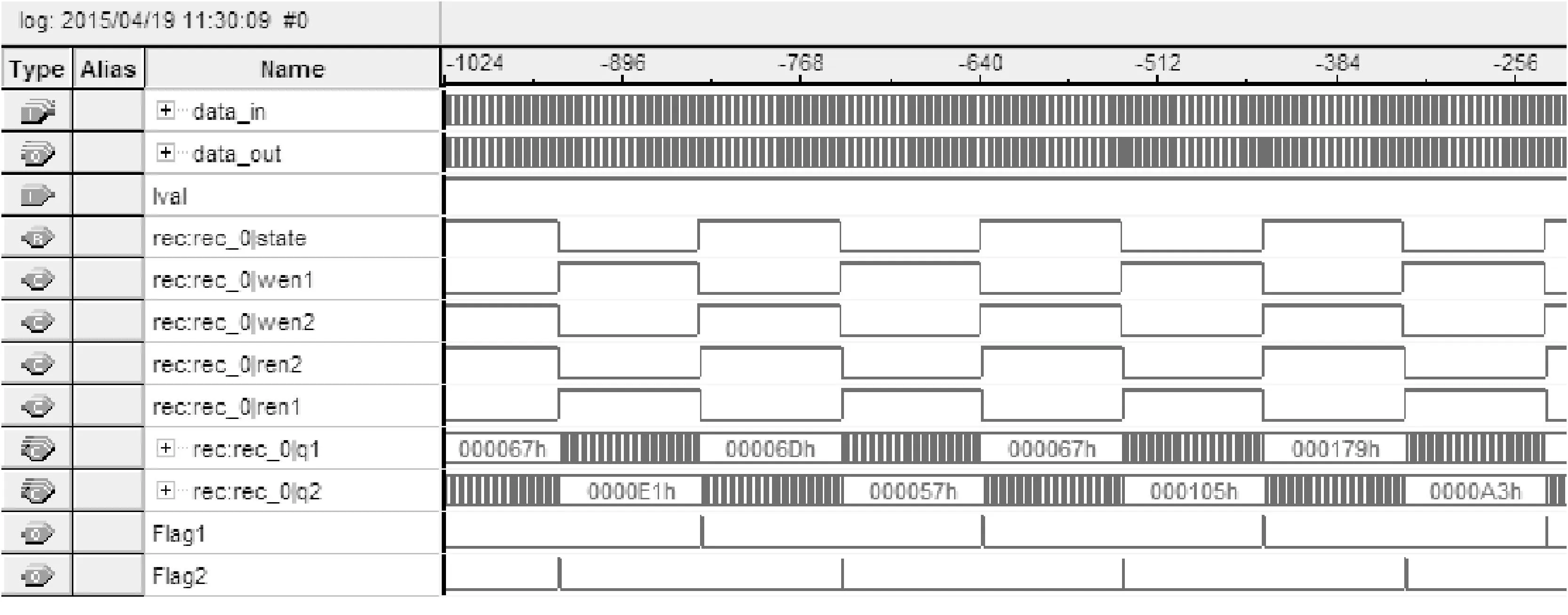

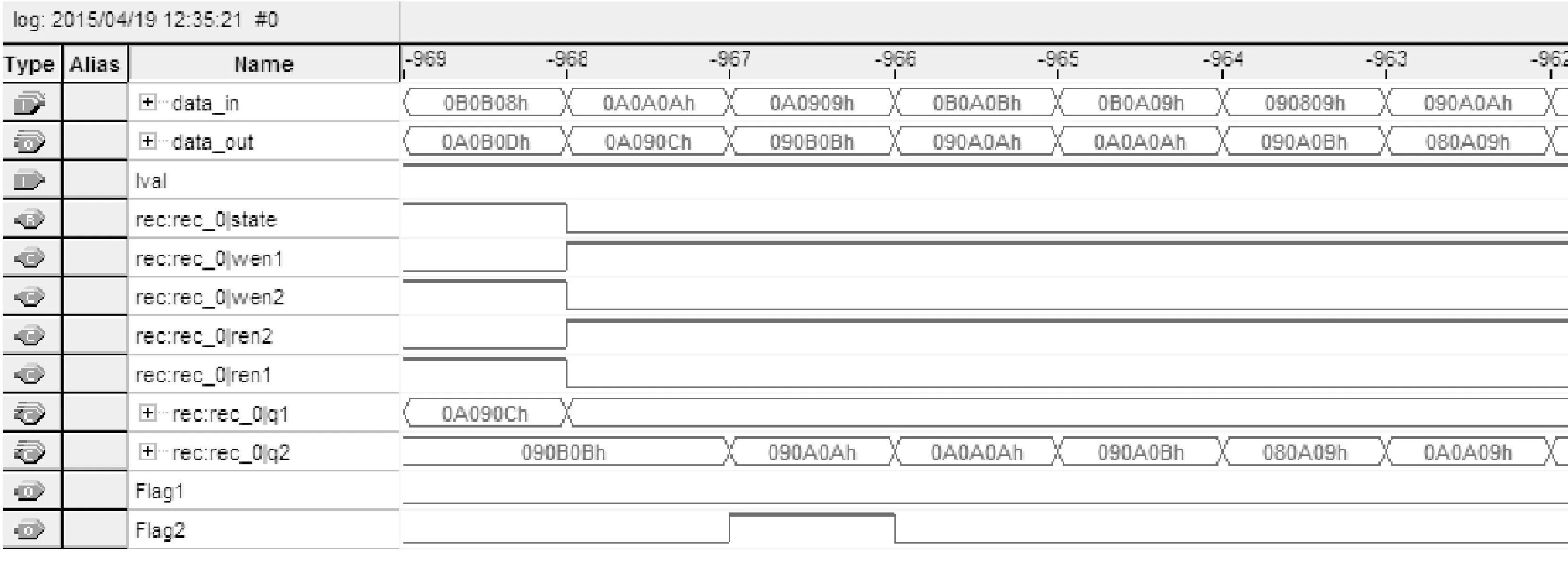

为了验证该图像数据采集与传输系统功能的实现,图像数据源来自KEY公司的L1000系列CCD线阵相机,设置其行频为3500 Hz,图像深度为24位。在FPGA内部例化两组FIFO,宽度为24,深度取较小为100,来模拟外部FIFO,以便查看FIFO的读写周期是否正确。同时利用Quartus中Signal Tap工具结合FPGA编程可以精确采集到FIFO输出数据(图6、图7)。测试结果表明:当LVAL有效时,两片FIFO交替存储和读取数据,相机输入FPGA数据与FIFO的读出数据完全一样。

图 6 采集数据周期图

图 7 采集数据周期细节图

5结束语

本文设计的基于数据采集与传输系统,相机数据采集模块、乒乓存储模块、相机控制模块在FPGA的控制下实现了Camera Link接口的CCD相机数据采集、缓存、与传输,后续采用DSP做复杂的色选算法。本设计可以替代基于计算机的高速实时图像数据传输与处理系统,实现了体积小、实时性高、处理数据量大的特点,该系统成功应用在CCD色选机分选系统中。

[参考文献]

[1]何中翔,杨世洪. 基于Camera Link的实时显示技术研究[J]. 现代显示,2008,93(8) :31-35.

[2]贾建禄,王建立. 基于Camera Link的高速图像采集处理器[J]. 液晶与显示, 2010,25(6) :914-918

[3]赵德伟,王永超. 基于多DSP与FPGA的视频处理平台硬件设计[J]. 电视技术,2013,38(7) :75-81.

[4]杨柯,范海震. Camera Link接口的高速电子存储系统设计[J].舰船电子工程,2012,215(5) :110-113.

[5]陈欣波. Altera FPGA 工程师成长手册[M].北京:清华大学出版社,2012.

[6]黄成茂. 基干Camera Link和USB2.0的图像采集技术研究[D].成都:电子科技大学, 2012,5.

[7]潘松,黄继业. EDA技术与VHDL[M].北京:清华大学出版社,2007.

[8]梁义涛,唐垚,史卫亚,等. 基于Cyclone IV的Camera Link-HDMI高清视频转换器设计[J]. 电子技术,2013(5):12-14.

[9]National Semiconductor Corporation.DS90CR287/DS90CR288A datasheet[Z].National Semiconductor Corporation,2004.

[10] Texas Instruments Corporation.SN74V215/SN74V225/SN74V235/SN74 V245 datasheet[Z].Texas Instruments Corporation,2006.

[责任编校: 张众]

Design of Image Collection and Processing System Based on CameraLink

ZHOU Jingdong, CHENG Chai, ZHOU Minggang, HUANG Yunpeng , LI Minhui

(ResearchandDesignInstituteofAgriculturalMechanicalEngin.,HubeiUniv.ofTech.,Wuhan430068,China)

Abstract:In the field of color recognition, aiming at characteristics that mass data of image should be transferred and processed out from high-frame camera, this article designed a high frequency linear CCD data image acquisition and processing system using FPGA as a process chip based on Camera Link. High performance DSP complete the complex algorithm calculation. The design idea, hardware architecture,and functionality of the system were introduced including Camera Link interface technology, cache memory, FIFO interface technology, and image output control, et al. The system finally achieved stable data transmission, storage and processing after the system had been debugged.

Keywords:image acquisition; image process; FPGA; FIFO; Camera Link

[中图分类号]TP274

[文献标识码]:A

[文章编号]1003-4684(2016)01-0004-04

[通讯作者]程钗(1987-),男,湖北黄石人,湖北工业大学硕士研究生,研究方向为机电一体化技术

[作者简介]周敬东(1973-), 男,湖北黄石人,工学博士,湖北工业大学副教授,研究方向为机电一体化技术

[基金项目]国家自然科学基金(51174084)

[收稿日期]2015-09-14