基于分立元件的DDS重构滤波器的性能分析

2016-03-29耿籍穆仕博

耿籍 穆仕博

(中国空空导弹研究院,河南洛阳 471000)

基于分立元件的DDS重构滤波器的性能分析

耿籍 穆仕博

(中国空空导弹研究院,河南洛阳 471000)

DDS的DAC所输出的频谱中包含有很多镜像频率,该镜像频率是造成DDS输出频率周期性抖动的主要因素,若要消除这种抖动获得纯净的输出频率,就必须充分了解重构滤波器的滤波特性和最优的构建方法。本文主要介绍了如何基于分立元件搭建性能最优的LC低通滤波器,并对不同的滤波器构建方式进行了特性分析和对比。

DDS;模数转换;滤波;抖动;镜像频率

基于分立元件搭建DDS输出重构低通滤波器是DDS输出信号滤波的通用方法,搭建重构滤波器主要目的在于滤除DAC输出的镜频分量,从而消除输出频率的抖动,获得纯净的输出频率,然而重构滤波器的构建方式、器件选型以及器件布局和布线均影响着滤波器对镜频分量的抑制效果。在国家知识产权局专利检索网站,目前可以检索到有关以“分立元件、滤波器”为关键词的共计103件发明和实用新型专利,比如“一种超低损耗同轴线电感微带高通滤波器”、“一种宽带低损耗声表面波可开关滤波器组”等专利。本文结合实例,从以上方面分析了滤波器的性能差异和不同因素所带来的影响,并给出了具体的指导建议。

1 DDS输出频谱的镜频分布特性

使用DDS产生时钟信号,DAC镜像频率衰减不足会严重影响系统的周期性抖动性能,在输出频谱的幅度遵循响应曲线的情况下,镜像频率理论上可扩展至无限频率。图1所示为DDS的DAC输出的理论频谱。图2所示为具体实例的输出频谱[1]。

图1 DAC输出理论频谱

图2 DAC输出频谱实例

从图1和图2中可以看出,镜像频率占有较大能量,必须通过重构滤波器的阻带抑制特性予以消除,这就需要我们根据实际情况设计出具备优良阻带抑制特性的低通滤波器。

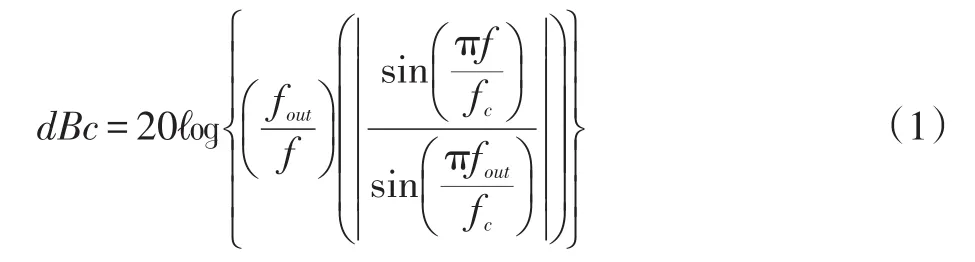

通过以下公式,可计算任何特定镜像频率相对于fout的相对幅度(dBc),其中f是镜像频率,fc是DAC的采样数率:

评估滤波器的阻带性能时,应以远超出其通带范围的频率进行测量,以确保镜像频率能得到充分抑制。建议应在频率达到数千兆赫或至少达到5fc时观察阻带抑制。

2 重构滤波器的特性分析

在实际应用中,当镜像频率远远超出通带时,滤波器的阻带抑制性就会下降,这是由于非理想器件和印刷电路板上器件的物理布局引起的。

2.1 非理想器件选择特性分析[2]

实际用于滤波的电容和电感并不完全具有容性或感性,分立元件的实际电路模型均存在一个由L和C组合构成的自谐振器件和一个由R引起的插入损耗器件(如图3所示)。从器件选择的角度来看,要实现最优的通带和阻带性能,首先要选择具有较高自谐振频率和较高Q特性的器件,具有较高Q额定值的器件的优点是其串联R值较低。在低通滤波器中,这种特性可以减少串联电阻的插入损耗并降低旁路电容的阻抗。各器件的自谐振频率由元件值及其物理结构决定,选择尺寸较小的封装通常是较佳的选择,较小的封装一般具有更高的自谐振频率并减少与PCB布局相关的寄生效应,对于旁路电容,可选用元件值仅为原始元件值一半的两个并联电容将自谐振推至更高的频率。该技术的影响笔者将在后续试验结果对比小节加以印证。选择插入损耗较小的器件可在滤波器输出端提供更大的信号幅度,幅度的降低会直接影响输出信号的压摆率,而提高接收器的输入压摆率可降低宽带噪声。

2.2 元器件物理布局特性分析[3]

由于器件的布线焊盘之间存在寄生电容,寄生电容会无意间将信号从输入耦合至输出,所以滤波器的器件布局会显著影响镜像频率的阻带抑制,要实现最优的阻带抑制,需要同时对器件选择和布局细节加以关注。以下列出可使重构滤波器获得最佳性能的实用布局技巧。

(1)在器件下面使用实心(不间断)接地层来降低电路的环路电感,从而降低返回电流路径的阻抗。

(2)将滤波器每阶的旁路电容用两个小电容来实现,来提高电容的自谐振频率并降低感性接地。此外,对旁路器件结合使用底部接地层和顶部接地层,这样做可以进一步降低感性接地。使用多个过孔将两个接地层连在一起。

(3)避免滤波器元件之间靠得太近,器件布局紧密时,走线寄生和互耦会影响滤波器的频率响应。

(4)保持走线的阻抗与滤波器的特性阻抗相匹配。虽然这一点对器件互连并非至关重要,但对于连至滤波器外部电路的走线(比如输入和输出连接)而言却很重要。

2.3 不同电路结构特性分析

图3 理想模型与实际模型对比

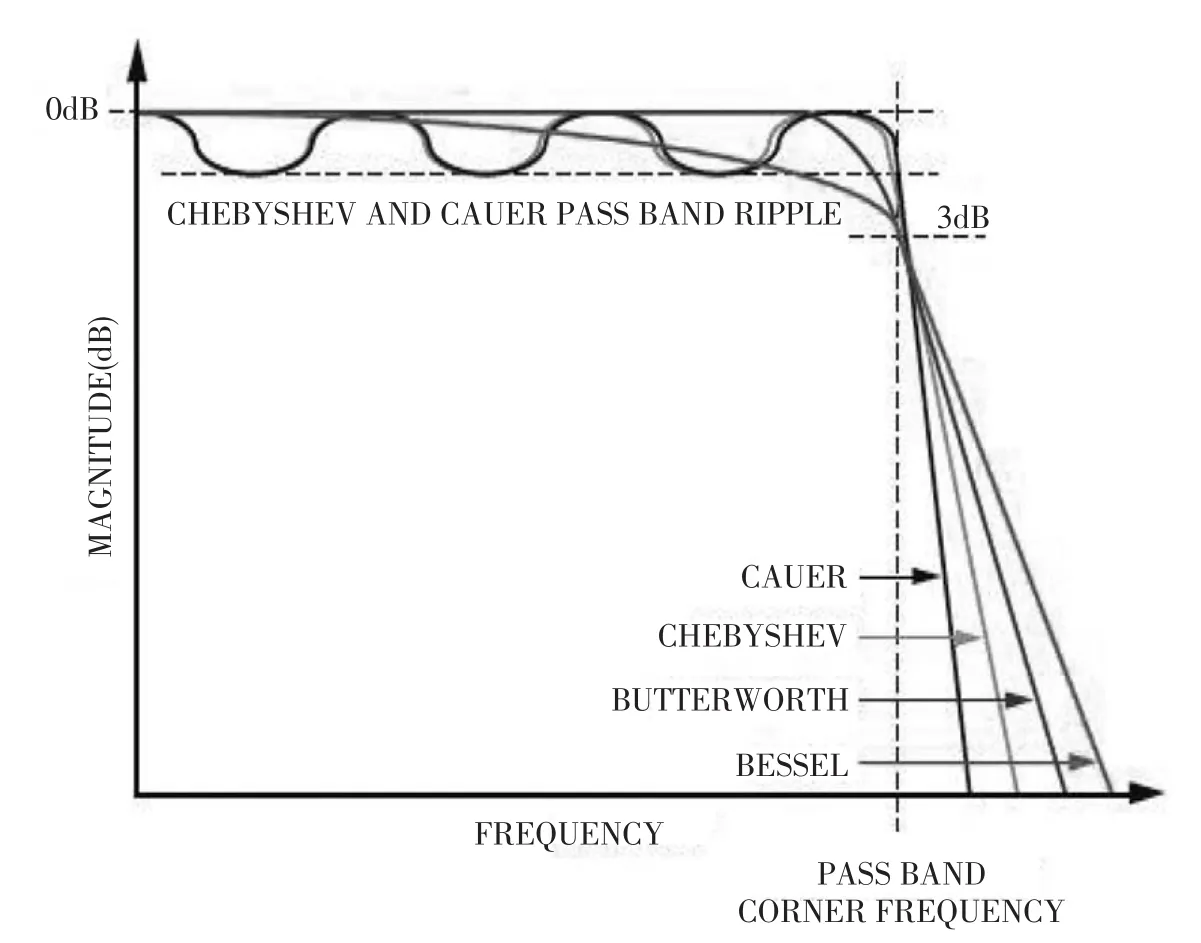

分立LC低通滤波器的实施成本较低,并且具有较强的灵活性。因此我们通常使用椭圆响应滤波器(又称考尔响应滤波器)作为LC低通重构滤波器。与其他响应类型相比较,在给定滤波器阶数的情况下,椭圆滤波器可提供最快的通带至阻带转换时间,此特性使椭圆滤波器成为重构滤波器的理想电路构建方案。

图4所示为考尔、切比雪夫、巴特沃兹和贝塞尔这四种基本滤波器的一组具有代表性的响应曲线。

如图所示,椭圆响应能提供陡峭滚降,但代价是通带和阻带中会出现纹波(图中纹波为示意绘制不代表真实的纹波摆幅),但该纹波参数可以通过具体的滤波器设计进行控制[4]。

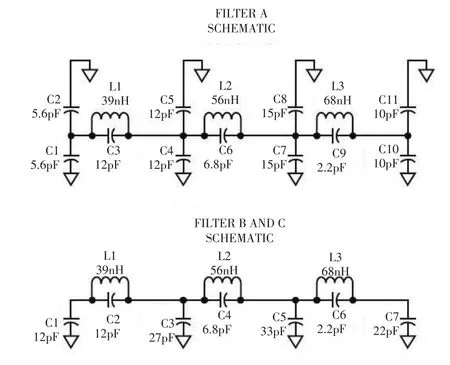

LC滤波器根据驱动电路是电流源还是电压源而分为两种形式。如果由电流源驱动,则第一元件为并联连接,而对于电压源,第一元件为串联连接。DDS的输出通常为电流驱动,我们选择并联连接为第一元件。图5为本案所要对比的三种滤波器(A、B、C)电路模型(七阶、椭圆、低通LC),B和C滤波器的原理图相同但实际的布局布线不同,相比较B和C,A滤波器每阶的旁路电容遵循了前述的元器件选用原则,即将原本的一个原值旁路电容替换为两个容值为原值一半的旁路电容,具体布局参见图6。

图4 四种基本滤波器的响应曲线

图5 滤波器A、B、C的电路结构对比

3 不同电路结构及布局的对比

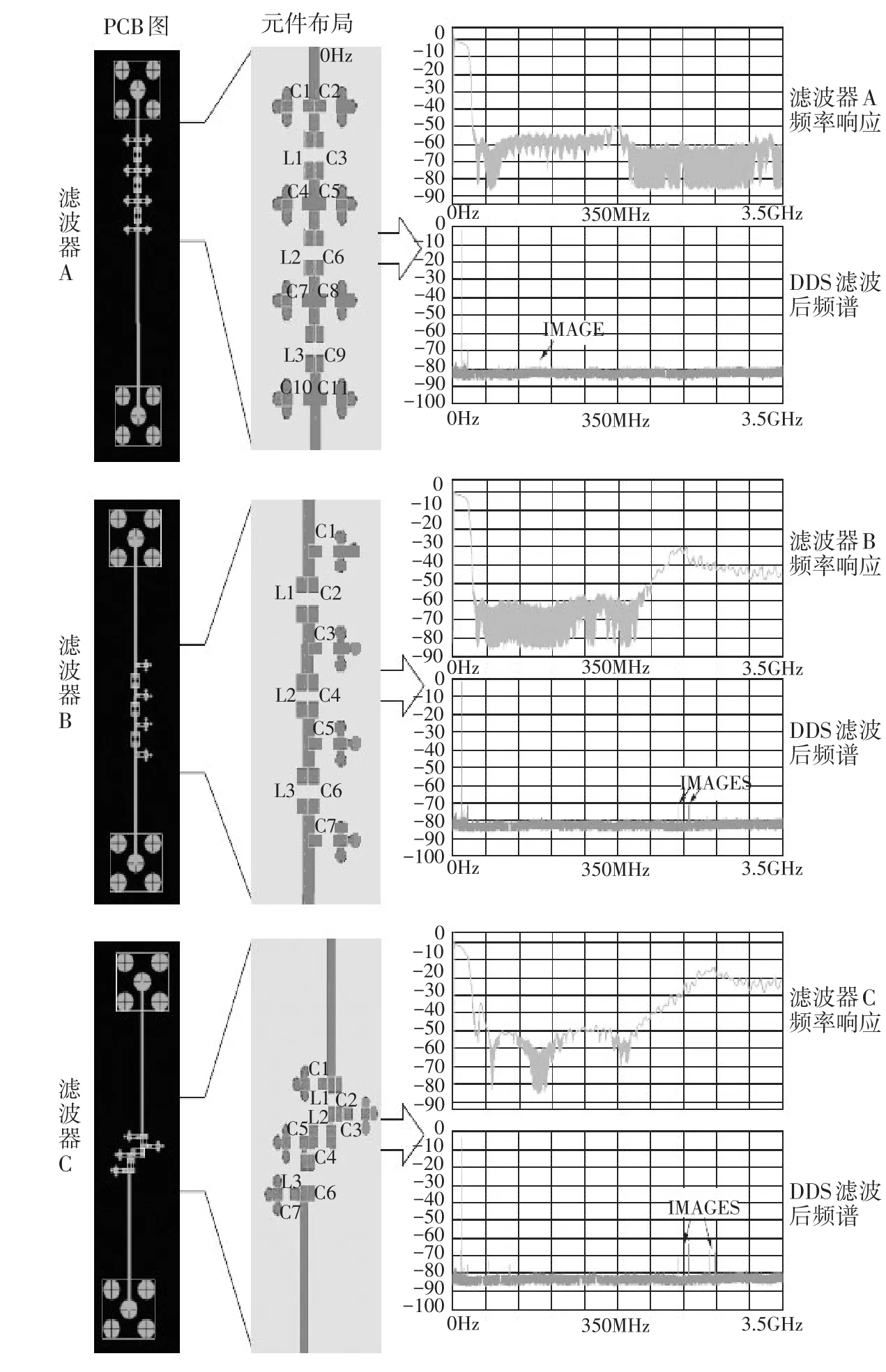

图6所示为滤波器A、B、C三种滤波器的频率响应曲线和实际的滤波效果,这三种LC低通椭圆滤波器的实现方案表明不同的PCB布局对镜像频率的抑制效果也不同。三种方案实现的都是使用分立LC器件的七阶、椭圆、160MHz低通滤波器(DDS输出频率设置为110.123MHz,DAC采样速率为500MSPS)。

在需要极低抖动的应用中,充分抑制DAC镜像频率非常关键。实际上,非谐波频谱杂散的幅度与所产生的周期性抖动之间存在直接关系,公式如下:

式中,dBc是相对于基波幅度的杂散幅度,UI为一个相关时钟信号周期,抖动的量级以UI为单位进行表示,公式2的曲线图如图7所示。例如,如果一个时钟信号具有-35dBc的非谐波杂散,则由图可知该杂散能够引起约0.006UI的周期性的峰值间抖动。

使用此曲线图时,切记抖动值仅适用于单杂散分量,存在多个杂散时,公式2所示的arctan函数自变量中必须对每个杂散的贡献求和。此外,该曲线图不涉及随机抖动问题,其效应必须单独考虑[5]。

例如,与N个杂散相关的峰峰值抖动公式如下:

4 结论

DDS的DAC输出所产生的频谱在采样频率倍频附近排列着多个基波(镜像频率),这些镜像频率的幅度是周期性抖动的主要来源,滤波器输出端和接收器输入带宽内的任何杂散都会降低DDS做为时钟输出的性能,降低幅度与杂散幅度成正比。因此,设计DAC重构滤波器之前,应该对重构滤波器特性和性能有充分的了解,以确保其满足具体的应用要求。

图6 滤波器A、B、C的滤波效果对比

图7 时序抖动与杂散干扰的关系

[1]徐振英.数模转换器应用技术[M].北京:科学出版社,2000.

[2]袁光德,李文林.电子技术及应用基础[M].北京:国防工业出版社,2007.

[3]胡圣尧,关静著.模拟电路应用设计[M].北京:科学出版社,2009.

[4]森荣二.LC滤波器设计与制作[M].北京:科学出版社,2006.

[5]华南盾,戴鳌前.模拟电路测量与实验[M].上海:上海交通大学出版社,1985.

The Performance Analysis of DDS Restructuring Filter Based on the Discrete Component

Geng JiMu Shibo

(The Air-to-Air Missile Academy of China,Luoyang Henan 471009)

There are many image frequency in the output frequency spectrum of DDS's DAC,these image frequency is primary factor which cause output frequency Jitter,if we want to eliminate this,we must fully understand the charac⁃teristic and the best structure of the filter.This article introduce how to establish the best LC low pass filter,and giving the performanceanalysis and contrast for the different filter structure.

DDS;DAC;filter;Jitter;image frequency

TN713

A

1003-5168(2016)11-0069-04

2016-9-28

耿籍(1974-),男,硕士研究生,高级工程师,研究方向:雷达导引头嵌入式计算机设计。