飞管1394总线接口模块设计实现*

2016-03-18蔡叶芳张亚琦牛少平

蔡叶芳,张亚琦,牛少平,夏 杰

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068;3.西安翔腾微电子科技有限公司,陕西 西安 710068)

飞管1394总线接口模块设计实现*

蔡叶芳1,2,张亚琦3,牛少平1,2,夏 杰3

(1.中航工业西安航空计算技术研究所,陕西 西安 710068;2.集成电路与微系统设计航空科技重点实验室,陕西 西安 710068;3.西安翔腾微电子科技有限公司,陕西 西安 710068)

在面向新一代飞机管理系统的1394总线应用中,为满足节点标准化设计,提高电气特性信号质量,降低节点的维护成本,提出了一种基于1394总线协议的飞管1394总线接口模块。该模块具有功耗低、体积小、重量轻、可靠性高的特点,并且1394总线 3个端口分别通过 3根1394专用电缆以辫接方式引出,实现了接口的标准化和统一化。在充分理解1394总线协议的基础上,分别从硬件架构、逻辑设计和软件设计方面介绍了飞管1394总线接口模块的设计与实现,通过测试与验证,表明该接口模块功能与性能满足机载环境的应用需求。

1394总线;飞机管理系统;AS5643协议;接口模块

0 引言

随着航空电子系统综合化程度越来越高,1394总线系统中的设备复杂程度提高,为实现1394总线系统接口的标准化要求,设计一种飞管1394总线接口模块成为必然。模块采用统一设计,便于远程节点与总线网络的连接;为提高信号质量,采用辫接方式;并实现信息收/发和相关总线信息的监控功能。

飞管1394总线接口模块安装在飞机管理系统总线上远程节点的成品单元内,提供了远程节点与飞机管理系统总线通信的能力。该接口模块可提供满足飞机管理系统总线要求相关的物理层和链路层硬件需求,采用辫接方式实现1394总线接口与飞机管理系统的连接,完成飞机管理系统总线与LRU主机控制器之间的数据通信。

1 接口模块设计

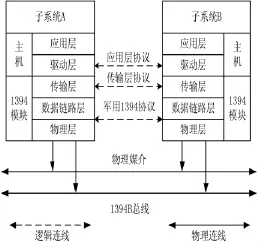

飞管1394总线接口模块设计遵循1394总线通信系统的五层协议,如图1所示。其中,物理层与数据链路层由接口模块的硬件实现;1394协议通过FPGA逻辑和驱动软件实现;应用软件和驱动软件驻留在上位机中,应用软件通过调用驱动软件实现主机对模块基本资源的访问、数据通信、模块状态控制、状态信息读取等功能[1]。

1.1 硬件架构

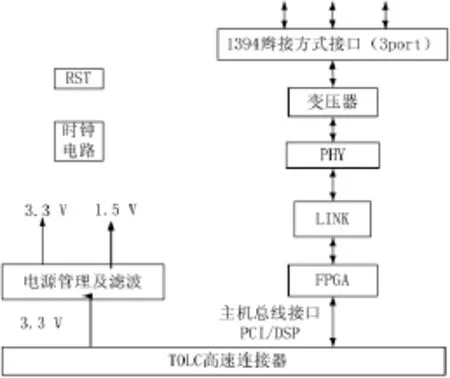

飞管1394总线接口模块实现1394总线接口、协议解析/处理及数据收发等功能,同时对外提供 PCI或异步总线接口,实现与主机之间的数据交互,其硬件功能框图如图2所示。

图1 1394总线通信系统

图2 接口模块功能框图

飞管1394总线接口模块由 FPGA芯片、链路层电路、物理层电路、1394接口电路、主机接口电路、复位电路、时钟电路、电源电路以及其他辅助电路等部分组成,各功能模块描述分别如下:

(1)FPGA电路:采用Actel公司大规模器件A3PE3000,主要实现接口控制、SAE AS5643协议处理和数据传输等功能[2];

(2)链路层:支持1394a协议,实现链路层配置、总线组包和解包功能;

(3)物理层:支持1394b协议,实现总线仲裁以及收发数据编解码功能;

(4)耦合变压器:变压器作为物理层芯片和总线传输介质之间的耦合器件,起到了对接收和发送终端的隔离保护作用,防止总线上的干扰或脉冲对核心器件的损害,增强了接口模块的可靠性和防护能力[3];

(5)测温电路:实现对模块的温度采集和监控,对模块进行健康管理;

(6)复位电路:实现模块的上电复位功能,确保上电后该模块的电路单元工作在稳定状态下,上电复位采用RC上电防抖动电路来实现,提供给FPGA和PHY芯片作为复位输入;

(7)时钟电路:为FPGA、链路层和物理层芯片提供工作时钟;

(8)电源电路:支持DC-DC转换,为接口模块提供工作电源。

飞管1394总线接口模块实现单节点RN功能,在接口模块硬件设计基础上,兼容 PCI和异步总线两种主机接口。其中 PCI接口采用标准的 PCI信号,主机通过接口模块上的 TOLC连接器访问硬件资源并进行数据交互,完成 FPGA与主机的通信;异步总线接口支持两种处理器:TMS320C6000系列和TMS320F281x系列,对应的外总线接口分别为EMIF接口和XINTF接口。

1.2 逻辑设计

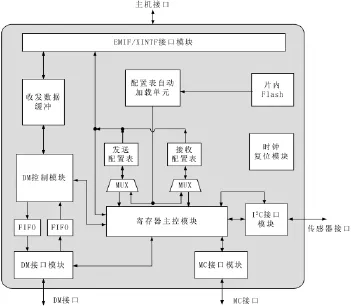

飞管1394总线接口模块的功能主要由FPGA实现,FPGA系统架构如图3所示。主要功能模块包括:主机接口单元、接收和发送数据存储区、接收和发送消息配置DPRAM、配置表加载单元、寄存器主控模块、DM控制模块、DM接口和MC接口模块、I2C接口模块。

图3 AS5643协议处理模块功能框图

其中寄存器主控模块主要实现寄存器的访问;配置表加载模块将内部 Flash中存储的特定格式配置表数据加载到寄存器和消息配置区中,并支持配置表头、配置表数据CRC校验及配置表加载重试功能。DM控制模块主要完成数据发送和接收功能;DM接口模块完成写发送数据、读接收数据、VPC校验(接收消息)、处理 CRC错误数据包等功能。MC接口模块主要完成对链路层芯片寄存器的读写访问、获取端口状态信息以及对链路层芯片进行初始化配置等功能;I2C接口模块完成对 I2C芯片寄存器的访问功能。

1.3 软件设计

飞管1394总线接口模块驱动软件作为应用软件和系统硬件资源的中间层,由主机应用软件调用,实现接口模块初始化、通信及获取节点状态等功能。

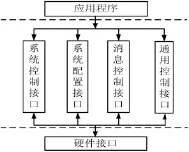

驱动软件包括 4个功能模块:系统控制接口、系统配置接口、消息控制接口、通用控制接口,具体驱动功能框图如图4所示。

图4 软件设计的体系结构关系图

系统控制接口主要实现初始化、 获取逻辑版本、获取配置表版本及软件版本功能,提供获取模块状态信息的软件接口。

系统配置接口主要实现获取总线接口模块芯片 ID、总线周期状态及BIT结果等功能,并提供对应功能软件接口。

消息控制接口主要实现收发异步流包、收发时间应答消息、接收 STOF包及获取消息计数的功能,提供应用软件数据通信接口。

通用控制接口主要包含 DPRAM访问接口、AS5643访问接口、1394链路层访问接口和配置区访问接口,实现驱动软件访问硬件资源的功能。

2 技术优势

与同类总线接口模块相比,飞管1394总线接口模块主要技术优势如下:

(1)创新性地将1394总线信号通过辫接电缆方式引出,降低了信号衰减,提高了信号传输质量;

(2)兼容 PCI和异步总线两种接口,满足不同成品多种主机接口的需求,解决产品统型问题;

(3)实现自适应多余度总线配置功能,提出了一种支持四余度总线配置表结构及加载方案,满足某机载产品多位置自适应的应用要求;

(4)1394总线信号采用变压器耦合方式引出,提供 3个Beta模式的端口,端口传输速率均可配置;

(5)创新性地提出S100B、S200B速率下的信号质量性能指标,完成1394接口物理层信号完整性分析、设计及验证,有效地提高了总线信号传输质量,保障了数据传输可靠性[4];

(6)与国外同类产品相比功耗较低(不大于 2 W)、体积更小、重量更轻(包含连接器和最大长度线缆在内约170 g)、可靠性高,应用范围更广,满足机载及地面环境应用需求。

3 测试及验证

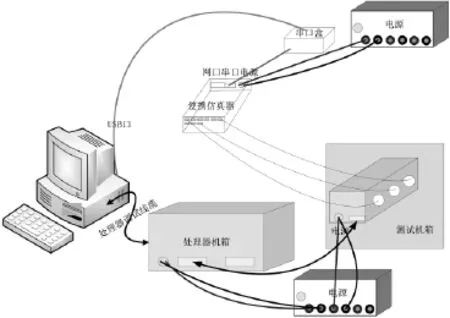

针对1394总线协议对接口模块的功能、性能及电气特性要求,根据AS5643协议体系中的相关测试协议,分别对该模块的产品功能、电气特性、环境适应性等进行了全面测试[5]。如图5构建验证平台对其功能、性能进行验证。测试机箱与处理器机箱相连作为RN节点,便携式仿真器作为CC节点。通过串口线将便携式仿真器与PC连接、测试机箱与便携式仿真器间用1394线缆连接,实现CC节点与RN节点之间的信息交互。

图5 飞管1394总线接口模块验证连接示意图

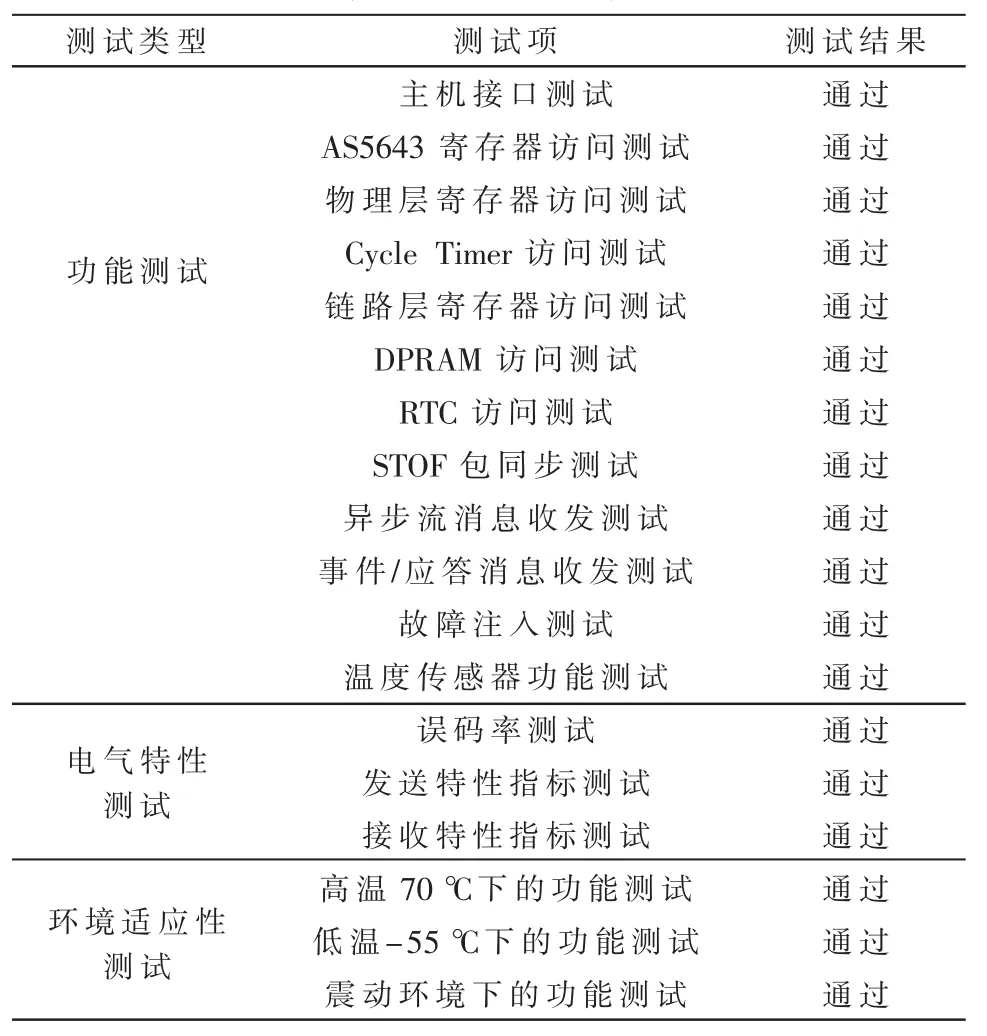

按照飞管系统要求,分别对接口模块的功能、电气特性及环境适应性进行详细测试,测试项及测试结果如表1所示,所有测试项均测试通过,满足飞管系统对接口模块的测试要求[6]。

表1 测试列表

4 结论

通过对飞管1394总线的接口模块功能、性能,试验,系统联试,试飞验证等进行测试,结果表明,飞管1394总线接口模块实时性强,确定性强,性能稳定、可靠,并通过国军标软件工程化测试,满足机载安全关键子系统高速、可靠、接口统一的要求,为航天、船舶等领域1394总线产品开发提供设计参考和实践经验。

[1]赵彬,田泽,杨峰,等.基于 AS5643协议的接口模块设计与实现[J].计算机技术与发展,2013,23(8):100-102.

[2]SAE AS5643/2 IEEE-1394b interface requirements forandaerospace vehicle applications[S].2006.

[3]SAEAS5643/1 S400 copper mediainterface characteristics over extended distances[S].2004.

[4]Sai Haowei.Analysis of a SAE AS5643 Mil-1394b based high-speed avionics network architecture for space and defense applications[C].Proc.of IEEE Aerospace Conference. [s.l.]:[s.n.],2007.

[5]SAE AS5706 test plan/procedure for AS5643/1 S400 copper media interface characteristics over extended distances[S]. 2007.

[6]SAE AS5657 test plan/procedure for AS5643 IEEE-1394b interface requirements forand aerospace vehicle applications[S].2007.

Design and implementation of aerocraft management1394 bus interface module

Cai Yefang1,2,Zhang Yaqi3,Niu Shaoping1,2,Xia Jie3

(1.AVIC Computing Technique Research Institute,Xi′an 710068,China;2.Aviation Key Laboratory of Science and Technology on Integrated Circuit and Micro-System Design,Xi′an 710068,China;3.Xi′an Xiangteng Microelectronics Technology CO.,LTD,Xi′an 710068,China)

In the1394 bus application for a new generation of aerocraft management system,in order to satisfy the standard node design,improve the electrical characteristics signal quality,and reduce the node′s maintenance costs,this paper puts forward a aerocraft management1394 bus interface module based on1394 bus protocol.The module has characteristics of low power,small volume,light weight and high reliability,and1394 bus three ports are fetched respectively by three1394 special cable with plait format,to achieve the standardization and unification of interface.In the full understanding of1394 bus protocol,the article introduces the aerocraft management1394 bus interface module design and implementation from the hardware architecture,logic design and software design repectively.The test and verification show that the interface module function and performance meet the demands of the application of avionic.

1394 bus protocol;aircraft management system;AS5643 protocol;interface module

TP393

:ADOI:10.16157/j.issn.0258-7998.2016.06.003

蔡叶芳,张亚琦,牛少平,等.飞管1394总线接口模块设计实现[J].电子技术应用,2016,42(6):10-12,20.

英文引用格式:Cai Yefang,Zhang Yaqi,Niu Shaoping,et al.Design and implementation of aerocraft management1394 bus interface module[J].Application of Electronic Technique,2016,42(6):10-12,20.

2016-03-09)

蔡叶芳(1982-),男,高级工程师,主要研究方向:大规模集成电路、SoC设计。

张亚琦(1987-),男,助理工程师,主要研究方向:嵌入式软件设计与开发。

牛少平(1979-),男,硕士,高级工程师,主要研究方向:SoC设计与验证、图形图像处理器设计。

夏杰(1985-),男,硕士,工程师,主要研究方向:嵌入式硬件设计与开发。

航空科学基金(2015ZC51036);中国航空工业集团公司创新基金(2010BD63111)