数字电路教学中EDA工具的应用

2016-03-12本溪市机电工程学校

本溪市机电工程学校 栾 迪

数字电路教学中EDA工具的应用

本溪市机电工程学校 栾 迪

本文介绍将 QuartusII 软件应用到数字逻辑电路的教学中,利用QuartusII设计工具通过具体实例阐述了EDA技术在数字电子技术实验中的应用,体现了EDA技术相对于传统数字电路教学优越性,激发学生学习数字电路的兴趣,有良好的教学效果。

数字电路;QuartusII

1.引言

在传统的数字电子系统设计中,手工设计占有较大的比例。手工设计一般先按电子系统的具体功能要求进行功能划分,然后对每个子模块画出真值表,用卡诺图进行手工逻辑简化,写出布尔表达式,画出相应的逻辑线路图,再据此选择元器件,设计电路板,最后进行实测与调试。手工设计方法缺点是:(1)复杂电路的设计、调试十分困难。(2)由于无法进行硬件系统仿真,如果某一过程存在错误,查找和修改十分不便。(3)设计过程中产生大量文档,不易管理。(4)只有在设计出样机或生产出芯片后才能进行实测。

传统的数字电路的理论教学大多采用黑板板书和 PPT 的形式进行, 在这种单向的教学模式中,学生只能依靠教师的讲解,被动的接受知识,而不能形象、直观的看到电路内部实际的信号流动、处理过程以及电路的作用,因此,理解电路内部工作原理比较困难,教学效果不佳。传统数字电路实验部分的教学还要受到实验仪器和设备,元器件种类和数量的限制,有电接触不稳定、实验功能单一等缺点。

进入21世纪,随着电子技术的飞速发展, EDA技术也得到了长足的发展,同时也冲击和改变着传统数字电子技术实验教学的方法和模式, EDA已经成为数字电子技术系统设计的重要手段。EDA不但在整个设计流程上充分利用计算机的自动设计能力、在各个设计层次上利用计算机完成不同内容的仿真模拟,而且在系统板设计结束后仍可利用计算机对硬件系统进行完整的测试。随着计算机硬件技术和软件技术发展起来的软件技术,如 EWB、Multisim、Proteus、QuartusⅡ等EDA技术为数字电路课程的教学提供了新的思路和方法,利用QuartusⅡ软件可以不受上述条件的限制,方便学生对集成电路功能的理解、电路的仿真和设计。

2.QuartusII特点

QuartusⅡ是 Altera 公司的综合性 PLD 开发软件,支持原理图、VHDL、VerilogHDL 以及 AHDL(Altera Hardware Description Language)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整 PLD 设计流程[1]。

(1)QuartusII软件的元器件库提供了数千种电子元器件,包括:基本元件库、宏功能元件库、工作库、参数可设置兆功能库等。丰富的元器件为学生了解各类数字电路元器件打下了坚实的基础,也可了解各类元器件的参数和性能。

(2) QuartusII软件可提供电路仿真和测试功能,还可进行时序分析。能使仿真分析易于理解,仿真结果一目了然。

(3)QuartusII软件可设计、测试和演示时序逻辑电路等各种电路,还可对被仿真电路设置各种故障,从而可以在教学中模拟各种故障,提高学生对实际电路分析和排故的能力[2]。

3.四选一数据分配器的设计

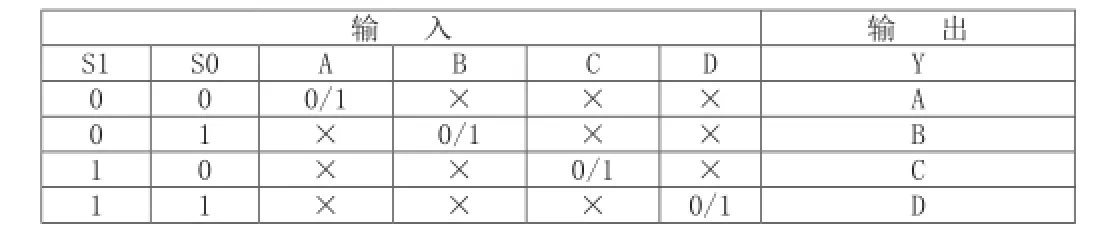

表1 4选1数据分配器的功能

数据分配器是将一路输入数据根据地址选择码分配给多路数据输出中的某一路输出[3]。它的作用相当于多个输出的单刀多掷开关。数据分配器的用途比较多,比如用它将一台PC机与多台外部设备连接,将计算机的数据分送到外部设备中,组成脉冲分配器,用它 与数据选择器连接组成分时数据传送系统。

3.1 Verilog HDL 语言描述

硬件描述语言(HDL)是EDA技术的重要组成部分,目前常用的HDL主要有VHDL、VerilogHDL、System Verilog和System C。其中,VHDL和Verilog HDL在目前的EDA设计中使用得最多,也得到几乎所有主流EDA工具的支持。Verilog 的部分语法是参照C语言的语法设立的。采用 Verilog HDL 语言的输入方式进行设计,4选1数据分配器的程序如下[4]:

module MUX41a(A,B,C,D,S1,S0,Y);

input A,B,C,D,S1,S0;

output Y;

reg Y;

always @ (A or B or C or D or S1 or S0)

begin

case ({S1,S0})

2'b00 : Y<=A;

2'b01 : Y<=B;

2'b10 : Y<=C;

2'b11 : Y<=D;

default: Y=A;

endcase

end

endmodule

3.2 波形仿真

在QuartusII平台,对上面的程序进行编辑、编译、综合、适配、仿真之后,可得到图1所示的仿真波形。

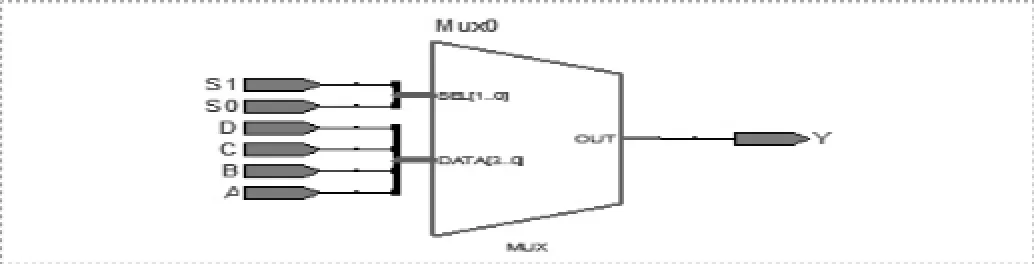

3.3 RTL电路

通过QuartusII软件还可以观察该四选一数据分配器的RTL电路图,了解线路连接和数据传输情况。

图2 四选一数据分配器RTL电路图

4.结论

用Verilog HDL对数字系统进行抽象的行为与功能描述以及具体的内部线路结构描述,从而可以在电子设计的各个阶段、各个层次进行计算机模拟验证,保证设计过程的正确性,大大降低设计成本,缩短设计周期。

利用 QuartusⅡ软件对数字电路进行设计仿真,突破传统数字电路教学的局限性,有利于学生对 Verilog HDL 硬件描述语言和数字逻辑电路的理解,将 QuartusⅡ应用到数字电路的教学中来, 可以将数字电路中理论的 0、1 关系更直观的展现到学生面前,激发学生学习的兴趣,提高学生学习的积极性,有很好的教学效果,起到事半功倍的作用。

[1]赵艳华,曹丙霞,张睿.基于 QuartusII 的 FPGA/CPLD 设计与应用[M].北京:电子工业出版社,2009.

[2]江国强.EDA技术与应用[M].北京:电子工业出版社,2004.

[3]蒋立平.数字逻辑电路与系统设计[M].北京:电子工业出版社,2008.

[4]潘松,黄继业,陈龙.EDA技术与Verilog HDL[M].北京:清华大学出版社,2010.