基于UVM实现高效可重用的SoC功能验证

2016-03-09重庆邮电大学通信与信息工程学院潘应进

重庆邮电大学通信与信息工程学院 潘应进 龙 恳

基于UVM实现高效可重用的SoC功能验证

重庆邮电大学通信与信息工程学院 潘应进 龙 恳

【摘要】通用验证方法学(UVM)融合了OVM和VMM两大验证方法学,使验证语言统一于SystemVerilog,验证方法学统一于UVM。在研究了UVM的基础上,重点研究了如何使用UVM搭建高效可重用的SoC验证平台。先进行模块级功能验证,再将模块级验证组件重用到系统级验证平台中,实现APB子系统的功能验证。通过组件的重用,缩短了系统验证平台的搭建时间,进一步缩短了SoC验证的周期。在结果分析上,通过代码覆盖率和功能覆盖率的结合,保证验证的进度和质量。通过与传统验证平台的对比,结果表明,UVM验证平台在验证效率上远远高于传统验证平台。

【关键词】通用验证方法学;SoC;功能验证;验证平台

0 引言

随着SoC芯片集成度和复杂度的不断提升,SoC基带芯片研发的验证工作量成倍增加[1]。然而,市场是无法接受芯片的研制周期成倍增加的,因此,需要针对占据SoC基带芯片设计大量时间的验证工作进行分析,研究更为高效的基带芯片验证方法,缩短芯片的研制周期以满足市场需求。

UVM验证方法学是一套具有强大功能的验证方法学,它吸取了包括AVM、OVM以及VMM在内的众多验证方法学的精华,代表着验证技术的最新进展[2]。使用 UVM 验证方法学搭建验证平台能极大地提高验证的完备性和效率,满足芯片设计的时间和性能要求。

本文深入研究了UVM,并基于UVM的基础架构,使用SystemVerilog验证语言[3]搭建了一套系统级验证平台,对一款基带处理芯片中的APB[4]子系统进行功能验证,并与传统验证方法进行对比,阐述UVM验证方法学在实现高效可重用的SoC功能验证时的独特优势。

1 UVM验证方法学

面对SoC验证难度的持续提升,传统的验证方法越来越难以满足验证的需求,大家开始探寻抽象层次更高的验证语言和性能更完善的验证方法[5]。UVM是基于SystemVerilog语言开发的一个库[6],而SystemVerilog最重要的一个特性就是引入了类的概念,这使得它具有了面向对象编程的特点,UVM也就由一个个这样的类组合而成。UVM库中包括三种类型的类[7]:uvm_components、uvm_objects和uvm_transactions。一个实际的验证平台就由扩展自uvm_components的基本组件类构成,包括uvm_driver、uvm_seqencer、uvm_monitor、uvm_agent、uvm_scoreboard、uvm_env、uvm_test等。

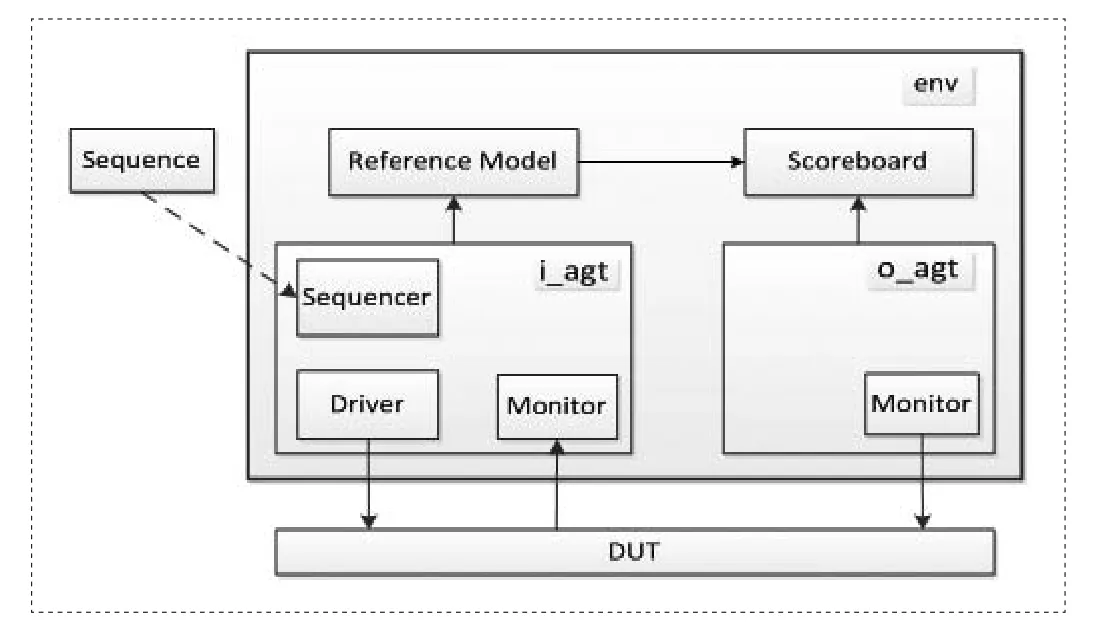

图1给出了一个典型的UVM验证平台的基本架构。在这个验证平台中,有两个agent,i_agt配置为active模式,负责驱动和监控总线;o_agt配置为passive模式,只负责监控总线,没有驱动功能。sequence产生随机的激励transaction并送给sequencer,sequencer有一个仲裁机制判断并决定何时将该transaction传给driver,driver在得到transaction后就将其驱动到DUT接口上,同时,monitor从DUT接口收集输入数据并传给参考模型用以产生期望值。在另一侧,monitor收集DUT的输出并发给计分板scoreboard,计分板完成数据的自动化比对。

图1 典型UVM验证平台架构

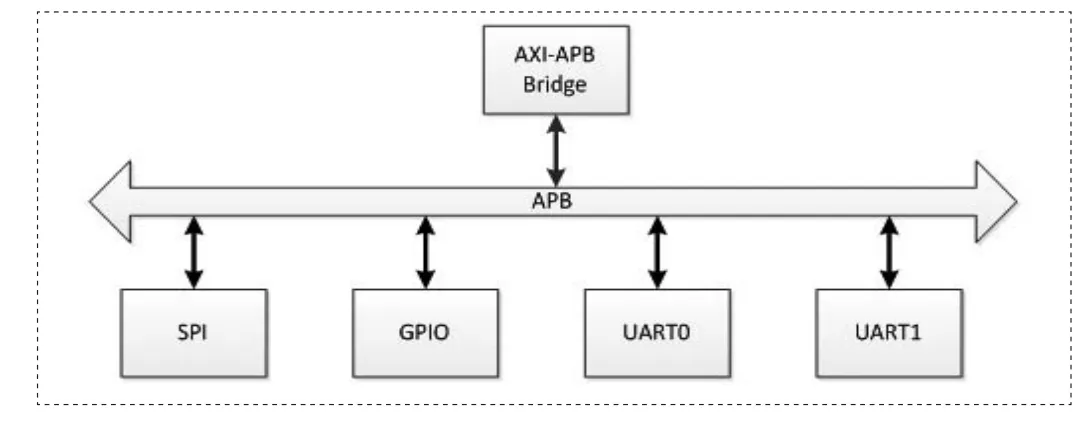

2 DUT介绍

本次验证的对象是一款通用基带处理芯片中的APB子系统,包含APB总线及其上挂载的SPI、GPIO和两个UART模块,以及一些时钟和复位模块。图2所示为本次验证对象的框图。在该子系统中,AXI-APB转换桥接收来自AXI总线的输入,并将其转化成APB格式的数据送给APB,APB根据不同的地址将数据发送到不同的模块,这些模块按照协议对输入数据进行处理,对APB进行回应或者将处理结果输出。

图2 APB子系统框图

3 基于UVM的验证平台设计

3.1 UVM模块级验证平台

本次验证从模块级验证出发,再将各个模块验证组件重用到子系统,完成子系统的验证。

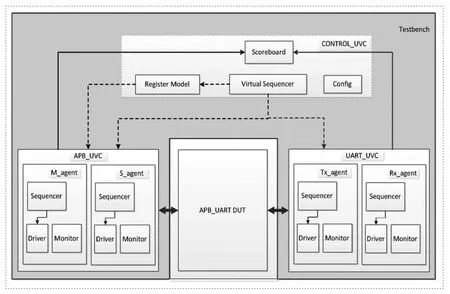

图3是基于UVM的UART模块级验证环境,分为三个部分:APB_UVC、UART_UVC和CONTROL_UVC。APB_UVC实现APB总线的功能,配置并控制UART,可对UART进行数据的读写操作;UART_UVC充当与UART通信的设备,可以接收来自UART的数据,也可以往UART发送数据;CONTROL_UVC对APB_UVC和UART_UVC进行管理,提供激励的入口,配置验证环境,完成数据的自动化检查,覆盖率收集,以及提供寄存器模型。

SPI和GPIO模块的验证平台与该平台类似,只需替换相应部分即可,这本身也是UVM模块级重用的一个体现。

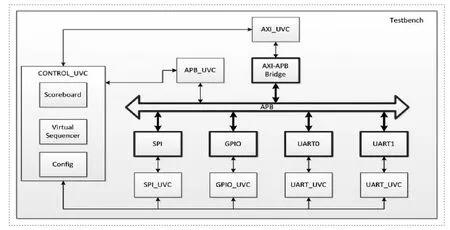

3.2 UVM子系统验证平台

完成模块级的验证后,就可以将所有模块集成到子系统验证环境中。针对本次验证的系统,模块级验证完成后将产生一些可重用的验证组件APB_UVC、UART_UVC、SPI_UVC、GPIO_UVC。再根据UVM结构和AXI总线协议[8]设计一个AXI_UVC,即可完成目标子系统验证环境的搭建,如图4所示。

图3 UART模块及验证平台

图4 APB子系统验证平台

这个平台重用了模块级验证平台中的APB总线验证模型和各模块的验证模型,将控制功能移到模块外围,在系统级进行验证流程的控制。CONTROL_UVC实现的功能大致与模块级相同,但复杂度却要大得多,如计分板部分,模块级只需实现自己模块的数据对比,而系统级的计分板针对的是整个系统,不同模块数据来源、格式都可能会不一样,所以在这个计分板模型中需要包含各个模块的计分板小模型。有的模块如UART不需要参考模型,而有的模块需要参考模型,在计分板中都要区别对待。

4 验证结果分析

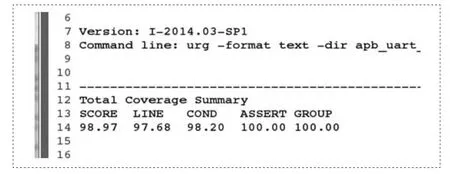

根据系统功能需求编写测试用例对验证平台进行测试,待所有测试用例全部运行完成且没有错误信息后,查看覆盖率信息,确定验证的进度和性能。由于该子系统中各模块没有太多的交集,所以在验证的各个环节上都是独立的,包括覆盖率的收集、结果的分析。图5为UART模块的覆盖率信息,其中行覆盖率达到了97.68%,功能覆盖率达到了100%,表明所有功能都已覆盖到了,而且代码覆盖也达到了要求,说明对UART的验证已完成。SPI和GPIO的功能覆盖率也均达到了100%,代码覆盖率也都在96%以上,符合验证的要求。

图5 验证覆盖率信息

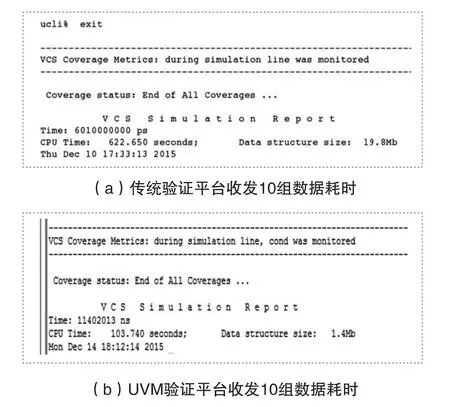

与传统验证平台相比,UVM验证平台在激励的产生,结果的自动化检查以及运行的耗时上都要更加优越。图6是UVM平台与传统验证平台运行单个测试用例的时间对比,可以看出,UVM平台的耗时不足传统平台的1/6。由此可见,当所有测试用例都测试完成,UVM验证平台在效率上将远远优于传统验证平台。

图6 UVM验证平台与传统验证平台验证效率对比

5 结束语

本文深入研究了UVM验证方法学的各种机制,利用SystemVerilog验证语言的特性基于UVM的架构搭建了一套系统级验证平台,对APB子系统进行了功能验证。通过对UVM中各种类的继承,建立了一个高度可重用的APB总线验证模型和UART、SPI、GPIO验证组件,并通过子系统集成证明了其可重用性。通过代码覆盖率和功能覆盖率的收集,保证了验证的质量。实验结果证明了UVM验证平台的高效性。这个平台真正实现了高效可重用的功能验证,为搭建旨在缩短SoC验证周期的系统级验证平台提供了参考的范例。

参考文献

[1]吕毓达.基于UVM的可重用SoC功能验证环境[J].半导体技术,2015,40(3):234-238.

[2]李俊.基于UVM的视频图像2D转3D模块的验证[D].中国海洋大学,2013.

[3]Janick Bergeron. Writing Testbenches using SystemVerilog[M]. Berlin:Synopsys.Inc,Springer,2008.

[4]Synopsys Discovery Verification IP for APB UVM User Manual Version1.98a.2013,71-80.

[5]段然.SoC系统验证方法研究[J].航天控制,2009, 27(3):80-85.

[6]Accellera. Universal Verification Methodology (UVM) 1.1 User’s Guide[M].2011.

[7]Mentor Graphics UVM Documentation Verification Methodology online Cookboook,2013:3-7.

[8]侯秋菊,沈海华.IP可重用的AMBA AXI总线验证平台设计与实现[J].计算机工程与设计,2008,29(7): 1713-1715.