基于SOPC的U盘加解密系统实现

2016-02-27沈珊瑚

吴 军,沈珊瑚,何 忠

(杭州师范大学杭州国际服务工程学院,浙江杭州 311121)

基于SOPC的U盘加解密系统实现

吴军,沈珊瑚,何忠

(杭州师范大学杭州国际服务工程学院,浙江杭州 311121)

摘要:U盘是一种能够进行数据交互的主流便携式存储设备,设计对U盘数据进行加密和解密的系统能够带来更为安全的移动存储.本文利用SOPC(System On a Programmable Chip )技术设计实现了一种U盘加解密系统,AES算法实现利用Verilog HDL语言,硬件部分采用Altera公司的Cyclone IV EP4CE15F17C8 FPGA芯片,与PC机的交互利用Nios II软核完成.由于加解密处理器和控制器都以IP软核的形式嵌入到FPGA中,整个系统具有高度的可配置性和兼容性.实验验证了该系统的加解密功能的正确性.

关键词:SOPC; U盘加解密; FPGA; Nios II

随着人们对信息安全的重视,数据加解密系统显得越来越重要,特别是当信息存储在某种便携式设备(如U盘)上时,由于缺少独立的数据保护系统,在进行数据交互时容易发生信息泄露的现象,如果能为这些便携式设备加上一个加解密系统,就能有效的保护信息安全.目前兴起的互联网云计算移动存储就迫切需要这类硬件加密方式.

一个好的加解密系统在于有一个几乎不能够被攻破的加密算法,AES(Advanced Encryption Standard)算法就是当今被业界所承认的比较安全的算法之一,是由美国国家标准和技术学会于2002正式公布的高级加密标准[1],由于此算法设计简单、安全性良好和可以抵抗目前所有的已知攻击,现已广泛应用于语音、视频信息加密,数据库中数据加密以及硬盘数据加密等方面[1-4].SOPC(System On Programmable System)是可编程片上系统,近几年低成本的FPGA不断推陈出新,利用EDA工具对FPGA芯片进行多样性设计,并逐步向系统级设计发展是一大趋势[5-6].

文中所实现的这种能够对U盘中数据进行加密和解密的系统,在使用时将计算机和U盘一同与加密器相连接,输入正确密钥后,即可进行数据的加解密和存储等操作.加密装置包括数据解压缩模块,存储设备控制模块,加解密模块,密钥管理模块,电源,时钟电路,以及负责与主机通信并带有USB接口的设备,与存储端通信并带有USB插槽的设备等.其中加解密模块采用多密码引擎的并行方式进行加解密.由于提供了基于AES算法对U盘中数据进行加解密的实现方法,具有很高的安全性、兼容性和高速存储性等特点[7-8].

1系统硬件结构

本系统实现的硬件包括黑金开发板四代,ALTERA Cyclone IV EP4CE15F17C8芯片,主要应用到的软件有:Quartus II、NIOS II IDE和Modelsim10.1等,其中Quartus II用来实现Verilog 硬件主要模块,如:AES加解密,密钥保存,串并转换等;NIOS II IDE主要用来控制U盘文件操作和串口通信,Modelsim10.1主要用来对Verilog模块进行行为仿真.

图1系统连接关系图

Fig. 1Diagram of system connection relationship

如图1所示,将开发板分别与PC和外部存储设备相连,其中PC与FPGA之间通过串口相互进行信息交互,PC负责发送命令至FPGA板,然后FPGA板对接受的命令进行判断和执行;U盘与FPGA开发板直接相连,在进行加解密的过程中可以对U盘里面的文件进行相应的操作.

系统硬件框架分析:

图2 系统框架Fig. 2 System Frame

U盘数据加解密系统框架如图2所示,它包括USB公口端、USB母口端、数据解压缩模块、存储设备控制模块、加解密模块、密钥管理模块、电源及时钟的产生电路.

图2中USB公口端含有USB公口及USB数据传输协议,与数据解压缩模块相连接;USB母口端含有USB母口及USB数据传输协议,与存储设备控制模块相连接;加解密模块含有加密算法,并采用多加解密引擎的方式对送入的数据分组进行加解密操作,与存储设备控制模块相连接;密钥管理模块与存储设备控制模块相连接,对密钥进行安全管理;电源及时钟的产生电路分别与所述的存储设备控制模块和加解密模块相连接,用于产生加解密模块所需要的电压和时钟.

2系统软件分析

2.1 SOPC系统的构建

本文以Altera公司的EP4CE15F17C8芯片为基础,构建了一个能对U盘中数据进行加解密处理的SOPC系统.整个SOPC系统如图3所示.

AES-128加密算法系统每次将128bit(bit:位)的明文块和128bit的密钥经过10轮迭代最终产生128bit的密文块输出,解密过程则相反[7];AES加密IP核是用SOPC Builder构建的,根据AES算法内部设计的理论,处理时延时2ns,但为了安全稳定起见,同时也考虑到FPGA板能够跑在100M,故时钟设为100MHZ,完成128bit的加密需要13个时钟周期,按照以上时钟计算,满负荷运行加密时的速度可以达到985M bit/s(123M byte/s)[8],从而可以实现高速稳定的加解密运算.放大图A中,“AES”是AES加密模块,负责数据的加密;“port8to128”是串并转换模块,负责串并转换;“keybox”是密钥管理验证模块,用于验证密钥的正确性;放大图B中,aes_inv_cipher_top为AES解密模块,负责数据的解密;port8to128为串并转换模块,负责串并转换.

图3 SOPC 系统, 解密模块(左下图),加密模块(右下图)Fig. 3 SOPC system, decryption module (bottom left), encryption module (bottom right)

2.2 AES时序分析

2.2.1AES加密核接口时序图

如图4所示,一次128bit字节的加密可以在12个时钟周期内完成(10个周期用于轮循环,1个时钟周期用于初始化密钥扩展,1个时钟周期用于输出阶段).AES加密模块内部一旦接受到ld管脚信号为高,会在text_in和key总线上分别采样128bit明文和密钥.通过加密密核的运算,在12个时钟周期后,AES加密核会将done管脚信号拉高,告诉外部加密完成,用户可以根据该信号的完成情况来读出text_out数据线上的密文数据使用.

图4 AES 加密核接口时序Fig. 4 Time sequence of AES encryption core interface

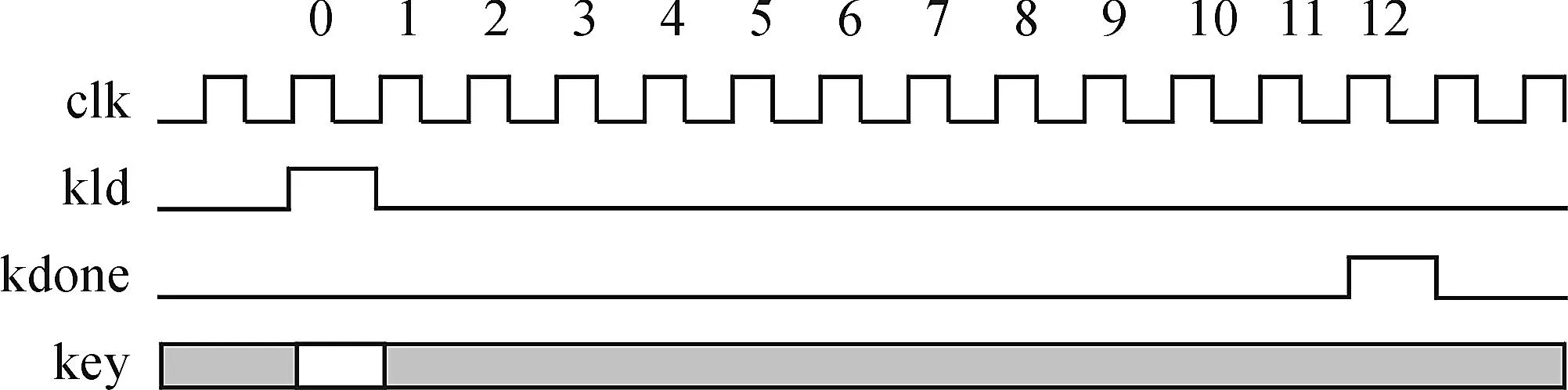

图5 密钥装入时序Fig. 5 Time sequence of key input

2.2.2密钥装入时序图

如图5所示,由于解密过程需要将子密钥扩展以后再反序,所以子密钥要在开始解密过程前已经反序完成,一旦密钥开始装入,密钥扩展就会产生并存取在内部缓存中.扩展的密钥可以被以后的解密反序列重复使用.其中key在kld信号拉高时装入,一旦密钥扩展完成以后,kdone信号就会在下一个时钟拉高.kdone拉高意味着可以进行解密操作了(由于密钥装入和加密序列不能并行发生,所以一个密钥装入总是在解密序列被执行前执行).

2.2.3解密序列图

图6 解密时序Fig. 6 Time sequence of decryption

如图6所示,一次128bit字节的解密可以在12个时钟周期内完成(10个周期用于轮循环,1个时钟周期用于初始化密钥扩展,1个时钟周期用于输出阶段).AES加密模块内部一旦接受到ld管脚信号为高,会在text_in和总线上分别采样加密后的数据.通过解密密核的运算,在12个时钟周期后,AES解密核会将done管脚信号拉高,标志着外部解密完成.

2.3 Modelsim仿真时序验证

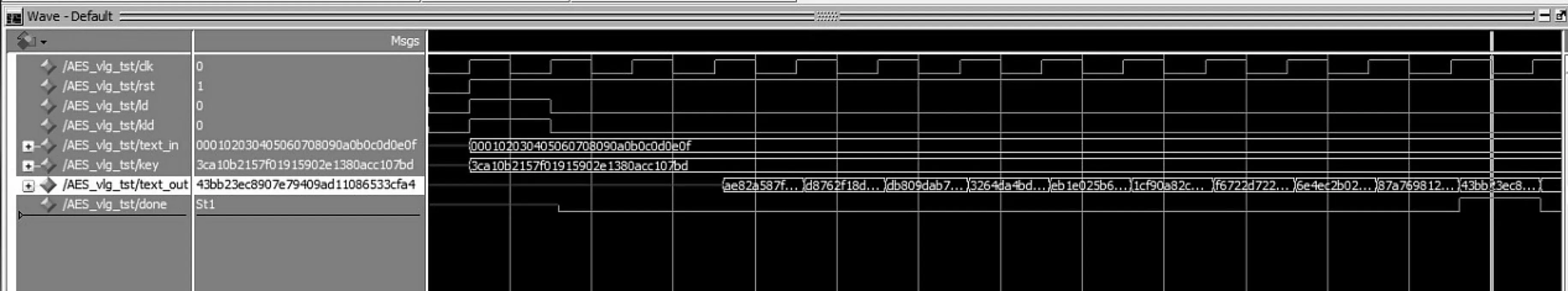

2.3.1加密验证

如图7所示,加密过程在12个周期内完成了,其中数据在10个周期内共加密了10次,直至第10轮为最终加密所得的结果,通过图7可以看到加密的结果为text_out=43bb23ec8907e79409ad11086533cfa4;在rst为1前,所有的输出都为高阻态,当rst=1时才会开始加密过程,ld为数据加载信号,当ld=1时开始加载数据,可以看到text_in在其等于1时加载了数据:text_in=128′h000102030405060708090A0B0C0D0E0F;kld为密钥载入信号,当其为1时开始载入密钥,可以看到载入的密钥key=128’h3ca10b2157f01915902e 1380acc107bd,密钥载入信号一般都是与数据加载信号同步,从而利于一有数据载入就能开始加密;done为加密完成信号,当done=1时,表明加密过程完成,可以进行解密过程.

图7 加密仿真结果Fig. 7 Encryption simulation result

2.3.2解密验证

如图8所示,令数据输入text_in=128’h43bb23ec8907e79409ad11086533cfa4,等待14个周期后,ld=1,开始载入数据,解密过程耗时12个周期,在后10个周期内将进行10次变换,并在第10次输出最终结果text_out=128’h 000102030405060708090a0b0c0d0e0f,由图8可以看出,数据经过加密和解密过程后其值保持不变,从而验证了加解密的正确性.

图8 解密仿真结果Fig. 8 Decryption simulation result

3实验结果

3.1 实现环境

整个实验在NIOS II IDE中进行,其中用的工具还有串口调试助手和AES加密解密计算工具;串口调试助手用于输入命令进行与主机和FPGA之间的信息交互,AES加密解密计算工具用于验证实验结果的正确性.

3.2 结果分析

程序共有4个主要命令:

1) 设置密钥,命令:k(密钥如果不正确没有操作权限);2) 遍历文件,命令:m;3) 读取文件,命令:r;4) 加密演示.命令:e.

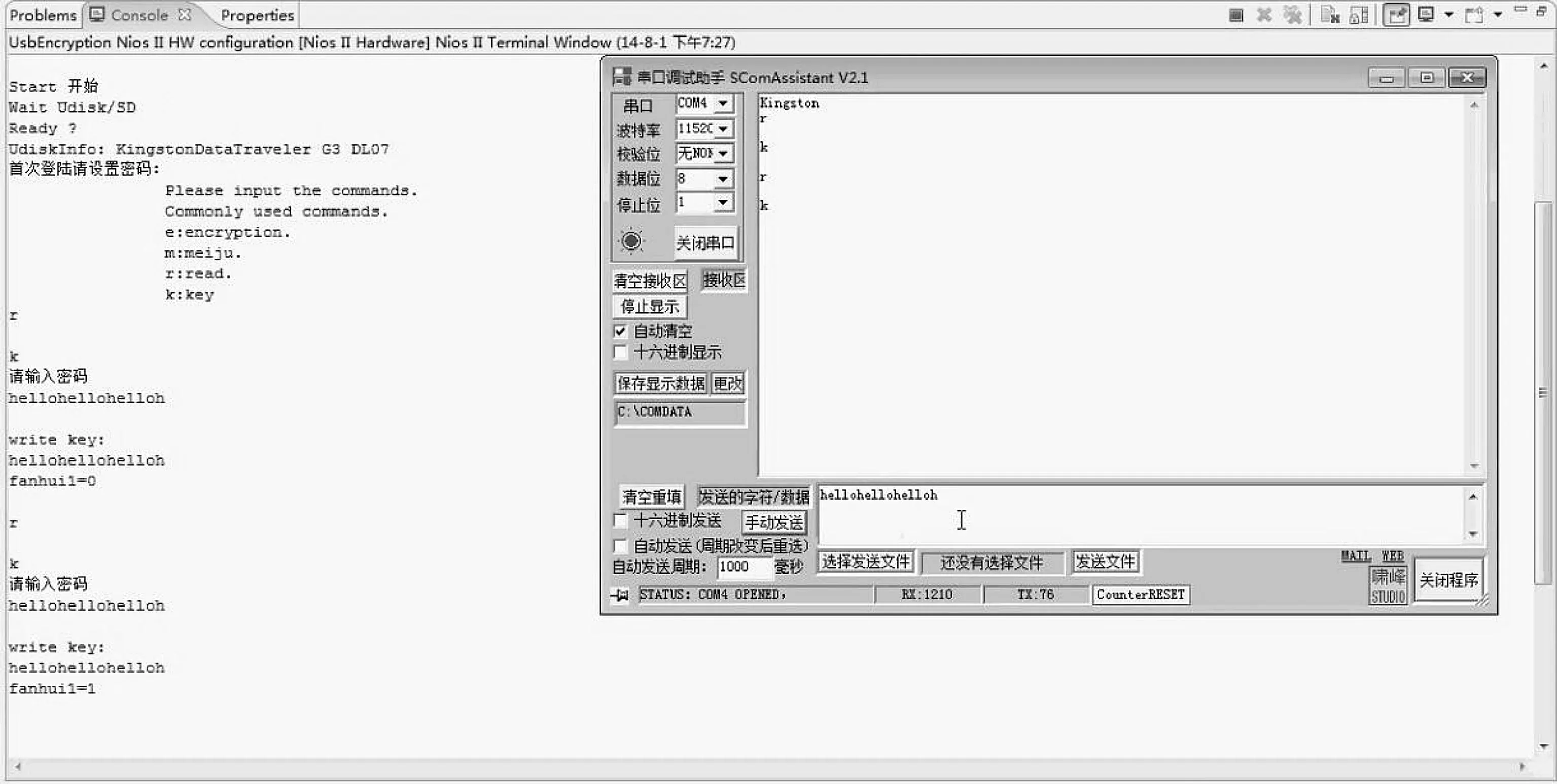

3.2.1密钥的设置与验证

图9显示,利用串口调试助手输入命令k后,在NIOS II IDE软件的console窗口可以看出输入了两次k命令,在验证标识fanhui1没有等于1前是没有权限进行其他命令操作的,这点可以从图9输入命令的情况看出.

图9 密钥设置与验证Fig. 9 Key setting and verification

3.2.2文件的读取

图10显示,在窗口调试助手里输入命令r后,就会提示输入要读取文件的文件名,读取的是TEST这个文本文档里的内容:You cannot improve your past, but you can improve your future.其中SrcFileSz表示文本文档里面内容的大小,单位为字节.

图10 文件读取Fig. 10 File reading

图11 枚举文件Fig. 11 File listing

图12 加密文件Fig. 12 Encryption files

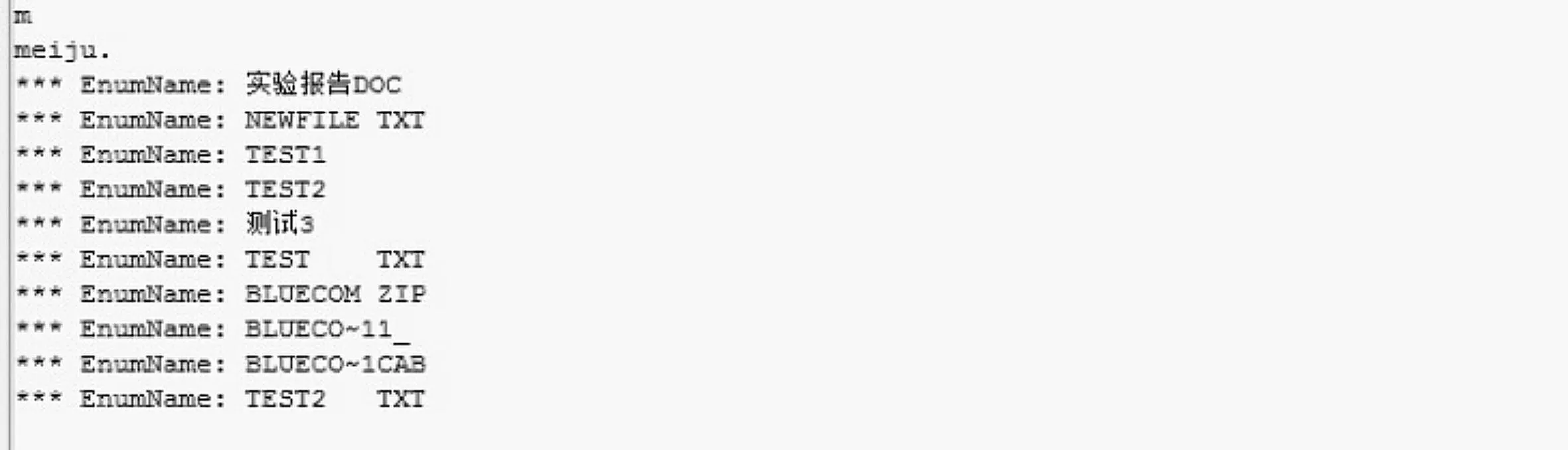

3.2.3枚举文件列表

图11显示,在串口调试助手里输入m命令后,就会列举出当前U盘里所有的文件的文件名,文件夹显示名称,文件显示名称加文件后缀名.

图13 软件验证结果Fig. 13 Software verification result

3.2.4加密文件

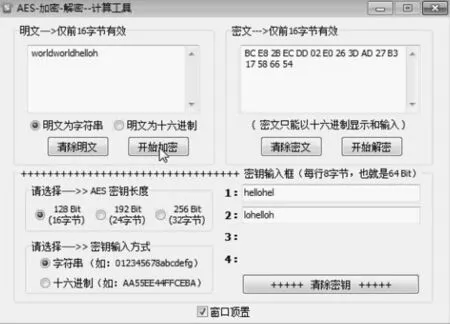

图12显示,在串口调试助手里输入命令e后,就会提示请输入要加密的文件名,以TEST文本文档为例,对其里面的文件进行加密处理,结果以十六进制显示(方便验证),从图12可以看出,密钥为:hellohellohelloh,明文为:worldworldhelloh,密文为:bce82becdd02e0263dad27b317586654.

3.2.5验证结果

用AES加密解密计算工具对上面的结果进行验证,如图13显示,可以发现在点击开始加密后,出来的密文与上面的结果是一致的,从而说明结果是正确的.至此,完成了对U盘里数据进行加解密的功能验证.

4总结

本文基于AES算法,利用SOPC技术设计出具有对U盘数据加解密功能的加解密系统,提供了一种对U盘数据加解密的加密器和加解密方法,当用户使用时,只要与加密器中已存的密钥一致就可以开始使用该加密系统进行加密,进而实现对U盘中的数据进行加解密操作,具有很高的安全性、兼容性、普遍性、通用性,高速存储、节省外部存储空间等优点.未来将改进现有系统密钥需要手动输入的弱点,并基于此系统对密钥管理进一步研究,即利用FPGA芯片本身时延等特性进行硬件固有安全的研究.

参考文献:

[1] 肖国镇,白恩键,刘晓娟.AES密码分析的若干新进展[J].电子学报,2003,31(10):1550-1554.

[2] 刘凌波,代江滨.现代密码理论新动向[J].计算机时代,2004(2):1-2.

[3] MENEZES A J, VAN OORSCHOT P C,VANSTONE S A.应用密码学手册[M].胡磊,王鹏,译.北京:电子工业出版社,2005:201-245.

[4] 付华杰,刘丽君,张遂南.高速USBIP核的设计与开发[J].微电子学与计算机,2008,25(7):127-129.

[5] 戴迎珺.基于SOPC的USB设备控制器IP核设计[J].计算机工程与设计,2008(20):5234-5236.

[6] 刘连东,郁滨,罗长远. 基于NIOS II的嵌入式USB主机设计与研究[J].计算机工程与设计,2007,28(9):2100-2102.

[7] EIBIRT A J, YIP W, CHETWYND B, et al. An FPGA-based performance evaluation of the AES block cipher candidate algorithm finalists[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems,2001,9(4):545-557.

[8] CALTAGIRONE C, ANANTHA K. High throughput, parallelized 128-bit AES encryption in a resource-limited FPGA[C]//Proceedings of the fifteenth annual ACM symposium on Parallel algorithms and architectures.[S.l.]:ACM,2003:240-241.

[9] SAGGESE G P, MAZZEO A, MAZZOCCA N, et al. An FPGA-based performance analysis of the unrolling, tiling, and pipelining of the AES algorithm[C]//Field Programmable Logic and Application. Berlin: Springer-Verlag,2003:292-302.

Implementation of USB Disk Encryption and Decryption System Based on SOPC

WU Jun, SHEN Shanhu, HE Zhong

(Hangzhou Institute of Service Engineering, Hangzhou Normal University, Hangzhou 311121, China)

Abstract:USB disk is a mainstream portable storage device that can carry out data interactions, and it brings safer mobile storage with the design of encryption and decryption system for the USB disk. This paper implementes a USB disk encryption and decryption system with SOPC (System on a Programmable Chip) technology, AES algorithm is implemented with Verilog HDL language, the core part adopts Altera Cyclone IV EP4CE15F17C8 FPGA chip, and the interaction with PC engine uses Nios II soft core. Since the encryption and decryption processor and controller are embedded in the FPGA chip in the form of IP soft core, the whole system is highly reconfigurable and compatible. Experimentations verify the functional correctness of the whole system.

Key words:SOPC; USB disk encryption and decryption; FPGA; Nios II

文章编号:1674-232X(2016)01-0095-07

中图分类号:TP368

文献标志码:A

doi:10.3969/j.issn.1674-232X.2016.01.018

通信作者:沈珊瑚(1981—)女,讲师,博士,主要从事安全芯片实现相关研究.E-mail:shshen88@163.com

基金项目:杭州师范大学科研启动基金项目(PF14002004005); 浙江省信息安全联盟课题(kz13013003).

收稿日期:2015-04-02