H.264/AVC解码芯片体系结构与验证

2016-02-24曹朋朋许宏杰陈威宇

曹朋朋,田 泽,许宏杰,赵 强,陈威宇

(中国航空计算技术研究所 集成电路与微系统设计航空科技重点实验室,陕西 西安 710068)

H.264/AVC解码芯片体系结构与验证

曹朋朋,田 泽,许宏杰,赵 强,陈威宇

(中国航空计算技术研究所 集成电路与微系统设计航空科技重点实验室,陕西 西安 710068)

H.264是一种高性能的视频编解码技术,在编解码效率和性能大幅提高的同时,增强了错误恢复及网络自适应等功能,具有广泛的应用前景,体系结构的合理设计与验证对H.264/AVC芯片至关重要。文中基于对H.264/AVC解码芯片体系结构的研究,构建FPGA验证平台,并对编程结构、软件框架及验证的实施进行了深入探索。首先确定了芯片的体系结构,为H.264/AVC解码芯片的设计验证提供了有力支撑,并通过搭建FPGA的测试,在FPGA对所设计的芯片功能和性能进行验证。验证结果表明,基于该体系结构的芯片功能正确,可满足实时解码需求,体系结构的设计与验证为整个芯片的设计提供了重要保障。

H.264;解码;FPGA;验证

0 引 言

H.264/AVC是一种高性能的视频编解码技术[1-2],其最大的优势是具有很高的数据压缩比率。如图1所示,H.264/AVC标准可分为三类[3-4]:

(1)基本类。简单版本,应用面广。

(2)主类。采用了多项提高图像质量和增加压缩比的技术措施,可用于SDTV、HDTV和DVD等。

(3)扩展类。可用于各种网络的视频流传输。

实现H.264编解码主要可以分为硬件实现和软件实现。文中利用H.264/AVC视频解码核构造H.264/AVC视频解码验证平台,H.264/AVC解码核是基于H.264/AVC标准,实现H.264/AVC解码的。根据软硬件的功能划分,对软硬件的交互机制与软件框架做了细致划分,由视频解码核硬件完成对264码流的解码,由解码核软件(FW)实现对解码芯片的控制,实现软硬件协同功能共同解码功能[5]。此外,该系统中还集成了音频解码模块,可实现对音频AAC码流的解码功能[6]。

1 H.264解码芯片体系结构

1.1 视频解码核功能介绍

H.264视频解码过程中,分为四个主要步骤,分别是NAL解码、逆变换、动态补偿、去方块滤波。这四步也是资源消耗的主要部分[7]。如果四个步骤全采用处理器纯软件解码运算,处理器的负载会非常巨大,视频解码模块将通过硬件解码的方式,实现上述解码过程中耗时最多的四个步骤。

一个完整的视频解码器如图2所示,由码流输入接口、视频输出接口(显示)、外部存储器接口(包括程序存储器接口和图像数据存储器接口)组成。视频解码模块由视频解码核、视频输出控制模块(简称VOC模块)和存储器接口三部分组成[8-9]。前端与存储器控制器连接,读取存储器中的视频数据。该模块具有PCI通路和Video通路。PCI通路与PCI主机连接,将从存储器读出的视频数据进行缓存,然后由PCI主机读出;Video通路与显示模块相连,将从存储器读出的视频数据进行缓存、采样格式转换和颜色空间转换,然后按照相应视频格式标准组帧输出到显示模块。

图2 视频解码核体系结构

1.2 视频解码体系结构

视频解码系统由视频解码核和视频解码核Firmware组成,解码核Firmware软件符合H.264/AVC标准,为SoC架构中的芯片控制部分软件程序,完成对解码引擎的控制。Firmware对解码核状态的控制和跳转应符合H.264/AVC标准中相关章节的解码控制的要求。

该系统从码流输入模块输入的原始码流输入格式为符合ISO13818-1标准的TS流,并可扩展支持其他封装的格式[10]。根据应用需求,由处理器接收来自码流输入模块、以太网、IDE三个模块输入的码流。程序运行中需在EMC模块外部挂接的同步SRAM中维护码流环形缓冲区。当码流输入中断产生时,从TS流输入模块(分码流输入模块、以太网、IDE三种输入方式)读取码流后,存储于码流缓冲区中;在中断服务程序外,查询ES缓冲区状态,若有剩余空间,则根据ISO13818-1完成对TS流的解析,分别将解析的视频ES、音频ES存入码流输入模块中对应的DPRAM中。由视频解码核BSDMA模块根据数据请求将输入的码流写入DDR2外存中[11]。

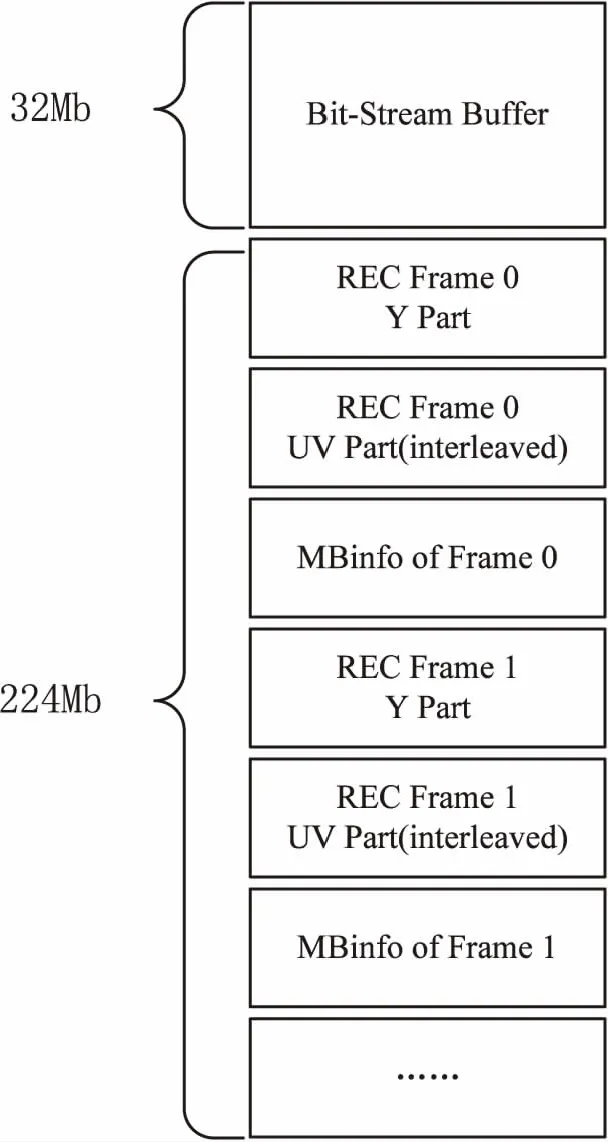

外存空间分配如图3所示。

图3 外存空间分配

H.264/AVC视频解码核中通过bs2rbsp模块输入码流,或BSDMA模式将码流读入进行解析。码流读入后经过一个8字节深度的FIFO进行缓存,然后将码流交给PES解析模块解析成ES流,如果码流本身就是ES流则无需经过PES解析模块,然后ES流进入SCD模块进行NAL头的解析,最后将NAL的字节数据交由解码引擎进行解码。在解码核解码检测到NAL起始码后,将产生Start_Code中断,处理器接收到中断程序后,根据NAL类型,解码NAL。

2 软硬件交互接口设计

在整个解码平台的设计中,涉及较多的软硬件交互机制。解码核使用bsdma从码流输入模块读入视频ES流,存入DDR中后,由解码核检测264码流的起始码,检测到起始码后,由解码核解码出NAL类型,产生Start_code进入软件中断处理程序,并在软件中断处理程序中,根据NAL类型,完成对相关NAL的解码。

序列的参数集(SPS)包括一个图像序列的所有信息,图像的参数集(PPS)包括一个图像所有片的信息。多个不同的序列和图像参数集经排序存放在解码器。编码器参考序列参数集设置图像参数集,依据每一个已编码片的片头的存储地址选择合适的图像参数集来使用。

图像参数集管理完成对图像参数集(PPS)进行管理,用于由每一个条带头中图像参数集决定的NAL单元的解码过程。图像参数集RBSP包括一些参数,这些参数可以被一个或多个编码图像的编码条带NAL单元或编码条带数据分割块A的NAL单元使用。

3 FPGA验证平台介绍

文中涉及的系统为基于Xillinx Virtex5 XC5VFX200T内部集成的PPC440硬核的EDK验证系统。该系统内部集成了视频解码模块和音频解码模块工作的必要元件以及功能模型(见图4),利用该FPGA测试平台可测试H.264/AVC解码芯片视频解码模块的功能。

图4 H.264/AVC解码FPGA验证平台

4 解码芯片FPGA验证

H.264/AVC协议中,Main Profile解码器支持对各种不同帧场模式、不同图像序列,以及不同熵编码方式的码流进行解码。为验证解码核解码功能的正确性,通过JM生成各种不同的码流,只要该码流符合H.264/AVC协议中Main Profile标准,视频解码核都应该能够正确进行解码。在验证过程中,对解码核的验证项分为基本验证项和扩展验证项。基本验证项的选取策略如表1所示[12-13]。此外,Main Profile标准还支持用不同宏块分割方式、帧场自适应方式、不同slice划分方式等不同的编码方式。在解码验证平台中,均可完成对以上不同编码方式生成码流的解码,并通过PCI主机输出解码后的YUV数据。与JM解码后生成的YUV文件进行比较,以判断解码核解码数据的正确性[14]。

5 结束语

文中结合H.264视频解码芯片的研制需求,结合周边资源,利用FPGA验证平台,完成了视频解码核的验证。在PPC440处理器时钟为405 M,解码核时钟为45 M情况下,完成了分辨率为1 024*768解码每秒25帧的速度[14-15],并通过数据比较,证明了解码后数据的正确性。为H.264视频解码芯片的研制开发提供了可靠的支撑,对具有同类需求的芯片的研制具有借鉴意义。

表1 H.264基本验证项码源格式

[1] 陈 佳,田 泽,黎小玉,等.H.264/AVC视频编码核基于FPGA验证的设计与实现[J].计算机技术与发展,2013,23(7):10-13.

[2] 毕厚杰.新一代视频压缩编码标准-H.264/AVC[M].人民邮电出版社,2005.

[3]H.264/MPEG-4Part10whitepaper[S].[s.l.]:[s.n.],2003.

[4]ITU-TH.241.ExtendedvideoproceduresandcontrolsignalsforH.300seriesterminals[R].[s.l.]:[s.n.],2003.

[5] 沈敏一,高新波.H.264视频编码系统中多参考帧的选择算法研究[J].电路与系统学报,2008,13(4):50-54.

[6] 王维哲,周 兵,张行进.H.264编码帧中的帧内预测模式选择算法[J].计算机工程,2008,34(2):226-228.

[7] 陈 芳.一种基于错切原理的图像旋转方法[J].淮阴师范学院学报:自然科学版,2004,3(4):319-322.

[8] 邱 航,陈雷霆.基于点的计算机图形学研究与进展[J].计算机科学,2009,36(6):10-15.

[9]BosiM,GoldbergR.Introductiontodigitalaudiocodingandstandards[M].Massachusetts:KluwerAcademicPublishers,2003.

[10] 武 丹,许如星.浅析《计算机图形学》中线裁剪算法的讲授方法[J].科技创新导报,2009(30):182-182.

[11] 郭 亮,李 玲,田 泽,等.ARINC659总线接口芯片的FPGA原型验证[J].计算机技术与发展,2009,19(12):240-242.

[12] 范飞虎.基于FPGA的MPEG-2/4AAC音频解码器的设计与验证[D].西安:西安电子科技大学,2013.

[13]ISO/IEC.ISO/IEC13818-7:MPEG-2AAC,SecondEdition[S].[s.l.]:ISO/IEC,2003.

[14] 申 敏,曹聪玲.基于SoC设计的软硬件协同验证技术研究[J].电子测试,2009(3):9-12.

Architecture and Verification for H.264/AVC Decode SoC

CAO Peng-peng,TIAN Ze,XU Hong-jie,ZHAO Qiang,CHEN Wei-yu

(Key Laboratory of Aviation Science and Technology on Integrated Circuit and Micro-system Design,AVIC Computing Technique Research Institute,Xi’an 710068,China)

H.264 is a high performance video codec technology.It is enhanced in the performance and efficiency of video codec,and also improved in error recovery,network adaptive function and so on.So it has broad prospect.The raional design and verification of the architecture is very important to the H.264/AVC SoC.Based on the research of H.264/AVC SoC architecture,it constructs FPGA verification platform,and studies the programming structure,the software framework and implementation of verification in depth.Firstly,the architecture of the SoC is designed,which provides a powerful support for the verification of H.264/AVC Decode SoC.Secondly,by building the FPGA test platform,the function and performance of the SoC is verified in FPGA.The verification results show that the system based on the architecture is correct.It can meet the needs of real-time decoding and provides a important support for the design and verification for H.264/AVC Decode SoC.

H.264;decode;FPGA;verification

2014-10-13

2015-01-05

时间:2016-05-05

中国航空科学基金(2015ZC51036)

曹朋朋(1984-),男,硕士,研究方向为集成电路设计;田 泽,博士,研究员,中国航空工业集团首席技术专家,研究方向为SoC设计、嵌入式系统设计、VLSI设计。

http://www.cnki.net/kcms/detail/61.1450.TP.20160505.0814.008.html

TP39

A

1673-629X(2016)05-0153-03

10.3969/j.issn.1673-629X.2016.05.033