高稳可变频率源的低杂散设计与实现*

2016-02-05解东亮潘明海

解东亮,潘明海,王 龙

(南京航空航天大学电子信息工程学院,江苏 南京 210016)

高稳可变频率源的低杂散设计与实现*

解东亮,潘明海,王 龙

(南京航空航天大学电子信息工程学院,江苏 南京 210016)

现代雷达电子对抗广泛使用DRFM对雷达信号进行采样、存储与处理。传统频率合成技术无法同时满足高性能DRFM对频率信号的稳定、低杂散、多路相参等指标要求。研究了频率源输出信号的抖动与杂散谐波对采样系统杂散性能的影响,结合传统频率合成技术,设计了基于FPGA和低噪声时钟抖动消除器的频率源电路,并对初级信号的谐波抑制设计了基于带通滤波器和微带滤波器的窄带滤波电路。最后,对系统的测试结果表明,本设计可输出多路频率范围为2.27~2600MHz(分段)的频率信号,步进小于10kHz。信号相位噪声优于-95dBc/Hz @100kHz,杂散抑制优于-60dBc。

频率源;低杂散;谐波抑制;滤波电路

0 引言

DRFM技术可以产生相干的雷达回波信号,从而实现对雷达系统的欺骗干扰,是针对现代相干体制雷达的有效方法[1-2]。其对雷达信号处理的关键环节是高精度采样与重构[3-4],需要一个高质量的频率源作为采样时钟。为了保证系统频率的相关性,频率源不仅需要为DRFM提供采样时钟,同时也要为上、下变频模块提供本振信号。频率源输出信号的稳定度、谐波杂散等性能直接影响整体系统的性能指标。目前,频率源的主要实现方法是采用频率合成技术,按合成方法不同可分为直接模拟合成、直接数字合成、间接数字合成三种。其中,直接模拟合成方法是通过混频器、倍频器以及分频器等模拟电路实现频率的合成,其优点在于相位噪声抑制较好,但其电路复杂,功耗和成本较大。直接数字合成即DDS技术,通过数字技术产生一组数字序列,再利用数模转换器将数字序列转换为模拟输出,其优势在于频率步进小、电路简单,但受制于数模转换器的输出性能有限,所以合成频率的信号频率不高,杂散抑制性能不足。间接频率合成使用锁相环技术,通过鉴相器、环路滤波器、分频器等构建闭路反馈系统实现频率合成。锁相环技术输出频带较宽、杂散抑制高,但相位噪声抑制能力不足[5]。

在实际工程应用中,常需要多路相参的不同频率信号,三种频率合成技术并不能满足需求。本文设计的高稳可变频率源使用锁相环技术,并通过FPGA控制分频比,可实现多路相参的频率输出,同时针对谐波抑制需求较高的应用设计了窄带滤波电路,既可以满足多路相参可变频率信号的需求,又保证了输出频率的杂散性能及稳定度。

1 频率源信号杂散对采样系统性能的影响

1.1 时钟抖动对杂散性能影响

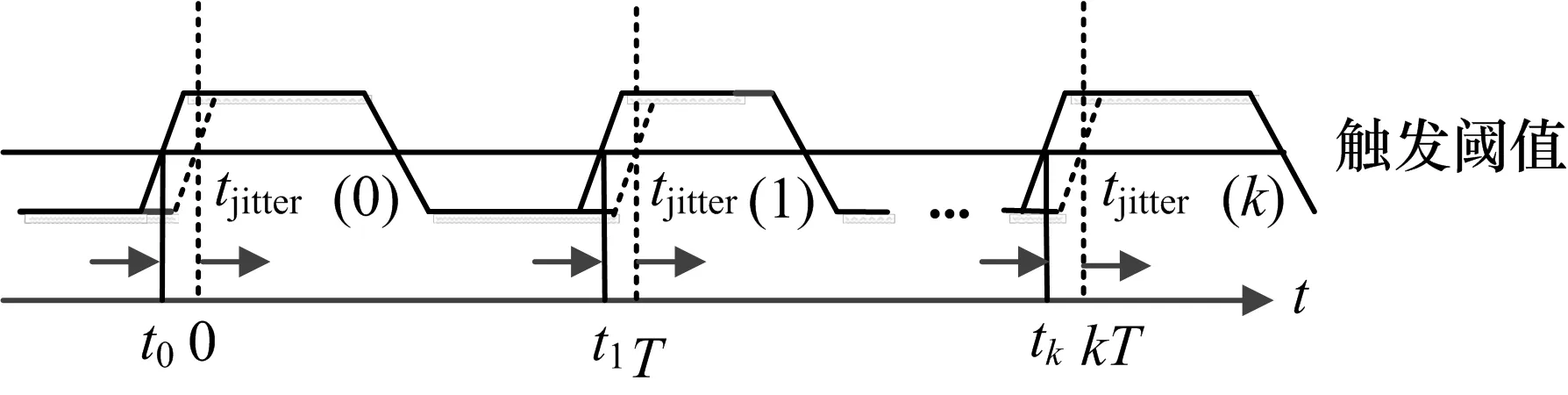

DRFM在进行高速采样时,采样时钟的抖动和杂散对整体系统的杂散性能有着决定性的影响。时钟抖动是指时域上实际时钟与理想时钟相比存在的超前或滞后的偏移,通常可以分为长周期抖动、均方根抖动和周期间抖动等。对于采样系统而言,主要受到周期间抖动(时钟的连续周期间的偏差)的影响[6]。周期性时钟抖动的示意图如图1所示,其中虚线波形表示理想时钟的上升沿,实线波形表示实际时钟,水平直线是ADC中时钟电路的触发阈值,tk是第k个时钟沿的实际时间,即实线波形相邻两个上升沿与触发阈值的交点时刻,虚线波形与触发阈值的交点时刻为kT。

图1 时钟抖动时域示意图

图中tjitter(k)是第k个时钟边沿的抖动,定义为:

tjitter(k)=tk-kT

(1)

关于时钟抖动和采样系统相位噪声关系的研究较多[7-9],宽带采样系统的信噪比与采样时钟的抖动密切相关,忽略量化噪声等因素影响,由时钟抖动引起的输出信号的信噪比的公式如下:

(2)

式中,tjitter为时钟抖动。由式(2)可以看出,在采样系统设计时,根据系统工作频率和信噪比要求可以计算出对应的时钟抖动:

(3)

通过以上分析可知,随着输入信号频率的提高,采样系统对时钟抖动的可接受最大范围也越来越苛刻,除了根据式(3)可以计算时钟抖动外,许多高性能ADC和DAC器件也提供了不同输入频率下对时钟抖动的限制条件[10],可以为系统设计提供参考。

1.2 杂散谐波分量对采样系统杂散性能的影响

在频率源的研制过程中,会因为PCB版布线、电源输入噪声、参考信号噪声等的影响而使得输出信号中混杂一些谐波分量,这些谐波分量有的幅度较高,会严重影响采样系统的杂散性能。

设含有谐波分量的采样时钟信号为sspur(t),频率fs、幅度为As。

sspur(t)=Assin(2πfst)+Acsin(2πfct)

(4)

式中,fc和Ac是杂散谐波分量的频率和幅度,基于理想时钟的采样时刻为时钟信号的正向过零时刻,即s(t)=0。设谐波分量导致采样时刻出现的偏移时间为ΔT,令:

Assin(2πfs(t+ΔT))+Acsin(2πfc(t+ΔT))=0

(5)

通常情况下谐波分量幅度要远小于时钟信号幅度,可认为As≫Ac,ΔT≈0,则可以得到偏移时间为:

(6)

设采样系统的采样信号为x(t),其经过采样输出为:

(7)

由式(7)可以看出,采样系统的采样时钟信号中含有谐波分量,导致采样输出信号中也混杂了杂散分量,当谐波分量频率较高时,会因为不满足奈奎斯特采样定理而产生欠采样,导致采样后的信号产生混叠,在基带内会出现杂散分量,其频率位置为:

(8)

同时,计算出输出信号中杂散的幅度后还可以计算出系统的杂散电平SFDR为:

(9)

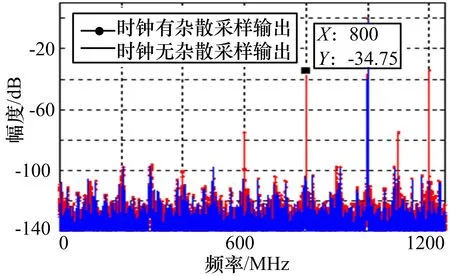

图2是使用Matlab软件对1GHz采样信号进行仿真得到的采样输出频谱,其中采样时钟fs=2.5GHz,杂散分量fc=2.5GHz。由于欠采样导致在基带内800MHz处产生了杂散谐波,其杂散电平值为-34.75dBc,与根据式(9)计算出的理论杂散电平值-34.0dBc近似一致(误差是因式(7)近似取值而产生的)。

图2 1GHz采样信号输出频谱

可以看出,采样时钟的抖动和杂散直接影响了采样系统的杂散指标,因此在频率源为高精度数据采样系统提供采样时钟输入时,必须根据系统指标要求,针对谐波分量进行滤波处理,并在设计研制过程中从布线、串扰、噪声引入等方面优化设计。

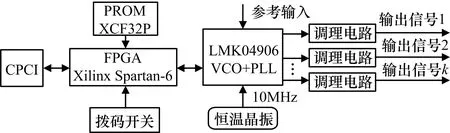

2 频率源的设计与实现

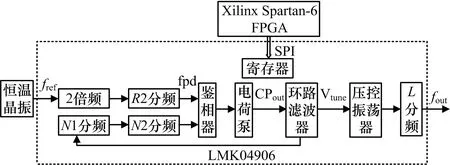

本设计可输出多路2.27~2600MHz(频段2.27~236.36、263.3~288.9、296.25~325、338.6~371.4、395.7~433、474~520、592.5~650、790~866.7、1185~1300、2370~2600MHz)频带内的高稳定频率可变时钟信号。频率源采用FPGA控制时钟抖动消除器产生时钟信号,由于高频段信号杂散较为复杂,本频率源针对信号杂散抑制设计了灵活的时钟调理电路。本时钟源硬件设计方案如图3 所示。

图3 时钟源硬件设计框图

2.1 频率源硬件设计

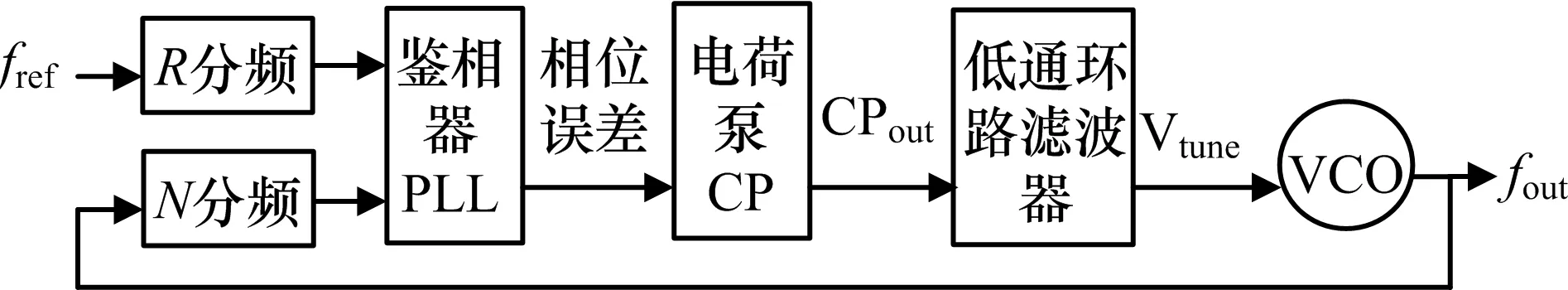

频率源使用FPGA控制高稳定超低噪声时钟抖动消除器产生初级频率信号。超低噪声时钟抖动消除器采用TI公司的LMK04906,该器件输出信号频偏在100Hz~20MHz内的RMS(均方根抖动)为123fs,可以保证输出信号的高稳定度。频率产生基于集成高性能压控振荡器(VCO)型锁相环(Phase Locked Loop,简称PLL)原理。VCO型锁相环的结构原理如图4所示,其在工作时利用鉴相器产生相位误差来驱动电荷泵产生与相位误差对应的正/负电流脉冲串CPout。低通滤波器通过对CPout求积分产生“干净”的电压信号Vtune来驱动VCO产生对应频率。

图4 PLL型VCO原理框图

对LMK04906的控制采用Xilinx Spartan-6系列FPGA芯片XC6SLX25,该芯片接口丰富,价格较低,有利于降低频率源成本。FPGA对LMK04906的控制模式采用SPI接口总线,通过配置LMK04906的寄存器设置其各项输出参数。LMK04906采用双环路 PLLatinum 锁相环架构可工作于单/双PLL模式。其工作原理如图5所示。

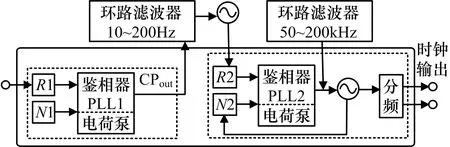

图5 双PLL工作原理框图

当工作在双PLL模式时,PLL1在外部参考信号的驱动下为PLL2提供精确的低相噪参考时钟,需要为第一级环路滤波器设计窄带滤波器(带宽10~200Hz)以过滤外部噪声。第二级环路滤波器带宽设置为50~200kHz,借助片内VCO高频偏处和板上VCO低频偏处的良好的相噪特性,可输出极低相噪的频率信号。

当工作在单PLL模式时,不需要PLL1和外部参考输入,只需要一款压控晶振为PLL2提供输入即可。

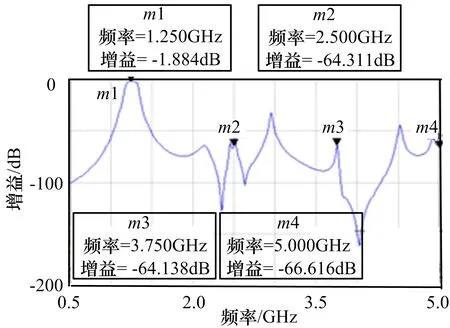

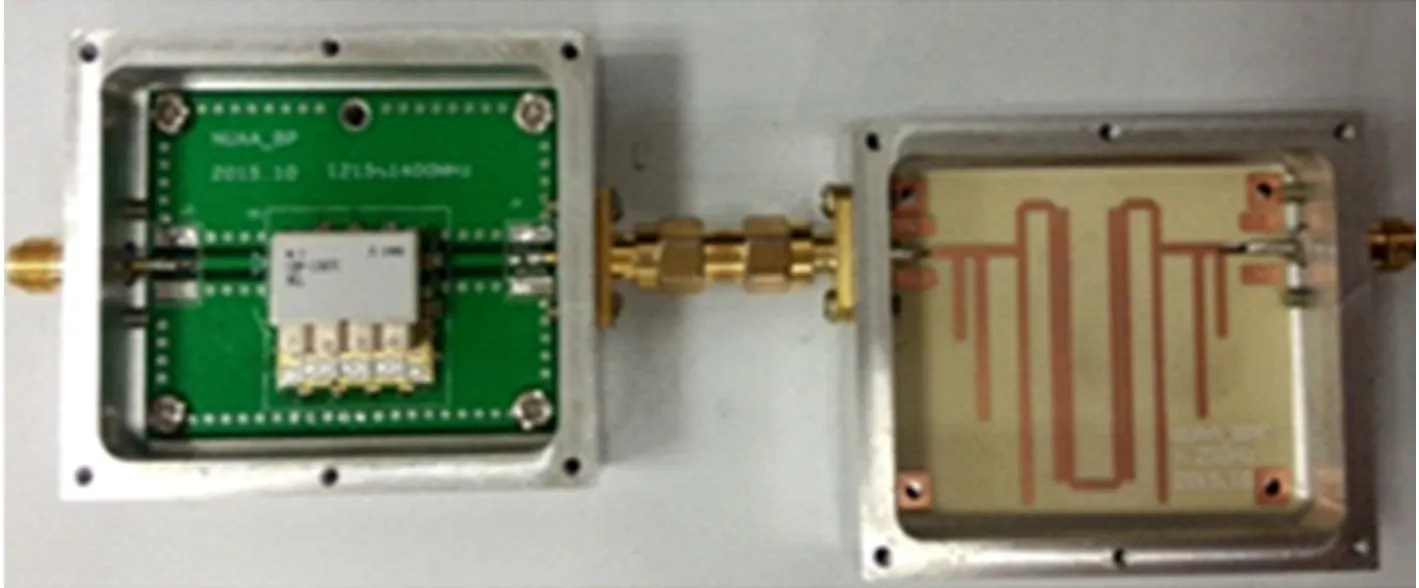

为进一步提高输出频率的杂散性能,设计了基于带通滤波器与微带滤波器级联的窄带滤波链路。以1.25GHz输出频率为例,带通滤波器选择Mini公司的CBP-1307C+,其通带范围为1215~1400MHz,2.5GHz处抑制约为62dB。微带滤波电路采用抽头式发夹型设计[11],可以对2.5GHz和3.75GHz处的谐波进行更“干净”的过滤。其全带宽插损仿真结果如图6所示,其中m2和m3分别为二次、三次谐波频率点。

图6 微带滤波电路全带宽插损

2.2 频率源步进设计

频率源的步进由FPGA控制LMK0490内部的各级分频器来实现,如图7所示,恒温晶振输出10MHz参考信号经R2分频产生鉴相频率,分频器R2取值范围1~4095,因此鉴相频率fpd范围为4.52~4.96kHz。VCO输出的分频反馈信号在经N1分频时分频比最小值为2,所以VCO输出信号分辨率为2fpd即9.04~9.92kHz,由于VCO输出时钟还要经过输出分频器L的最终分频(分频比1~1045),因此最终输出时钟分辨率为2fpd,即在2.37~2.6GHz段为9.04~9.92kHz,在1.185~1.3GHz段为4.52~4.96kHz,以此类推。

图7 VCO型锁相环结构原理

3 实验测试与分析

3.1 时钟源系统实物

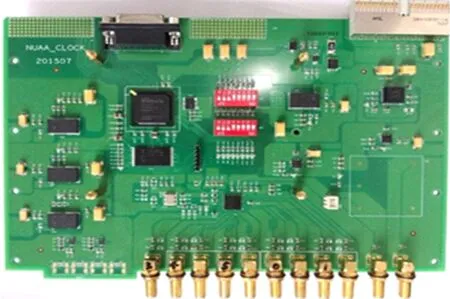

高频低杂散时钟源时钟产生模块采用CPCI 6U标准板卡设计,6层叠层,实物如图8所示,时钟调理单元如图9所示。

图8 时钟产生模块电路板

图9 1.25GHz输出调理电路实物

3.2 测试结果及分析

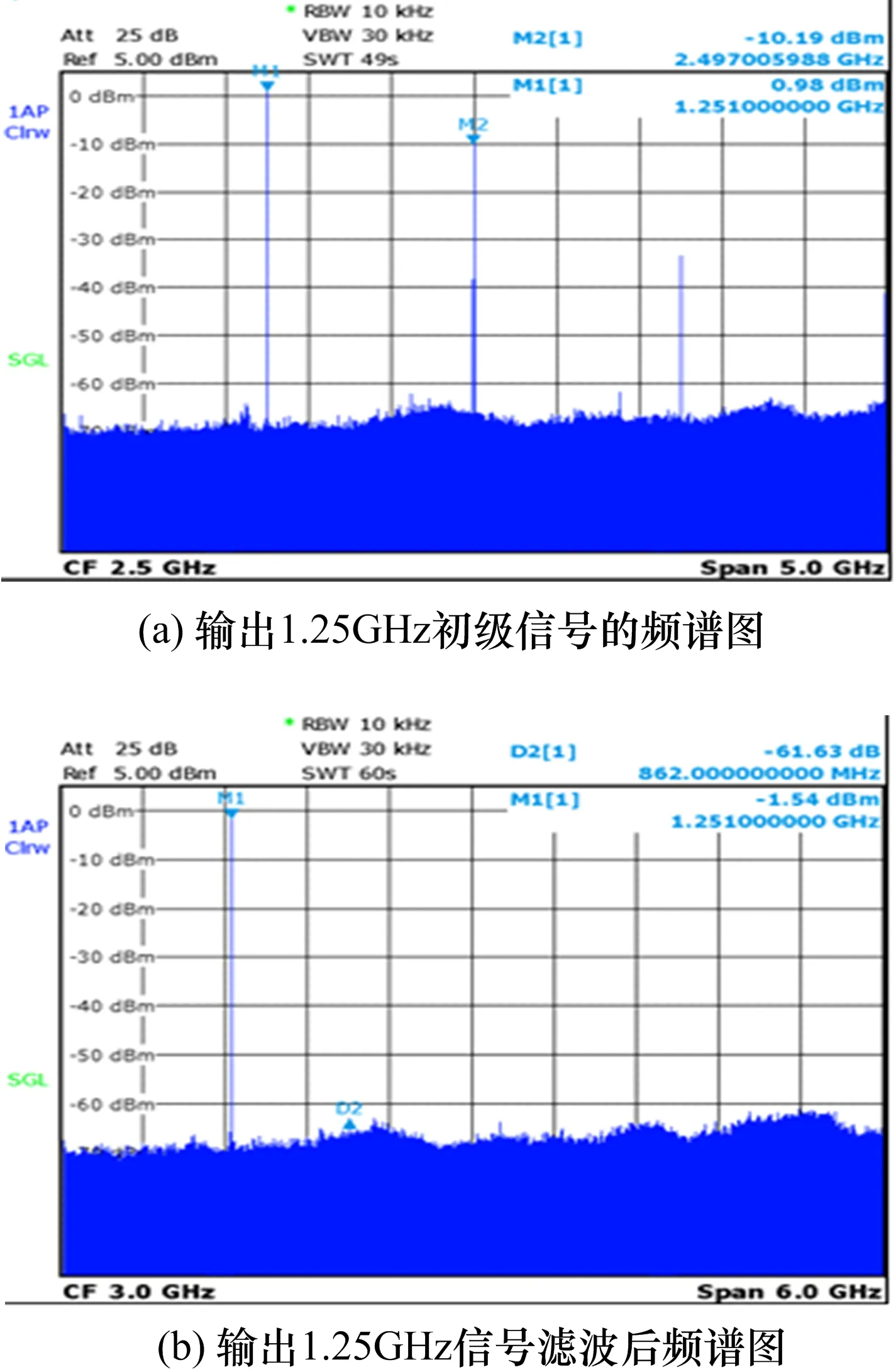

对时钟源输出信号的测试采取的方法是使用频谱仪FSL6测试1.25GHz输出信号的杂散以及相噪等参数。测试结果如图10所示,图10(a)是未经滤波处理的初级输出信号,可以看出1.25GHz时钟信号的功率分别为0.98dBm,二次谐波(2.5GHz)为-10.19dBc,三次谐波(3.75GHz)为-34dBc,除谐波外无其他恶性杂散信号。图10(b)是输出1.25GHz信号滤波后频谱图。图11是最终输出的1.25GHz杂散均抑制在60dBc以下,完全达到设计指标要求。

图10 输出1.25GHz信号滤波前后频谱图

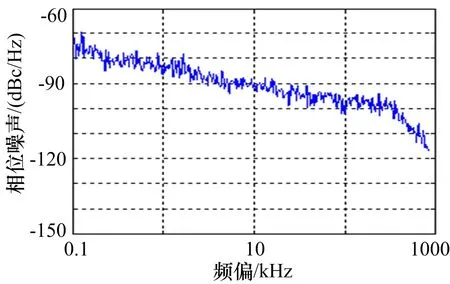

使用R&S频谱仪对输出的1.25GHz频率信号测试的相位噪声数据如图11所示,其中在频偏100kHz处的相位噪声为-98dBc/Hz@100kHz,满足设计要求。

图11 输出1.25GHz信号的相位噪声

4 结束语

本文针对宽带DRFM系统的应用需求,研究了采样时钟的抖动和杂散对DRFM系统采样性能的影响,提出了一种基于FPGA和超低噪声时钟抖动消除器的低杂散时钟源系统,最后对系统输出进行了测试。测试结果表明,本设计输出的频率信号完全满足宽带DRFM的需求,并且电路设计灵活,通用性高。本方案已应用于某带宽1GHz的DRFM预研系统实物中,具有较高的工程应用价值。■

[1] 杨会军,王根弟.基于DRFM的弹载自卫式单脉冲雷达干扰技术[J].航天电子对抗,2011,27(1):6-9.

[2] 李彦栓,潘理刚.基于DRFM的欺骗干扰与压制干扰技术研究[J].电子科技,2015,28(6):158-161.

[3] Scott DB. Digital radio frequency memory linear range gate stealer spectrum[J]. IEEE Trans. on Aerospace and Electronics Systems, 2003,39(2):725-735.

[4] Yang Jing, Guo Xiaoxu, Li Yunjie. Design of a novel DRFM jamming system based on AFB-SFB[C]∥ IET International Radar Conference 2013,2013:1-5.

[5] 张娟. 合成频率源的研究与实现[D]. 重庆:重庆大学, 2011.

[6] 段宗明,柴文乾,代传堂.时钟抖动和相位噪声对数据采集的影响[J] .雷达科学与技术,2010,8(4):372-375.

[7] 杨小军,陈曦,张庆民.时钟抖动对ADC变换性能影响的仿真与研究[J].中国科学技术大学学报,2005,35(1):66-73.

[8] 宋屾,焦淑红,胡尔富. 时钟抖动和相位噪声关系的研究[J].应用科技, 2006,33(4):1-3.

[10]骆守峰,赵丕杰.射频直接采样系统中等效相位噪声模型分析[J].现代雷达,2014,36(2):71-73.

[11]万君磊,潘明海. 新型微带抽头式发夹型带通滤波器的设计[J].微波学报,2015,31(4).

Low spurious design and implement of a high-stability and adjustable frequency source

Xie Dongliang, Pan Minghai,Wang Long

(College of Electronic and Information Engineering,Nanjing University of Aeronautics and Astronautics,Nanjing 210016,Jiangsu,China)

DRFM is widely used to sample, store and process radar signals in modern radar electronic countermeasure. The traditional frequency synthesis cannot satisfy the requirements of the high-performance DRFM simultaneously to the stability, low spurious and multi-channel synchronization of frequency signal. The effect of the jitter and harmonic component of frequency signal to the sample system spurious performance is studied, and the frequency source based on FPGA and low-noise compliant clock jitter cleaner is proposed by combining the traditional frequency synthesis. Furthermore, the narrow band filter based on band-pass filter and microstrip filter are designed to suppress the harmonic component of original signal. According to the measurement results, multi-channel frequency signal within 2.27~2600MHz is generated. The step frequency is less than 10kHz, and phase noise is better than -95dBc/Hz@100kHz, and harmonic suppression is better than -60dBc.

frequency source;low spurious;harmonic suppression;filter circuit

国家自然科学基金(61271327);江苏高校优势学科建设工程项目资助课题。

2016-09-08;2016-09-10修回。

解东亮(1991-),男,硕士研究生,主要研究方向为射频系统设计与仿真。

TN911

A