独立多通道DDS同步技术研究与实现

2016-01-28钱焕裕周叶华

钱焕裕,程 明,周叶华

(中国电子科技集团公司第36研究所,嘉兴 314033)

独立多通道DDS同步技术研究与实现

钱焕裕,程明,周叶华

(中国电子科技集团公司第36研究所,嘉兴 314033)

摘要:本地激励信号源是无线电系统的重要组成部分。在很多应用中,需要实现多个本地信号之间的相位同步,来达到精确测试测量的目的。从直接数字合成(DDS)时钟的工作原理出发,对DDS的同步方法进行了全面而详细地理论分析。最后结合AD9910芯片设计了一个独立多通道DDS同步输出系统。通过测试,验证了本文论述方案的可行性。

关键词:直接数字合成;同步;独立多通道

0引言

在现代通信、雷达、测试系统、电子对抗等领域,通常需要实现多路激励信号之间的相位同步,来达到准确测量、精确定位、精确成像、增强抗干扰能力的目的。激励信号的传统产生方法有直接频率合成和锁相环频率合成2种。对直接频率合成而言,产生不同频率所需要的信号路径不同,链路中包含的放大、混频器件数量也不尽相同,因此很难在多路输出以及频率切换时保证输出激励源的相位连续与同步。对锁相环频率合成而言,小数分频比的相位随机性以及器件相位特性的温度漂移也很难保证电路的稳定工作。

随着现代电子技术和微电子技术的发展,直接数字合成(DDS)技术也得到了迅猛的发展,成为一种新的频率合成的主要方式。因其具有频率转换时间短、频率分辨率高、相位输出连续、可编程控制、全数字化结构、便于集成等优点,在通信、雷达、测试系统、电子对抗等领域得到了十分广泛的应用[1]。因此研究如何使多个DDS芯片之间的输出信号同步,具有重要的实用价值。

由于市场上DDS芯片的种类较多,不同DDS芯片的同步方式可能会有所不同,本文将从DDS的时钟系统入手,对不同DDS的时钟系统进行比较;针对时钟系统特点,分析了同步的方法;在此基础上,结合AD9910设计了一个独立多通道DDS同步输出信号源[2-5]。

1DDS时钟系统

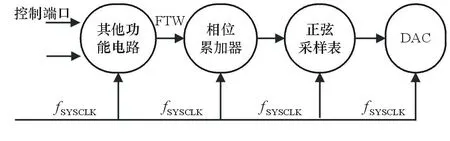

所谓DDS的时钟系统是指DDS内部将输入参考时钟信号进行倍频、分频后,提供内部给数字电路、模数混合电路的时钟分配链路系统。根据DDS的工作时钟频率大小,一般可以分为直接式和间接式2种。图1所示框图是当DDS系统工作时钟相对较低时,DDS内部的时钟分配方式框图,其中的fSYSCLK即为DDS的系统工作时钟。

图1 低速率DDS时钟分配框图

其可由外部直接提供或者经过内部锁相环将外部低速率时钟倍频后提供。DDS内部各功能电路的工作时钟均由fSYSCLK直接提供,不再对其进行分频处理。具有这种时钟系统的DDS,其工作时钟一般在300 MHz以下,且不具有片内辅助同步功能。

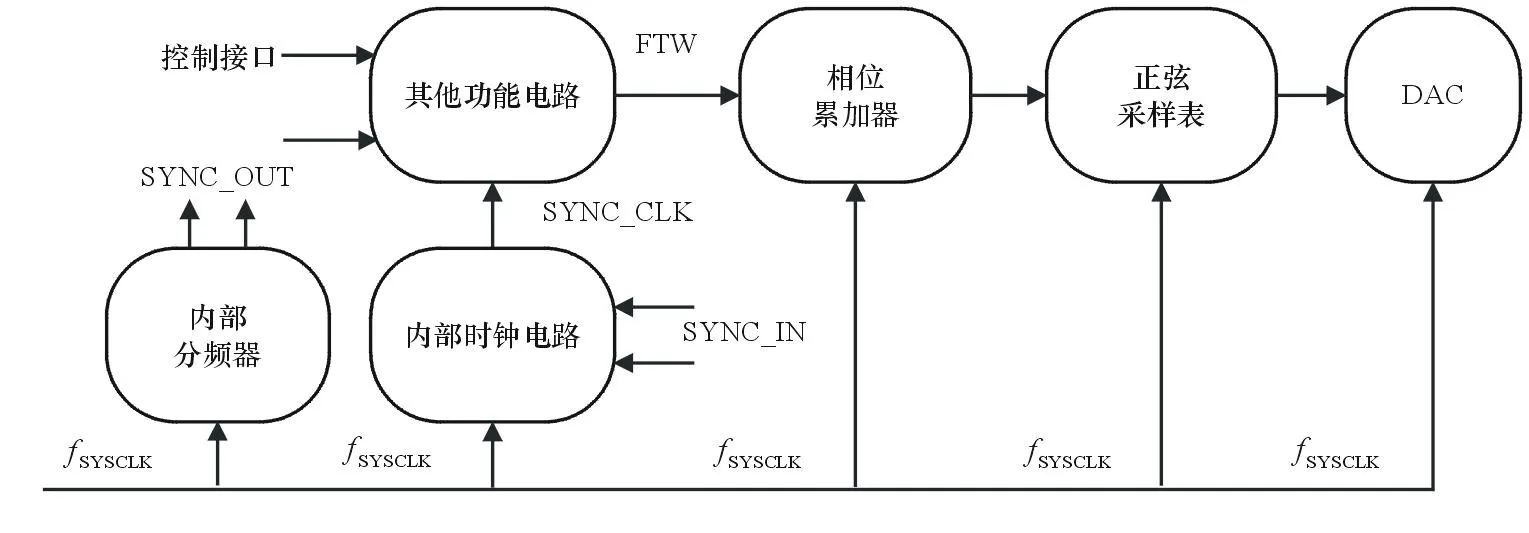

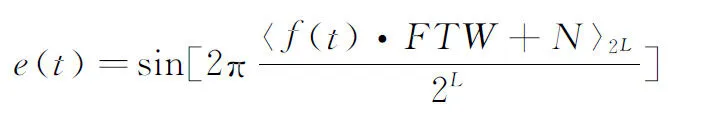

图2所示框图为DDS的系统工作时钟相对较高时DDS内部的时钟分配方式框图,其中的fSYSCLK同样为DDS的系统工作时钟,同样也可由外部直接提供或者经过内部锁相环将外部低速率时钟倍频后提供。为了满足输出频率与采样率之间的要求,数/模转换器(DAC)、相位累加器等信号产生模块的工作时钟依然由fSYSCLK直接提供。但是,受到设计成本与工艺等条件的限制,控制接口、寄存器及其缓存更新电路等其他功能电路的工作时钟由SYNC_CLK提供,一般由fSYSCLK分频得到,也会控制在300 MHz以下。为了能够实现同步功能,具有这种时钟系统的DDS配有内部辅助同步电路。图中的SYNC_OUT和SYNC_IN即为用于辅助同步的2个时钟接口。

图2 高速率DDS时钟分配框图

2DDS同步方法

根据图1和图2,可以分析得到DDS同步方法。为了使得到的结果更加直观,需要分析DDS的原理,得到输出信号的表达式。

根据DDS的工作原理,相位累加器对频率控制字(FTW)进行相位累加,以累加器的结果为地址,对正弦采样表只读存储器(ROM)进行访问,得到幅度量化值,再通过DAC将幅度量化值转换为输出模拟电信号。因此,DDS电路相当于一个信号采样输出电路。若将采样过程近似为理想采样,则采样信号的数学表示形式为:

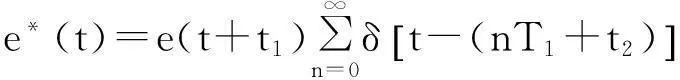

(1)

式中:e*(f)为采样输出信号;δ[t-(nT1+t2)]为采样函数,理想情况下为单位理想狄拉克函数;周期T1即为fSYSCLK的倒数;t2可理解为fSYSCLK的初始相位;t1为FTW被送至相位累加器开始有效的时刻,也可理解为被采样信号的初始相位;e(t+t1)为被采样信号,其表达式为:

(2)

f(t)=int(t/T1)

(3)

式中:L为FTW的位数;f(t)由式(3)给出;〈·〉2L是除以2L取余数的过程;N为更新FTW时相位累加器已有的初始值,表现在输出上是DDS频率跳变时刻信号的幅度值;N值表现出了DDS输出在频率跳变时的相位连续性;int(t/T1)为相除取结果整数的运算。

从以上3个式子可以分析得到,要想使输出信号相位同步,就必须满足以下3个条件:

(1) 需要具有相位同步的fSYSCLK信号,使多个采样系统之间具有相同的采样周期T和采样时钟初相位t2。

(2) 需要具有上升边沿对齐的数据更新信号,使多个采样系统之间具有相同的t1。因为int(t/T1)存在取整过程,所以允许更新信号上升沿的到达时间存在小于1个系统时钟周期的误差。

(3) DDS输出必须有相同的初始相位,即必须具有相同的N值。

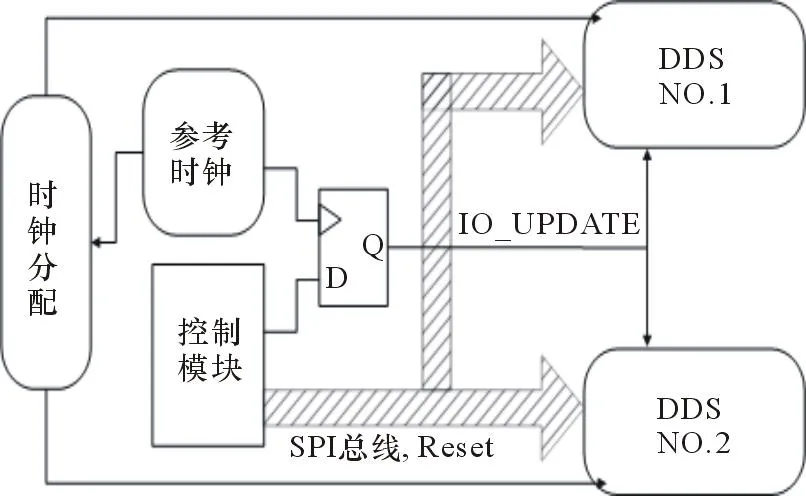

根据上面的分析,针对低速率时钟DDS的输出相位同步方法(如图3所示),该方法可以将图中的2个DDS扩展到任意多个。方法的关键在于实现根据式(1)和式(2)论述的3个条件。

图3 低速率时钟DDS同步方法

首先,将参考通过倍频方式提高到DDS正常工作所需要的频率,利用时钟分频器使时钟输出与DDS时钟输入之间做到电平和接口匹配,其中时钟分频器输出时钟送到多个DDS的参考时钟输入端时,参考时钟必须具有相同的相位。其次,利用参考时钟和D触发器将控制模块给出的异步数据更新信号转变为与DDS时钟同步的信号,更新信号到达各个DDS输入必须有相同的相位。最后,在控制上,系统上电之后,应向DDS给出Reset信号,使DDS具有相同的初始状态。

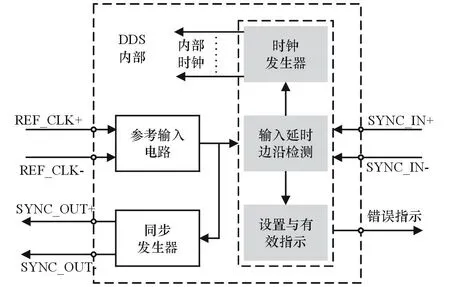

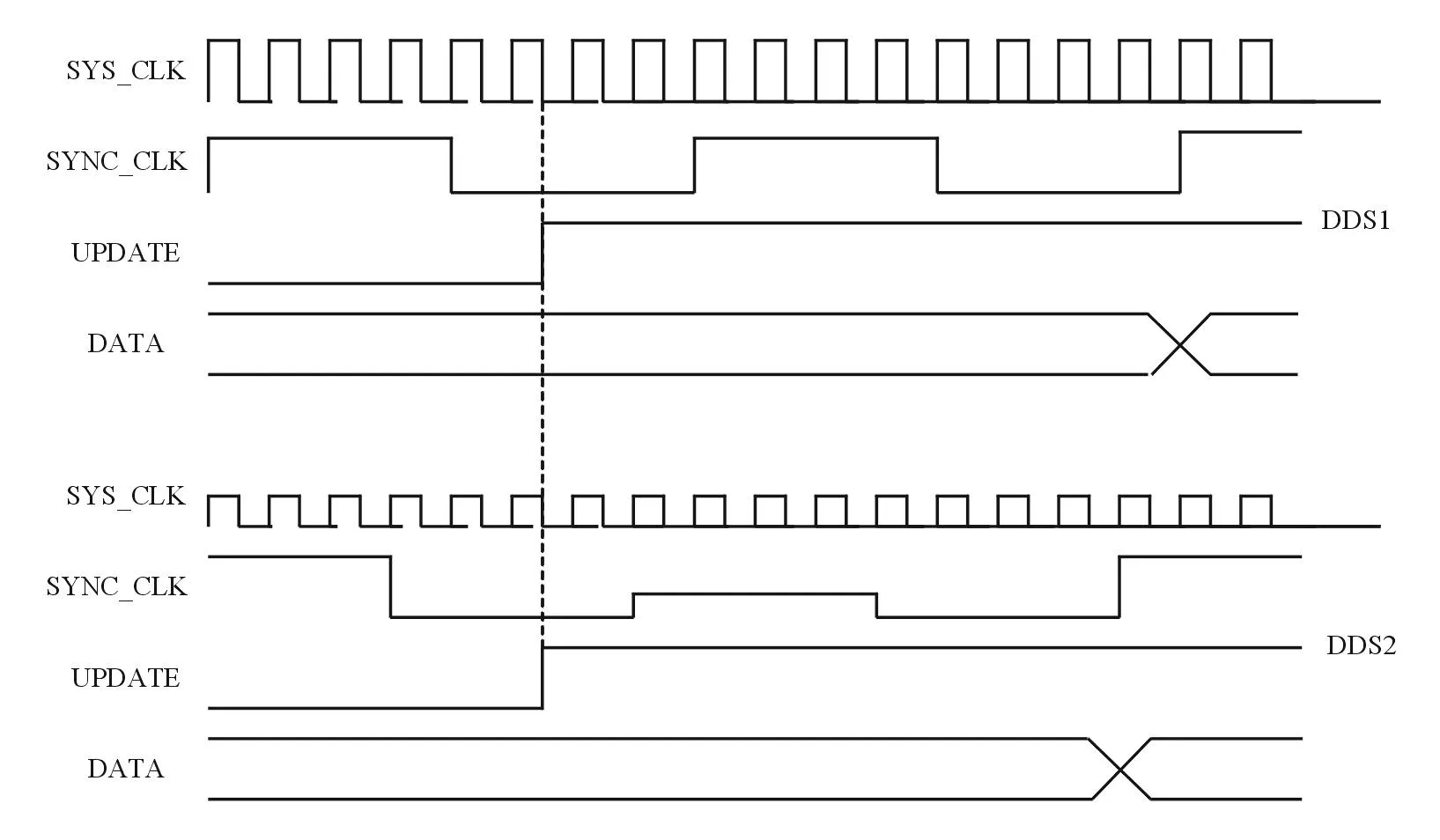

高速率时钟DDS做到参考时钟同步的同时,要注意内部辅助电路的工作时钟是由参考时钟分频得来,所以即使参考时钟是同步的,辅助电路工作时钟也未必是同步的,这就导致即使控制电路送给DDS的数据更新信号同步,数据更新过程也无法同步。图4给出了典型DDS辅助电路的时钟产生电路和辅助同步电路示意图。图5针对这一现象给出了说明。

图4 DDS辅助同步电路示意图

图5 辅助电路时钟不同步现象

从图5看出,即使外部给出了上升沿对齐的数据更新信号,但由于SYNC_CLK不同步,仍导致了参数t1的不同。由于这种原因,需要利用DDS内部的辅助同步电路保证内部辅助电路的时钟同步性。

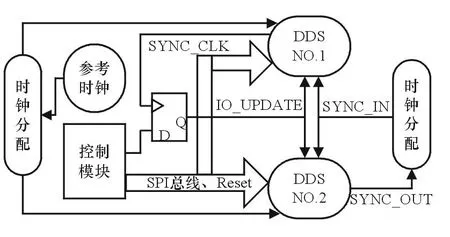

图6给出了高速率时钟DDS的同步方法,将其中一个DDS作为主器件,其他DDS作为从器件。由主器件提供SYNC_OUT,经时钟分配器后反馈给主从DDS,并保证相位同步。将D触发器的时钟由原来的参考时钟变为DDS输出的SYNC_CLK,保证更新信号与内部辅助电路的同步。

图6 高速率时钟DDS同步方法

3基于AD9910的DDS同步设计

3.1 设计原理

现需要设计一个DDS输出同步系统,通道数为6,DDS与控制模块均实现单板设计,即系统将包含6个DDS板和1个控制板,DDS将以板卡的方式插在控制模块上。

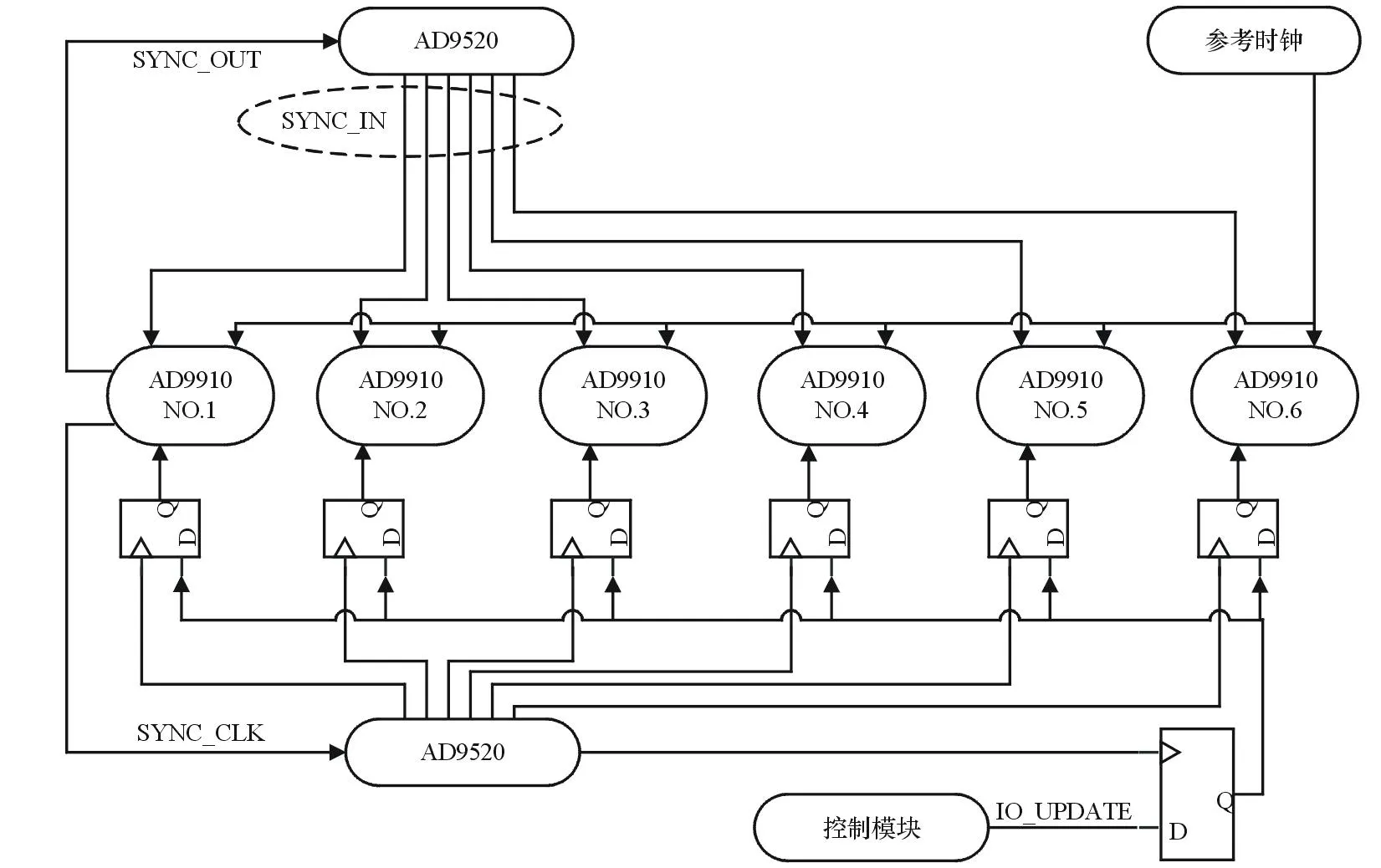

根据无杂散动态范围和相位噪声等指标的要求,可选择工作时钟高达1 GHz的AD9910作为系统的DDS芯片。AD9910的时钟系统属于高速率时钟DDS类型,内部辅助电路工作时钟SYNC_CLK为工作时钟的四分频(约250 MHz),可选择图6所示的DDS同步方法。具体的实施框图如图7所示。

图7选择第1个AD9910作为主器件,其他5个DDS作为从器件,所有参考时钟引线、SYNC_CLK引线、SYNC_IN引线以及IO_UPDATE引线各自均为等长线,满足同频等相位的要求。

图7 AD9910独立多通道DDS同步方法

因为主DDS输出的SYNC_OUT信号以及SYNC_CLK信号无法同时驱动多个DDS和D触发器,方案中选择AD9520作为关键的时钟分配器。AD9520具有内置高速分频器,在增强时钟驱动能力的同时,可以将AD9910输出的高速SYNC_CLK以及SYNC_OUT时钟进行分频,最高分频比高达192,可以降低D触发器的频率要求以及印制电路板(PCB)信号完整性要求,而且AD9520的输入输出接口与SYNC _OUT、SYNC _IN接口兼容,便于电路设计。

因为数据更新信号是突发性、非连续的数字信号,经过长距离的传输可能出现上升沿变缓或者振铃现象,降低信号同步的可靠性。为了增强数据更新信号的可靠性,在控制模块输出端和DDS输入端各插入1个D触发器,对信号进行整形的同时降低1个SYNC_CLK时钟的信号边沿误差。

方案实施实物图如图8所示。

图8 实物图

3.2 测试结果

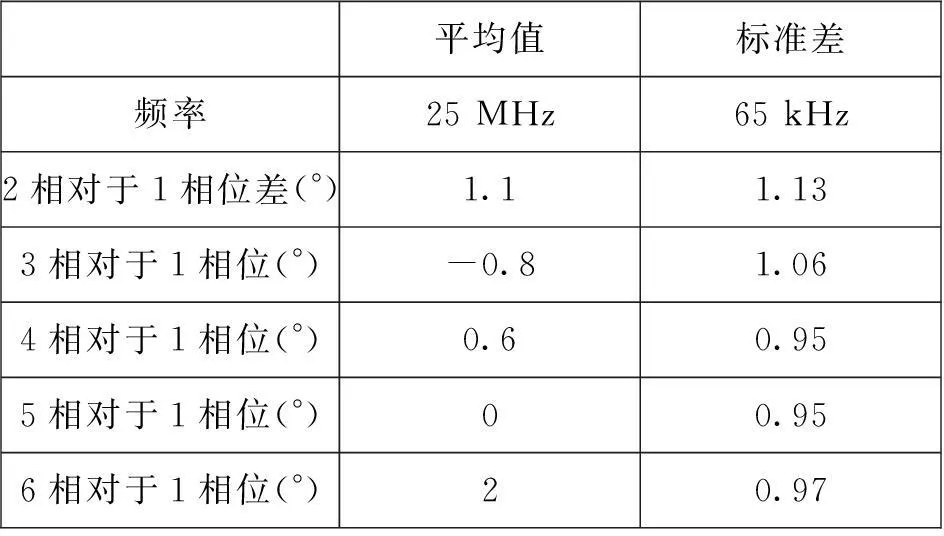

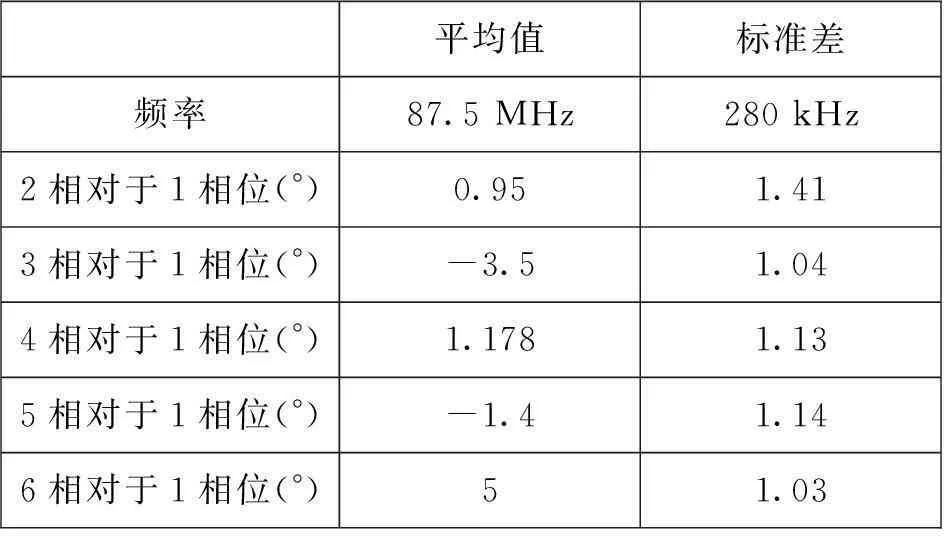

以第一通道为参考标准,表1和表2分别给出了DDS输出频率在25 MHz和87.5 MHz时,用示波器测量的各个通道相对于第一通道的相位差。

表1 25 MHz输出6通道相位差

平均值的平均次数为32次,测试过程中由于线缆引入的误差约为±1°。从测试数据可以看出,在测量误差范围以内,各个通道之间的输出相位差小于10°,同频输出时,相位关系不随频率来回切换而变化,不随工作时间长短而变化。

表2 87.5 MHz输出6通道相位差

4结束语

在工程设计中,采用锁相环或者直接频率合成方法得到的激励源之间往往很难做到输出相位稳定同步,而且DDS具有前面两者所不具备的频率转换时间短、频率分辨率高等优点。

因此,研究DDS的相位同步方法十分必要。本文以DDS的时钟系统作为切入点,从采样系统的角度分析讨论了针对不同时钟系统DDS的同步方法。在此基础上,设计了基于AD9910的独立多通道输出相位同步系统。

测试结果表明,采用同步方案的各个通道的DDS输出相位基本同步,而且同频率输出时,相位关系不随频率来回切换而变化,不随工作时间长短而变化。

参考文献

[1]池志鹏,陶然,单涛.基于TMS320C6701 控制多片AD9852的接口电路的设计[J].电子技术应用,2004(3):58-60.

[2]张若禹,孙静.基于ISA总线的多路同步DDS信号源设计[J].电子技术应用,2006(4):34-37.

[3]曾铮,郑建宏.高速PCB板设计中的串扰问题和抑制方法[J].电子设计应用,2006(4):81-84.

[4]黄德勇,张扬,杨云志.高速电路设计中的信号完整性研究[J].电讯技术,2004(2):149-152.

[5]白居宪.直接数字频率合成[M].西安:西安交通大学出版社,2007.

Study and Realization of Synchronization Technology of

Independent Multi-channel DDS

QIAN Huan-yu,CHENG Ming,ZHOU Ye-hua

(No.36 Research Institute of CETC,Jiaxing 314033,China)

Abstract:Local excited signal resource is an important part of radio system.In a lot of application,phase synchronism among multiple local signals is necessary for accurate test and measurement.This paper theoretically analyzes the synchronization method of direct digital synthesis (DDS) completely and detailedly from the operation of DDS clock,designs an independent multi-channel phase synchronization system combing with AD9910.Through test,the feasibility of the method presented in this paper is validated.

Key words:direct digital synthesis;synchronization;independent multi-channel

收稿日期:2015-06-17

DOI:10.16426/j.cnki.jcdzdk.2015.05.023

中图分类号:TN741

文献标识码:B

文章编号:CN32-1413(2015)05-0103-05