基于CPCI架构的雷达告警处理板设计

2016-01-28周智勇

周智勇,常 勇,马 丹

(1.中国电子科技集团公司第51研究所,上海 201802;2.总参四部驻杭州地区军事代表室,杭州314033)

基于CPCI架构的雷达告警处理板设计

周智勇1,常勇2,马丹1

(1.中国电子科技集团公司第51研究所,上海 201802;2.总参四部驻杭州地区军事代表室,杭州314033)

摘要:介绍了基于计算机程序配置项目架构的雷达告警处理板,阐述了其内部组成、脉冲描述字形成及录取、低压差分信号总线的收发电路和外围设备接口时序。

关键词:雷达告警;计算机程序配置项目;低压差分信号总线

1设计方案

告警处理板主要完成告警预处理功能,采用模块化设计方案,利用自行研制的基于计算机程序配置项目(CPCI)接口的6U板卡,组成了依托现场可编程门阵列(FPGA)+数字信号处理器(DSP)实现的告警数据录取、脉冲描述字(PDW)形成、直接存储器存取(DMA)数据录取和高速信号分选、识别等功能,具有设备构造简单、可靠,数据处理高速、实时的特点。由于控制和数据传输采用低压差分信号(LVDS)高速串行差分总线,因而具有传输距离远、高速、抗干扰和易于扩展的特点[1]。

功能要求:

(1) 提供告警接收机状态控制信号;

(2) 完成告警数据录取和存储;

(3) 提供信号分选和识别的硬件平台;

(4) 完成与上位机通信,接收上位机指令,上报工作状态信息;

(5) 提供告警输出信号;

(6) 429总线的全球定位系统(GPS)、惯导数据的录取。

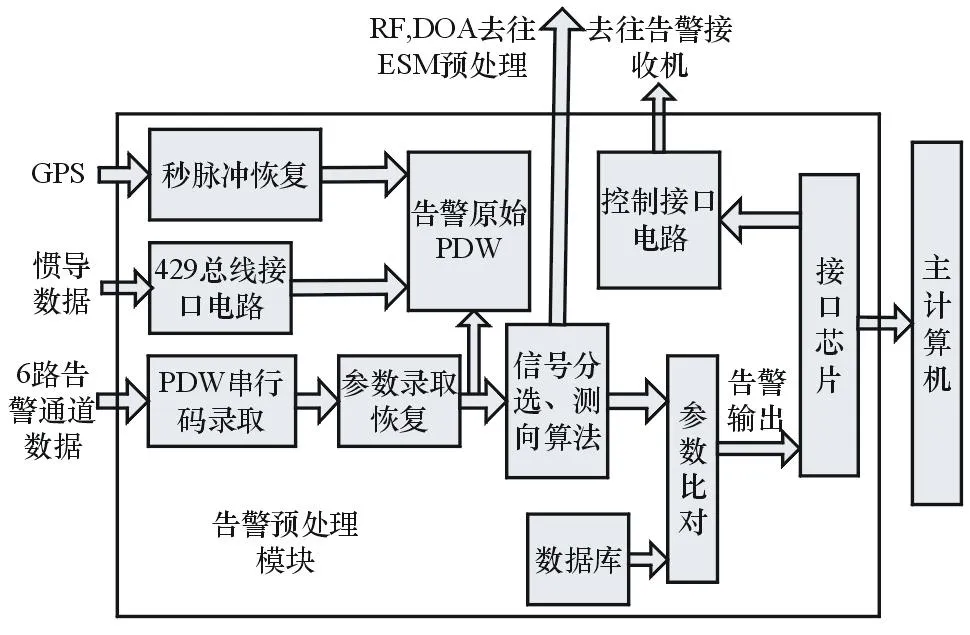

功能框图如图1所示。

图1 告警处理功能框图

告警预处理板接收告警接收机送来的6路信号描述字,从中解算出脉冲描述信息,包括脉冲到达时间、脉冲宽度、脉冲幅度、脉冲载频等诸多内容,全部为数字信号。一个脉冲描述字的位宽50位,系统通过串行调制器将并行数据转换为串行数据进行传输,在数据接收端通过解调器把串行数据解调为并行数据,实行数据的双向通讯只需要4根差分线。

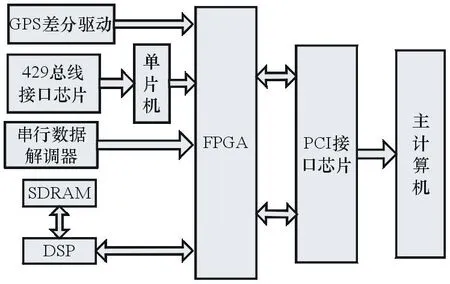

告警串行脉冲描述字经过串并转换形成PDW,根据要求送至DSP,然后通过告警算法计算出到达方向(DOA),并结合GPS和惯导信息,经过缓存直接送至主处理机进行后处理。原始PDW送至DSP完成信号分选识别,结合载机信息和主机数据库比对,进行信号类型、威胁等级判断,将结果通过计算机接口送到主处理计算机,同时将告警信号送出至电子自卫系统。其中告警处理数据还通过互连总线送至侦察预处理板[2]。 硬件组成框图如图2所示,实物照片如图3所示。

图2 告警处理硬件组成框图

图3 告警处理板实物照片

2主要电路设计

硬件电路中时序控制、录取告警数据以及PDW形成等功能采用FPGA来实现。FPGA具有较快的处理速度和良好的稳定性,同时又具有设计灵活、易于修改和维护的优点,可以适应不同的系统要求,采用灵活的结构满足不同的需要,提高了系统的适用性及可扩展性。本系统采用Altera公司的大容量FPGA StranixⅡ系列芯片EP2S60F672I4。负责接收PDW且将PDW送给DSP进行后续处理,还要负责DSP与主机的数据传输。同时外挂了2片16 Mbit的静态随机存储器(SRAM),可以用来缓存数据。此外, FPGA都接有检测口和指示灯,方便板卡的调试[3]。

而信号分选和识别等功能采用专用DSP来实现。DSP的运算速度和精度决定着系统的数据处理能力,同时也对整个系统的性能和结构产生重要的影响。DSP芯片选用的是TI公司的高速浮点DSP芯片TMS320C6713BGDPA-200,处理器时钟频率可达200 MHz,并且外围配备了384 MBytes的同步动态随机存储器(SDRAM),可以用来暂存大量的中间处理数据。

低压差分信号(LVDS)总线驱动器选择DS92LV1818TVV,而负责惯导数据录取时序的单片机采用TI公司的MSP4430F149IPM。

通过CPCI桥芯片PLX9054来实现板卡与主机的数据传输,采用32 bit、33 MHz的PCI总线,峰值传输速率可达132 MBytes/s。

2.1 串行PDW解码电路设计

因系统采用数字告警接收机,其输出为原始PDW,包括射频(RF)、脉宽(PW)、到达时间(TOA),而传输是靠LVDS总线传输,所以,告警处理板就存在串行码的解码问题。

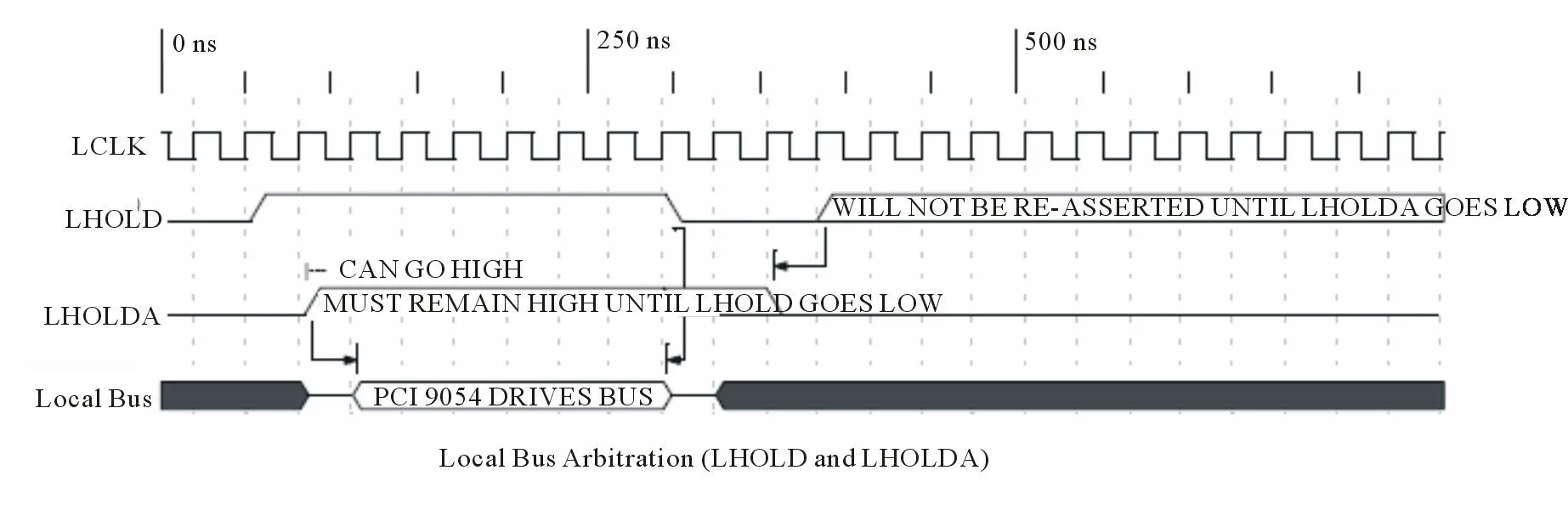

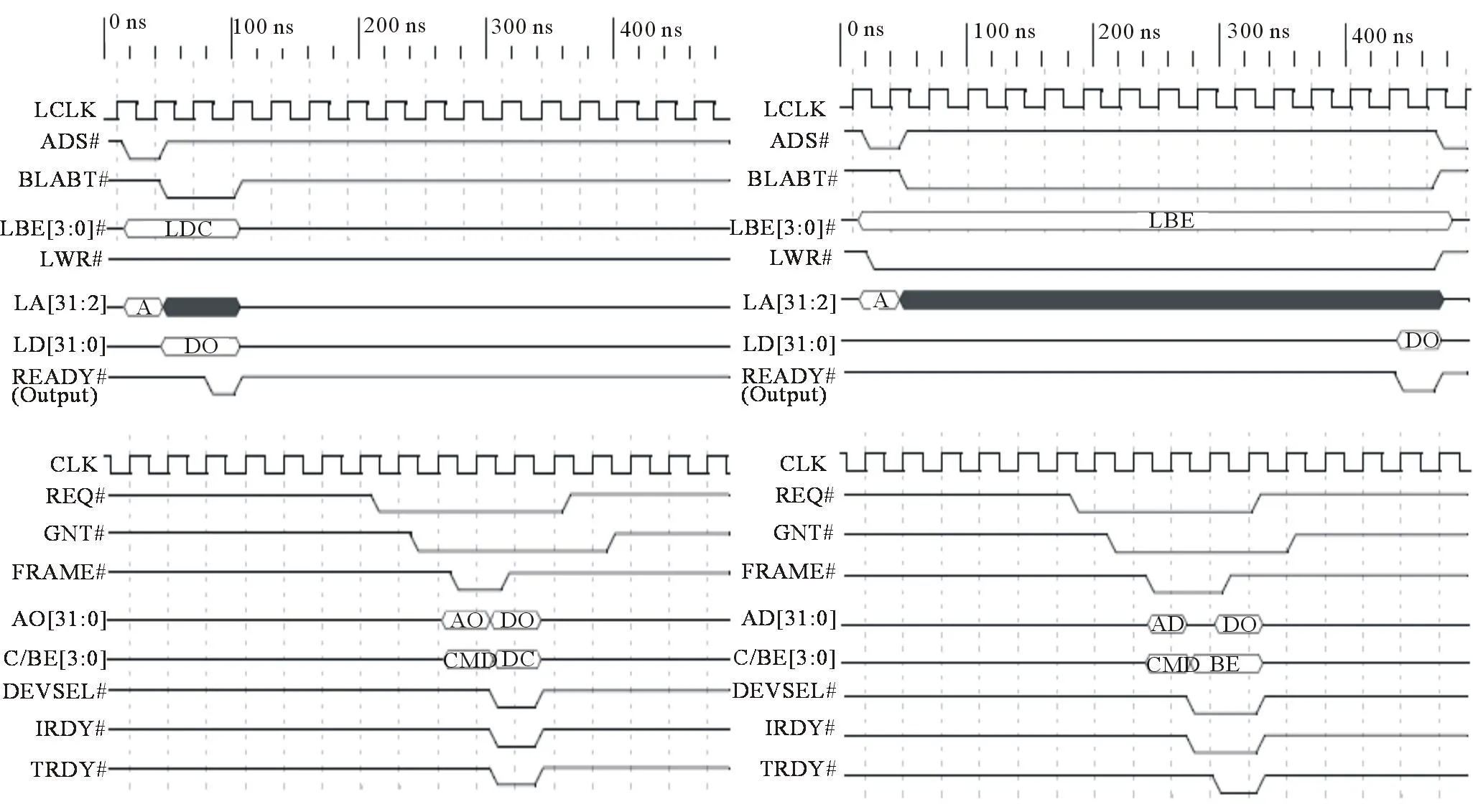

图4 9054握手时序图

2.2 PDW形成电路设计

将上述得到的RF、TOA、PW等各种信息,打包形成具有一定格式的PDW,最终送至DSP进行分选。为满足与DSP的通讯,PDW要重组成与DSP位宽一致的32 bit。

2.3 PCI接口电路设计

告警预处理板与主机通讯通过9054桥芯片实现,9054设计采用C模式,在FPGA中完成握手设计,握手时序如图4所示。

主设备突发数据读写设计中,主设备声明是否准备发送当前数据,在地址起始点使FRAME#有效,到主设备准备有效IRDY#,完成最后数据段。目标在数据段采样有效IRDY#和无效的FRAME#就知道是最后的数据段,直到目标TRDY#有效,数据段完成。9054突发数据传送时序如图5所示。

图5 9054突发数据传送时序

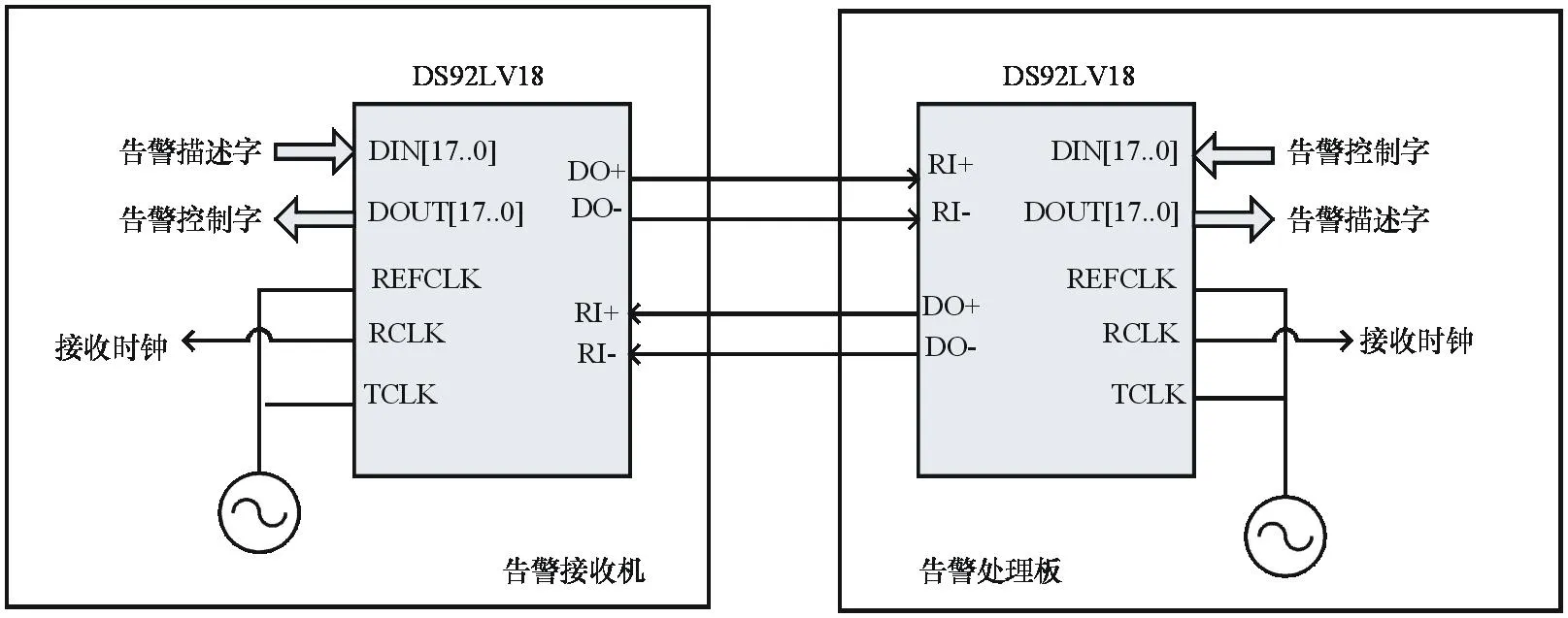

2.4 LVDS总线收发电路设计

告警接收机送至告警预处理模块的一个描述字有50位以上,同时还要接收侦察告警处理机的控制字,全部采用并行传输将增加很多电缆,因而使用串行传输LVDS,在终端进行调制或者解调,实现框图如图6所示。

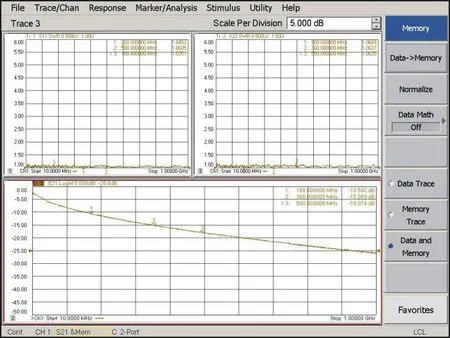

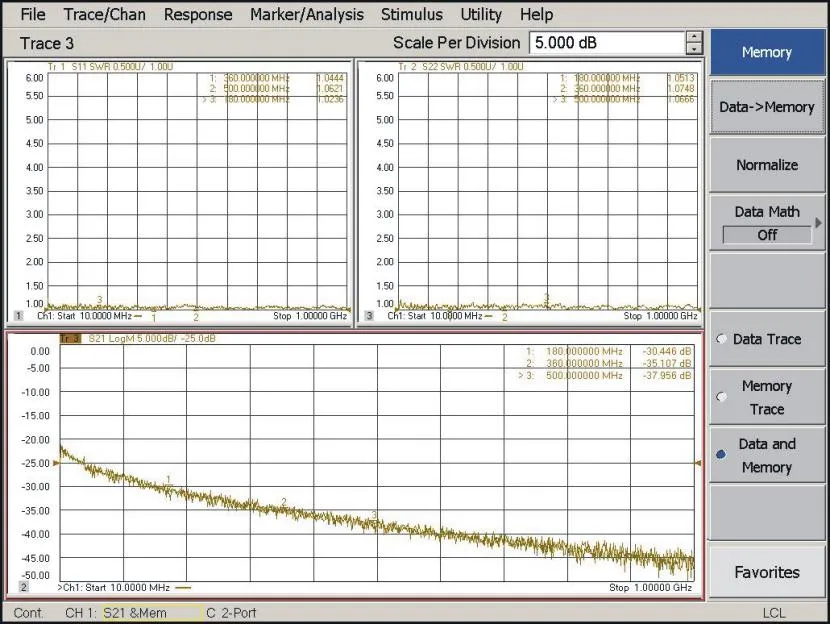

为摸清利用LVDS总线进行高速远距离传输的正确率,通过测试验证了数据传输中同轴电缆插损与通讯误码率的关系。图7、图8是同轴电缆加衰减器前后矢网波形图,30 m同轴电缆+衰减器的测试结果如表1所示。

通过以上测试可以看出,为保证传输数据质量,需保证以下要求:

(1) LVDS印制板单板电路端口与对应互联设备单板电路端口之间的电缆连接(包括焊接点、连接器、同轴线)的损耗应小于30 dB(@DC~360 MHz);

以告警描述字的收发为例,发送端告警接收机产生的描述字通过DS92LV18调制,通过DO+、DO-差分线传输,发送时钟为本地时钟TCLK;接收端侦察告警处理机接收DO-、DO+差分信号,由本地时钟REFCLK和串行数据产生接收时钟RCK,接收告警描述字,只要保证本地REFCLK与发送端TCLK偏差在5%以内即可正确接收。这样,告警接收机与侦察告警处理机间的数据交互用4根线即可完成。

图6 串行数据收发实现框图

序号测试电缆形式测试电缆@180MHz的插损值(dB)测试电缆@360MHz的插损值(dB)通讯误码率130m同轴电缆-10.502-15.0690230m同轴电缆+21dB衰减器-31.502-36.0690330m同轴电缆+23dB衰减器-33.502-38.0690.1‰430m同轴电缆+25dB衰减器-35.502-40.0693.6‰530m同轴电缆+28dB衰减器-38.502-42.06934.3‰630m同轴电缆+30dB衰减器-40.502-45.069170.7‰

图7 同轴电缆加衰减器前的矢网波形图

(2) LVDS印制板单板到设备输出端口、设备与设备之间的电缆互联应采用同轴连接器(同轴连接器的工作频率>360 MHz,特性阻抗=50 Ω),尽量避免采用开口线或低频连接器连接;

(3) LVDS印制板单板的电路设计应严格按照NS公司的芯片数据手册要求执行。

3结束语

基于CPCI架构的雷达告警处理板已经通过调试,并做了高低温、振动、温度冲击等环境试验,目前已交给用户使用,运行一切正常。下一步计划在FPGA片内资源的利用和系统时序控制上进行优化设计,进一步提高该板的性能。

图8 同轴电缆+20 dB衰减器后的矢网波形图

参考文献

[1]杨建,邓志清,高峰.基于FPGA的多功能雷达信号处理板硬件系统设计[J].舰船电子对抗,2011,34(6):52- 56.

[2]师庭伟.多功能激光告警信号处理技术研究[J].舰船电子对抗,2014,37(1):24-27.

[3]费元春,苏广川,米红,等.宽带雷达信号产生技术[M].北京:国防工业出版社,2002.

Design of Radar Warning Processing Board Based on CPCI Architecture

ZHOU Zhi-yong1,CHANG Yong2,MA Dan1

(1.The 51st Research Institute of CETC,Shanghai 201802,China;

2.Military Representative Office of Hangzhou,Hangzhou 314033,China)

Abstract:This paper introduces the radar warning processing board based on computer program configuration item architecture,expatiates the internal component,generation and extraction of pulse description word,transmitting and receiving circuit of low voltage differential signal bus & sequence of peripheral component interface.

Key words:radar warning;computer program configuration item;low voltage differential signal bus

收稿日期:2015-06-17

DOI:10.16426/j.cnki.jcdzdk.2015.05.022

中图分类号:TN957.51

文献标识码:A

文章编号:CN32-1413(2015)05-0099-04