可编程脉冲发生器的若干技术问题研究

2016-01-24蔡领朱金刚

蔡领++朱金刚

摘要:本文以一种SPLD器件为例,设计了一个周期和个数可控的脉冲发生系统。首先给出本设计的目标,并根据目标分析可行的各种方案,接着分四部分介绍了一种理想的实现方法,本文还首次提出了脉冲奇数分频中克服简单计数分频法无法实现50%占空比的新方法。最后对该系统进行测试并总结,它是目前较为实用的低成本高精度的可控脉冲发生系统,它同时也为处于相关教学一线的老师提供了一个实施案例。

关键词:电子技术;信号;SPLD;脉冲;奇数分频;占空比

中图分类号:TN7

文献标识码:A

DOI:10.3969/j.issn.1003-6970.2015.12.007

本文著录格式:蔡领,朱金刚.可编程脉冲发生器的若干技术问题研究[J].软件,2015,36(12):31-34

0 引言

可编程脉冲器在电子产品中应用广泛,目前大部分都是使用PLD(Programmable Logic Device)器件来实现,PLD器件通过编程可灵活方便地构建和修改数字电子系统。SPLD则是简单(Simple) PLD的意思,典型器件是Lattice公司生产的GAL16V8、GAL22VIO和Atmel公司生产的ATF16V8。SPLD器件使得电路设计段时间即可完成,且修改容易。早在20世纪90年代的数字电路实验的教学过程中就已经开始使用。许多文献中提到CPLD等大规模可编程逻辑器件将成为数字电路应用的大趋势,而作为联系模拟电路和各门技术课程的纽带的数字电路的设计中,SPLD双列直插封装更易用,开发环境要求低,成本低,在一些小规模设计中还是普遍使用。在高校教育中它更有助于学生理解和掌握技术,它使得设计难度大大降低,极大地吸引学生的注意力。分频电路和单脉冲电路等是电子技术中常用的模块,尤其是奇数分频中如何实现50%占空比的问题由来已久,本文将针对可编程脉冲发生器的设计目标,以对这些技术在SPLD上的实现为例展开探索。

1 系统概述

本设计以SPLD器件为例,制作一个多脉冲发生器,输出脉冲的个数和周期可预设置。电路框图如图l所示:

其中:

(1)输出脉冲周期可调。通过3路逻辑开关控制,分别为ImS、2mS、3mS、4mS...7mS。

(2)输出脉冲的数目可调。输出脉冲个数由3路逻辑开关控制,分别为1-7。

对于输出脉冲周期可调要求为1ms到7ms其实就是对周期为1ms的信号进行1到7分频;脉冲个数l到7个可编程实现一个3位的二进制计数器配合一些逻辑操作来完成。当然更多的脉冲个数和周期需要规模更大的PLD器件去实现。

2 系统设计与实现

2.1 脉冲信号源

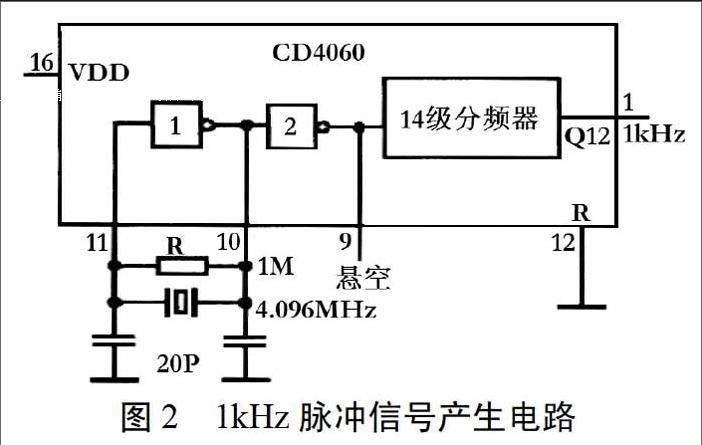

脉冲信号源可以用555定时器电路或品振产生,在进行数字电路设计时,多用几种方法进行设计可以培养分析和设计能力。如果考虑频率的稳定性,可选择晶振产生。具体实现为4.096MHz的晶振,结合CD4060产生lkHz的方波信号(周期为1ms),如图2所示。

2.2 输出脉冲周期控制电路

采用可编程分频电路来实现。

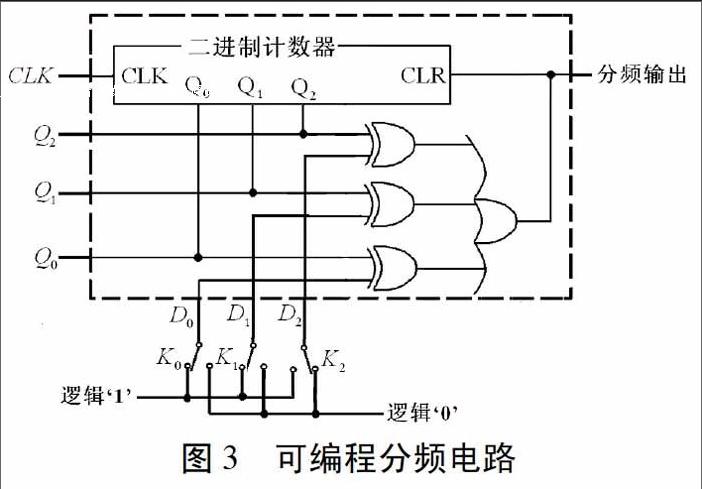

三位二进制计数器输出值为Q2Q1Q0,开关K0、K1、K2分别处于不同的状态(断开或闭合)时,产生相应的逻辑电平值(‘0或‘l),为D0-D7信号;Q2与D2,…,Q0与D0分别进行异或运算,当Q2与D2,…,Q0与D0都相等时CLR的状态为‘0,对计数器产生一次清‘0操作,计数器的最大值通过K0、K1、K2来设置。

这里简单比较下SPLD器件中22V1O和16V8这两类。22V1O的资源更为多些,但渐渐被复奈(Complex)PLD器件(CPLD)取代而面临淘汰,价格更是达到了20元左右一片,应用已经很少,16V8虽然资源相对少些,但是使用灵活,价格低,在简单数字电路设计中仍然发挥着举足轻重的作用。这里我们用廉价的16V8去实现单元逻辑电路。

在16V8的编程中,有几个地方需要注意。一是计数器无法实现1分频,即当输入设定为二进制001时通过计数器无法实现,需要用组合逻辑电路来实现。第二,16V8没有异步清零的功能,这样在计数时实际的计数周期要比设定的值多l,这可以用计数初值置为l的方法解决。

2.3 奇数分频对称波形实现的新方法

在分频数为3及以上的奇数时,简单的计数分频无法实现占空比50%,这是本设计的一个难点,也是由来已久的分频器里一个老问题。首先回顾下前辈们的方法,早在2004年,南开大学的高清运博士在他的一篇论文中提到了奇数分频器的设计,他提到可以分两步走:先对信号做N/2(带小数)分频(文中N都是指3以上的奇数),然后再做2分频。这种方法使用模(N+1)/2计数器进行计数,从0计数至(N-1)/2;将2分频器的输出反馈到输入待分频信号,在模(N+1)/2计数器计数至(N-I)/2时2分频器输出反向,同时使得原来输入待分频信号的上升沿计数变成下降沿计数。也就是说在2分频器输出由0变l或由l变0的外输入始终周期里,模(N+1)/2计数器的状态变化了2次,从而使计数循环减少了0.5个时钟,得到半整数输出。这种方法的电路实现相对节省资源,但是有些不容易理解;而后来提出的基于类扭环计数器的分频方法、各为上升沿计数和下降沿计数的双计数器输出相或法、先2倍频再整数分频法等,都将电路更加复杂化。

这里本文首次提出了一个新的节省资源且容易理解的方法:输入输出相与法。具体来说,N分频则用模N计数器,计数超过一半(N-1)/2和最大值N-1时电平反转,并在计数至一半时将输出波形与时钟信号进行逻辑与实现输出信号50%的占空比。下面以5分频为例。

图4清楚得展示了5分频时占空比控制的情况。其中“输入”即为待分频信号;“输出l”是指当模5计数器在计数至2和4后输出翻转的信号,显然这个信号还不是50%占空比;“输出2”即为最后的输出,占空比为50%。观察虚线部分可以发现,只要在计数值为2时将“输入”和“输出l”相与,而在其它计数值时保持原来的“输出l”,这样最后的“输出2”刚好就是50%占空比。按照这一简单的原理,本文基于16V8器件实现了3-7分频时占空比50%的要求,其中5分频输出测试结果图可见第4节的图8右半部分;对于更高奇数分频数,原理也是一样的,这里就不再详述。

2.4 脉冲数目的控制

图5表示了一个基于二进制减计数器的脉冲控制电路框图。二进制减计数器有两个工作状态:置数状态和计数状态,由逻辑控制脚RS R决定。当计数器的值从置入值减至0时,四输入或门输H{逻辑‘0,在时钟CLK的同步下,D触发器的输出为‘0,RS触发器的输出RS R为‘1,计数器执行“置数”功能,将由K0、K1、K2设定的逻辑状态D2D1D0置人计数器,但由于RS触发器的输出RS R必须由另一个输入端sinle_pulse_in来清‘0后,才能进入下一轮的计数周期,因此,sinle_pulse_in每出现一个负脉冲,就会触发一轮新的计数循环。开始计数时,RS R=0,停止计数时,RS R=l。将RS R通过一个非门倒相后接到一个与门的输入端,CLK接与门的另一个输入端,这样,当RS R=0时,与门就输出与CLK相同的脉冲,当RS R=l,与门就输出逻辑‘0。

2.5 单脉冲电路

上文已经提到,本系统中需要的单脉冲是一个负脉冲,即稳态时处于高电平,只当按键按下时出现一段低电平。由于机械按键在按下或松开时会发生机械抖动,会输出一系列的短脉冲波形,为了保证电路工作可靠,在用机械按键产生触发脉冲时,必须作去抖动处理。常用的按键防抖电路有同向缓冲器防抖电路,基于R—S触发器的防抖电路,基于电容充放电的防抖电路等。在本系统中,显然对于脉冲的宽度也有要求。详细来说,就是一次按键按下输出一串固定个数的脉冲,而在该串脉冲结束前,单脉冲输入端必须已经返回稳态(高电平),否则将继续引发下一串脉冲,因此,这里必须严格控制负脉冲的宽度。显然这里的脉冲宽度不能超出一个时钟周期,考虑16V8器件的D触发器资源,采用如图6所示的单脉冲产生电路。

因为单脉冲电路只用到2个D触发器,可以将这部分逻辑电路合并到输出脉冲数目控制的16V8芯片中。这里需要注意,由于单脉冲电路和输出脉冲数目控制电路共用一个时钟,所以输出脉冲数目控制电路右上方的D触发器应该去掉,否则输出脉冲个数将比设置值多l。

3 系统测试

本系统已经在万能板上焊接实验成功,用3个带锁按键用于控制调节周期;3个带锁按键用于调节输出脉冲个数;1个不带锁按键用来触发脉冲输出。

如图8所示,左边为周期设置成1ms、脉冲个数控制为l时的测试结果,可以看出,示波器显示为500us每格;右边为周期设置成5ms、脉冲个数控制为4个时的测试结果,其示波器显示5ms每格,且占空比为50%。

4 结论

本文以SPLD器件为例设计实现了一个可编程冲发生器,讨论了设计中的各个技术问题。对于更高分频数目和更多的脉冲个数的发生器,其原理是一样的,只需使用规模更大逻辑芯片即可。设计中奇数分频50%占空比的实现是本文最新提出的简单而有效的方法;单脉冲电路与脉冲输出个数控制电路进行了恰到好处的整合,可靠性高。同时本文设计思路清晰,可操作性强,可作为高校相关专业基础课堂教学的一个实施案例。