基于FPGA+DM36X的IP摄像机平台

2016-01-12李昂,陈文艺,杨辉等

基于FPGA+DM36X的IP摄像机平台

李昂1,陈文艺2,杨辉2,赵晓光1

(1.西安邮电大学 通信与信息工程学院,陕西 西安710061;2.西安邮电大学 物联网与两化融合研究院,陕西 西安710061)

摘要针对目前安防监控设备动态范围较低的问题,文中提出了基于FPGA和DM36X的高动态范围网络摄像机方案。该方案采用高动态图像传感器进行图像采集,并以FPGA和DM36X作为图像处理的核心。FPGA负责对高动态图像进行增强处理,弥补了DM36X对高动态图像处理的不足,并结合DM36X在视频图像编码及传输上的优势,最终实现1 280×720每秒30帧的高动态范围视频图像的采集、处理和传输。

关键词安防监空;FPGA;DM36X;高动态范围

收稿日期:2015-01-17

作者简介:李昂(1987—),男,硕士研究生。研究方向:嵌入式方向。E-mail:liang871210@sina.com。陈文艺(1964—),男,博士,教授,硕士生导师。研究方向:通信集成电路设计,视频图像实时处理及传输。

doi:10.16180/j.cnki.issn1007-7820.2015.09.038

中图分类号TP391.41

IP Camera Platform Based on FPGA+DM36X

LI Ang1,CHEN Wenyi2,YANG Hui2,ZHAO Xiaoguang1

(1.School of Communication and Information Engineering,Xi’an University of Posts and Telecommunications,

Xi’an 710061,China;2.Institute of Internet of Things and Integration of IT Application and Industrialization,

Xi’an University of Posts and Telecommunications,Xi’an 710061,China)

AbstractThis article proposes a program of IP camera platform based on FPGA+DM36X for a high dynamic range of security monitoring equipment.The program uses high dynamic image sensor for image acquisition with FPGA and DM36X as the core of image processing.FPGA is responsible for the high dynamic image enhancement processing,making up for the lack of DM36X in high-dynamic image processing.The advantage of DM36X in video encoding and transmission yields a high resolution of 1 280×720 at a transmission speed of 30 frames per second.

Keywordssecurity monitoring;FPGA;DM36X;high dynamic range

近年来,随着信息化技术以及物联网的发展,对于视频监控设备的要求不断的在提高,将高动态范围(High Dynamic Range,HDR)摄像机代替传统摄像机以提高监控质量成为了监控设备的发展趋势。TI公司达芬奇视频处理技术在网络摄像机视频监控方面的成功运用,使得DM36X芯片与其他芯片相比具有低功耗、小尺寸、低成本、高性能等特点[1]。但由于高动态摄像机的数据量非常大,同时对图像处理的要求也很高,这就增加了系统的复杂性。要同时满足高质量的视频图像处理效果和实时传输,单凭DM36X的处理能力已远不够,且DM36X内部的视频处理算法已固定,众多优秀的图像处理算法无法及时的添加进去,这也对DM36X图像处理能力的升级造成了一定的困难。而FPGA芯片处理速度快、灵活性高[2],可根据各种优秀算法进行较好的设计,所以系统选用FPGA进行前端HDR视频图像增强预处理部分,由此可在较大程度上减少DM36X的工作量,弥补其在高动态视频处理上的不足,使DM36X能完全发挥高速编码和传输效的特点,满足系统实时性要求。将FPGA和DM36X共同运用在网络摄像机平台中可充分发挥各自的优势。这种设计不仅使得系统在日后扩充和再次开发上提供了足够的灵活性,且有利于整个系统的升级与维护。

本系统是在TI公司基于达芬奇技术TMD320DM36X处理器的IP Camera方案基础之上搭建基于FPGA+DM36X的IP摄像机平台,采用高动态网络摄像机MT9M034进行图像采集,以FPGA+DM36X作为HDR视频图像增强、编码和传输处理核心,最终完成用户通过远程PC机客户端上观看1 280×720分辨率,每秒30帧的实时视频。

1总体方案

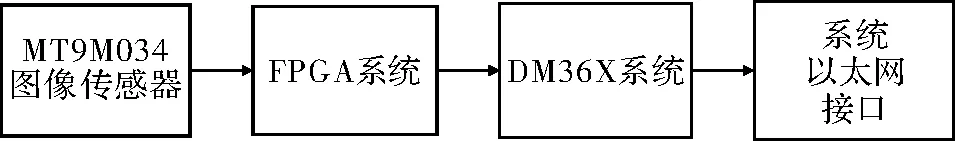

系统架构如图1所示,MT9M034采集HDR视频信号,FPGA负责对HDR视频图像进行增强处理,DM36X负责对增强后的HDR图像进行编码传输等处理。

图1 系统架构

系统3部分之间的数据流如图2所示。

图2 系统数据流

图像传感器MT9M034经过配置后输出动态范围为120 dB的HDR图像。图像数据的位宽是20 bit,可选择性的压缩成12 bit或14 bit。由于DM36X处理能力的限制,在本系统中将传感器输出数据位宽设置为12 bit,这就会造成图像数据的损失。所以本方案在原IP Camera的基础之上添加了FPGA系统,可根据需要灵活增加底层的图像处理算法。首先图像传感器输出的视频数据在FPGA上进行捕获和对数压缩等处理,达到对图像增强的效果。然后再将这12位裸数据传输给DM36X系统,并在DM36X系统中完成色彩空间转换、伽马校正、RGB转YUV、边缘增强等一系列处理[3]。最终将处理过的视频图像数据以H.264标准压缩后通过以太网接口传送到TCP/IP网络,完成用户通过远程PC机客户端上实时监控视频[4]。

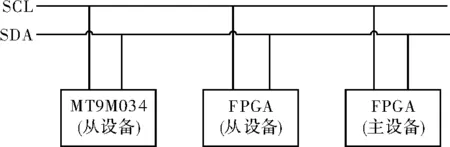

MT9M034(从设备)、FPGA(从设备)、DM36X(主设备)之间通过I2C总线进行通信。DM36X作为主设备不仅可通过I2C总线对MT9M034进行配置,还可对FPGA进行简单控制,如图3所示。

图3 I 2C控制

原DM36X IPNC的驱动程序是针对MT9T031传感器设计的。而本系统中采用的图像传感器是MT9M034。MT9M034和MT9T031虽均是美光公司推出的图像传感器,寄存器位宽均为16 bit,但其寄存器编址位宽是有差别的,MT9T031传感器的寄存器编址是8 bit,而MT9M034传感器的寄存器编址是16 bit[5]。为了使DM36X能对MT9M034传感器进行配置,需要对DM36X的驱动进行移植。

2FPGA硬件电路设计

如图4所示,在FPGA 上需要设计的电路包括图像捕获电路、数据校正电路、RAW转亮度电路、CLAHE色调映射电路和用于调试图像传感器的VGA显示电路。

图4 FPGA系统架构

DM36X将MT9M034配置好并启动后,图像传感器会输出12 bit的HDR图像数据,这些数据直接进入图像捕获电路模块,此模块主要是对数据进行标记和对行、列、帧等进行计算,为后面的电路设计提供必要的参数。MT9M034图像传感器通过分段性覆盖整个亮度域的3次曝光合成一副20 bit位宽的HDR图像,并将20 bit亮度分三段折线模拟对数压缩到12 bit输出,增加了传感器的实时性。因为普通的显示器只能显示8 bit数据,所以需要色调映射算法将HDR图像压缩成8 bit低动态范围图像(Low Dynamic Range Image,HDRI)这样既可保持图像整体明暗效果,又可使图像的细节部分很好的体现出来[6]。由于传感器内部的三段线性压缩和标准的对数压缩曲线之间具有一定的差距,会使原HDR图像损失许多的细节信息,若直接进行色调映射算法的处理的话会影响图像的对比度,所以在进行色调映射之前需要进行对数据进行校正,最大程度上消除传感器三段线性压缩造成的误差[7],然后在进行对数压缩这样就可将整个图像的亮度压缩到一个较小的范围内,最后在通过色调映射算法实现图像效果的增强。由于时间原因在FPGA中仅实现图像的抓取电路,通过Nios2图像抓取电路向PC机中存入一帧图像用于图像效果的调试,其中抓取的图像每个像素位宽是12 bit裸数据,在Matlab中进行显示,如图5所示。

图5 抓取的一帧图像

3MT9M034驱动移植

3.1 传感器特性

MT9M034传感器是美光公司推出应用于安防领域的高动态范围图像传感器。该传感器具有全局运动补偿功能,最高可提供每秒45帧下1 280×960分辨率的视频拍摄,支持线性模式和高动态范围模式。传感器具有并行和串行差分两种数据输出接口。并行接口数据速率低,概念简单,便于实现,在本系统中采用并行接口,在后续开发中为了提高速度可考虑采用差分串行接口。

3.2 DM36X的I 2C驱动移植

I2C(Inter-Integrated Circuit)总线是由Philips公司开发的一种同步串行总线协议,其是一种多向控制线,可让多个芯片连接到同一总线结构上共同实施数据传输[8]。DM36X的I2C驱动架构如图6所示。

图6 I 2C驱动架构

首先应用程序drv_i2c.c根据不同传感器的参数,将寄存器个数、寄存器地址位数寄存器值位数等配置信息存储在I2C_TransferPrm结构中,其次通过I2C_IOCTL_CMD_MAKE()函数将这些具体的寄存器信息生成相应的命令。这些命令由ioctl()函数传递给内核空间中的设备驱动dev_i2c.c,在设备驱动程序中I2C_devIoctl()函数对将对命令进行解析,根据不同的命令进行不同的操作,这里较为重要的两个命令是:(1)I2C_CMD_SET_DEV_ADDR,设置设备地址;(2)I2C_CMD_WRITE将用户空间的配置信息复制到内核空间,并存储在I2C_TransferPrm结构中。最终通过I2C_write()、I2C_read()函数调用I2C_transfer()将数据发出。在I2C_write()、I2C_read()中都是以I2C_msg作为传输单元的。

struct I2C_msg {

_u16 addr;从设备地址

_u16 flags;标志位,区分读写等

_u16 len;消息单元长度

_u8 *buf;数据缓存,存储发送数据或者接收数据。

};

I2C_write()、I2C_read()函数的主要工作就是设置I2C_msg,将寄存器地址(regAddr)和寄存器值(regValue)写入I2C_msg的数据缓存buf中,并调用I2C_transfer进行数据传输,达到对传感器寄存器配置的目的。

根据以上分析可知,将I2C驱动移植到MT9M034上,只需修改应用程序drv_i2c.c和设备驱动程序dev_i2c.c即可,I2C-core及以下部分的内容属于内核部分,其接口都是统一针对Davinci平台下的,故无需进行分析和修改。由于MT9M034的寄存器是16 bit编址,故需增加16 bit寄存器读写函数DRV_i2cWrite16()、DRV_i2cRead16()。另外在I2C_TransferPrm结构中增加16 bit寄存器地址指针;而且为了方便区分16 bit寄存器和8 bit寄存器,增加寄存器大小成员regSize。

typedef struct {

unsigned char dataSize;

unsigned char count;

unsigned char *reg;

unsigned short *reg16;

unsigned char regSize;

void *value;配置的寄存器值,16 bit或8 bit

} I2C_TransferPrm;

在drv_i2c.c中增加I2C_write16()、I2C_read16()函数,这两个函数与I2C_write()、I2C_read()相似。只是在I2C_msg的数据缓存中存入regAddr[15:8]、regAddr[7:0]、regValue[15:8]、regValue[7:0],使I2C可读写16位数据。通过以上修改,I2C的驱动程序移植完成。

3.3 DM36X前端的驱动移植

I2C驱动移植完成后仅可使DM36X对图像传感器进行配置工作,为使DM36X成功接收来自传感器的视频数据,还需要对DM36X的视频处理前端(Video Processing Front End,VPFE)驱动进行相应的修改来添加新的传感器驱动程序。DM36X的DVSDK中已对VPFE驱动做了多次封装,将与图像传感器相关的代码隔离到了用户区,这样方便用户对源程序进行修改和移植,并根据不同的需要来添加已知型号的CMOS图像传感器驱动。通过对VPFE源程序的修改实现两个功能,一方面根据视频图像的分辨率和帧率等信息向DM36X驱动提供寄存器的配置信息,另一方面为MT9M034传感器提供以I2C为接口的控制和配置功能。

4测试结果

确保硬件电路连接正确并上电后,将编译好的程序下载到DM36X中启动,打开远程PC机终端开启网页客户端或者VLC播放器输入用户名和密码,可显示1 280×720分辨率每秒30帧的视频图像,说明DM36X的驱动移植正确,并通过I2C总线将传感器配置成功。本系统的测试结果如图7所示,从图中可观察到在室内和室外光照强度相差较大的情况下,室内暗处和室外亮处的景物均可被观察到,具有较高的动态范围,保留了场景中绝大部分的细节,充分体现了本IP Camera的优势。

图7 测试结果

5结束语

在安防领域,对于视频监控设备的要求不断的提高,本文是基于FPGA和DM36X联合硬件平台开发的一款高动态范围网络监控摄像机,通过对DM36X视频前端驱动的分析和移植,已完成DM36X对整个平台的控制工作,并实现1 280×720分辨率每秒30帧的实时播放。较传统的网络摄像机可更好地应对复杂光照场景,从而拍摄出较高动态范围的视频影像,使场景中更多的细节可被观察到,对于提高安防监控能力有着重要的意义。由于图像传感器输出的数据是由20 bit压缩到12 bit的,造成图像数据有一定的损失,对比度较低,为了弥补这些不足,在系统中添加了FPGA系统,由于时间关系FPGA部分只完成图像抓取电路的设计,后续的开发中将重点对其他模块进行硬件实现,完善整个图像采集处理系统。

参考文献

[1]马洪蕊,蒋心晓,刘邵南.嵌入式视频应用系统设计与实现[M].北京:北京航空航天大学出版社,2011.

[2]王丹琦,吴毅,甘晓炫.基于FPGA的高速数据采集系统设计[J].电子设计工程,2014,22(21):153-158.

[3]Texas Instruments.Video processing front end(VPFE)[M].Tex,USA:Texas Instruments,2007.

[4]王雅,陈文艺,叶欣.基于DM365的嵌入式监控平台研究[J].保密科学与技术,2013(2):33-38.

[5]Aptina Corporation.1/3-inch CMOS digital image sensor MT9M034 data sheet[M].San Jose,CA:Aptina Corporation,2011.

[6]Boschetti A,Adami N,Leonardi R.High dynamic range image tone mapping based on local histogram equalization[C].Mosico:ICME,2010:1130-1135.

[7]郭少宸,陈文艺.图像传感器MT9M034输出图像数据的校正[J].电子科技,2014,27(9):54-61.

[8]朱南皓,李正祥.嵌入式Linux中I2C设备驱动程序的研究与实现[J].微计算机信息,2010(11):67-69.