基于FPGA的分布式干扰机实现

2016-01-12焦龙飞,莫子军

基于FPGA的分布式干扰机实现

焦龙飞,莫子军

(西安电子科技大学 电子工程学院,陕西 西安710071)

摘要为了有效对抗预警机、新型雷达网、通信网以及导航系统,在现代电子对抗中普遍使用分布式干扰技术。文中分析了分布式干扰的基本原理,并以FPGA为平台实现分布式干扰机的研制。分布式干扰机以DRFM为核心,使用FPGA内部FIFO完成假目标的转发与延时,实现了对雷达的分布式协同相干、非相干干扰。

关键词分布式干扰机;FPGA;DRFM

收稿日期:2014-11-22

作者简介:焦龙飞(1988—),男,硕士研究生。研究方向:FPGA嵌入式,电子对抗。E-mail:690061539@qq.com

doi:10.16180/j.cnki.issn1007-7820.2015.09.024

中图分类号TN972

Realization of Distributed Jammer Based on FPGA

JIAO Longfei,MO Zijun

(School of Electronic Engineering,Xidian University,Xi’an 710071,China)

AbstractThe distributed jamming technology is widely used in modern electronic countermeasure to effectively counter the awacs,new types of radar networks,communication networks and navigation systems.This paper analyzes the basic principle of distributed jamming,and realizes the distributed jammer based on FPGA.With the core of DRFM,distributed jamming uses FPGA’s FIFO for the false target transmission and time delay,realizing the distributed collaborative coherent and noncoherent jamming of radar.

Keywordsdistributed jammer;FPGA;DRFM

分布式干扰机被国内外专家认为是对付组网雷达的一种行之有效的方法。相对于独立工作的雷达干扰系统,分布式干扰机对组网雷达的对抗优势不仅体现在干扰效果方面,且在对组网雷达中各个辐射源的侦察定位方面同样优势明显。

电子战装备为了适应未来的战场密集、复杂多变的电磁环境,并对感兴趣的电子战兵器进行侦查、测向、干扰、反辐射摧毁,必须具备频带宽、对象广、技术新、变化快的技术特点。电子战是一个动态变化的作战领域,只要存在战争,对抗与反对抗就不会完结。根据不断变化的电子战作战对象和作战环境,研究一些适应未来高技术战争的新技术和新装备。分布式干扰具有一系列新特点,是一种“面对面”的干扰,即众多空间分布的干扰机群可压制较大空域内的雷达、通信台或导航接收机,因此在未来信息化战场上,分布式干扰是对抗预警机、分布式雷达网、通信网和导航网的有力手段[1]。

分布式干扰机是在气球载干扰机和无人机机载干扰机等形式发展起来的一种电子对抗设备。其可受控或自动地对敌方的电子设备进行干扰。在特定区域内,其既可产生虚假的进攻态势也可掩护目标。分布式干扰既可为群目标进行掩护干扰,也可用来进行自卫干扰[2]。

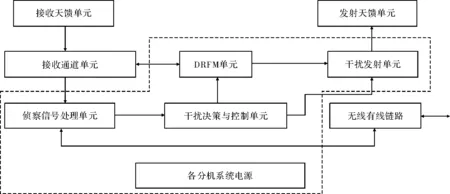

本文研制的分布式干扰机由两套干扰机构成,实现对雷达的分布式协同相干、非相干干扰。两套干扰机在软硬件上均采用相同的设计,其组成结构如图1所示。

1分布式干扰机的基本原理

1.1 干扰样式原理分析

分布式干扰机原理样机由两套干扰机构成,实现对雷达的分布式协同相干、非相干干扰,以实现对对雷达的角度欺骗干扰。两种干扰样式是以雷达天线的信号是否具有稳定的相位关系来区分的[3]。

(1)非相干干扰。两天线接收干扰源信号

(1)

图1 分布式干扰机系统组成

经和差处理后

(2)

经混频、中放(包括AGC控制),再经相位检波、误差积分后的输出角度误差信号

(3)

经天线方向图近似为

(4)

跟踪天线的指向角

(5)

(2)相干干扰。两干扰源在雷达天线有稳定相位

(6)

经和差处理后

(7)

经混频、中放(包括AGC控制),再经过相位检波、误差积分后的输出角度误差信号

(8)

其中

(9)

经天线方向图近似为

(10)

跟踪天线的指向角为

(11)

1.2 单机干扰机工作原理

接收天馈单元收到的信号经过接收通道单元进行时分隔离、低噪声放大、带通滤波、检波和对数视频放大(DLVA)、门限检测,形成各自的检测输出、视频包络输出和中/射频输出,供给数字射频存储(DRFM)单元和侦察信号处理单元。

侦察信号处理单元测量各波段检测信号的到达时间(TOA)、脉宽(PW),采集中频信号的波形,接收信号的分选、辐射源检测、威胁判决,将结果提交干扰决策与控制单元和无线数据链路。由于干扰带宽较窄,信号处理单元、DRFM单元和干扰决策单元均在同一块电路中完成。DRFM单元执行干扰决策与控制单元发来的控制命令和设置参数,完成对输入射频或中频信号的采样、存储、读出和干扰调制,将低功率的中频干扰信号交付干扰发射单元[4]。

干扰发射单元完成干扰信号中频到射频的变频和功率放大,通过干扰发射天线辐射输出。无线数据链路完成干扰样机与其他设备的双向数据交互,接收上位机干扰样式和干扰参数设置,回传侦察处理结果和干扰机工作状态。

上下变频的本振由外部信号源产生,系统频综采用分布式设计方式,由温补晶振产生高稳定基准信号,各分机系统由锁相、倍频等电路产生不同频率的信号[5]。

1.3 分布式干扰模式

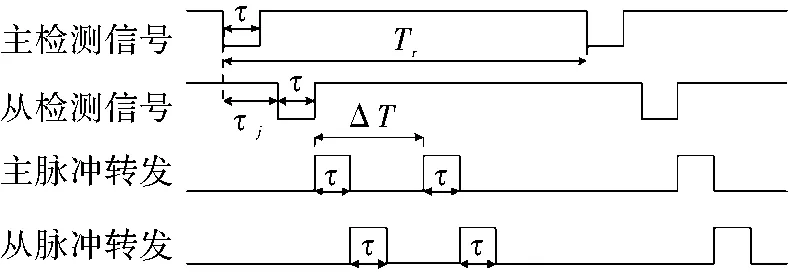

本组分布式干扰机采用收发分时全脉冲转发干扰方式。其中干扰时间Tj,附加初始迟延τj,重复周期Tr,脉冲周期τ,假目标间隔ΔT。

收发分时全脉冲转发包括同步和异步两种模式,同步与异步指主装置和从装置干扰信号到达雷达先后顺序的相关性。同步方式指二者干扰信号雷达的时间有确定的先后关系,偶闪烁同时有无,奇闪烁同一时刻仅有一部装置的干扰信号到达雷达。异步方式时不控制二者的到达时间[6]。

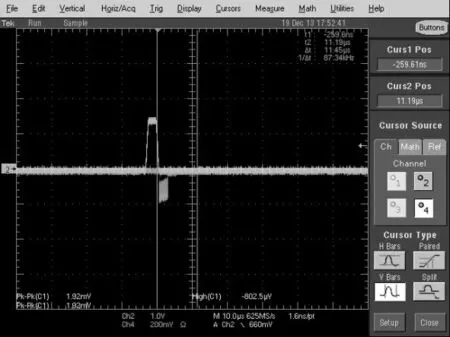

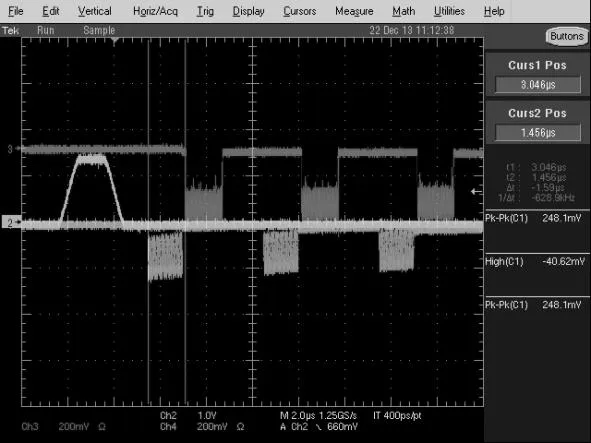

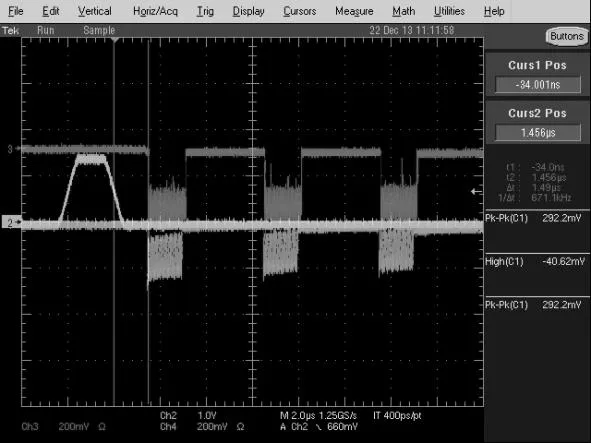

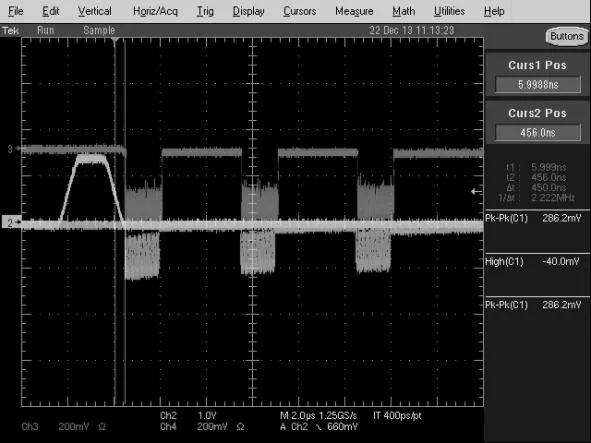

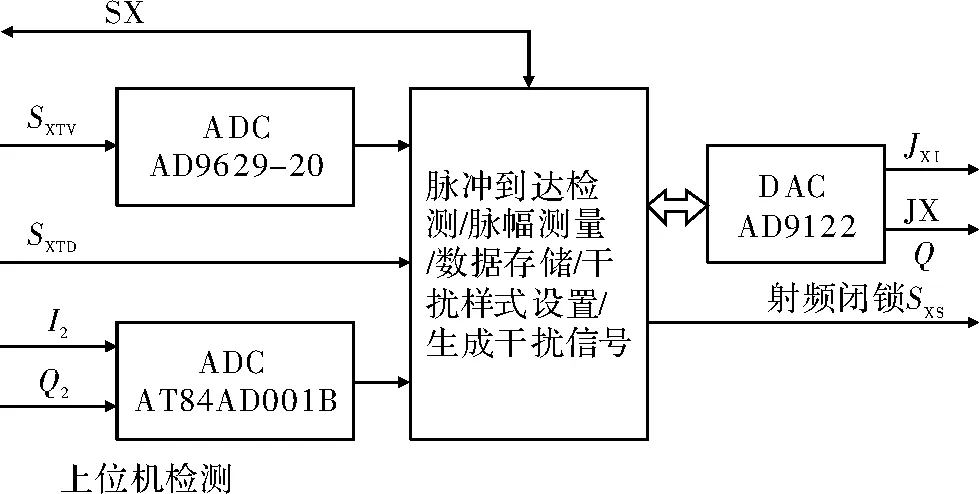

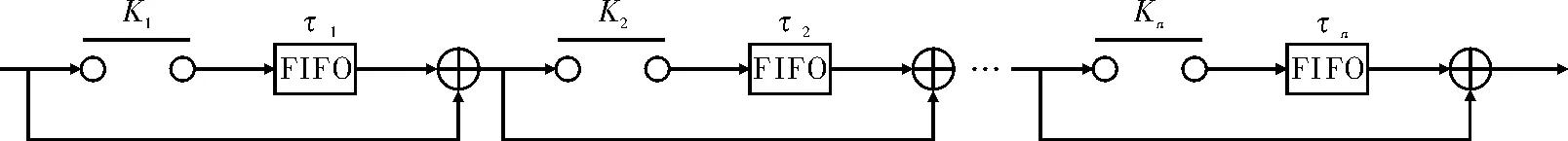

收发分时全脉冲同步转发的使用条件是干扰机不满足收发同时的隔离度要求,但允许干扰机延迟至少一个雷达脉冲宽度的时间再开始发射干扰信号。在检测信号SXTD有效期间,将波形采样数据写入存储器,从SXTD后沿迟延τj后开始发射干扰。脉冲之间的间隔和数量根据ΔT的计算设定。在一般情况下,τ+Tj=(0.8~0.9)Tr,即每收到一个SXTD信号,进行一次全脉冲存储转发干扰,迟延时间与干扰时间的和总 同步奇闪烁模式下,主装置在雷达脉冲结束加上附加迟延开始转发干扰,从装置在考虑附加迟延后再延迟一个脉冲宽度开始干扰。 图2 全脉冲分时转发干扰同步奇闪烁 同步偶闪烁模式下,主从装置在考虑附加迟延后同时开始干扰。 图3 全脉冲分时转发干扰同步偶闪烁 收发分时全脉冲异步转发模式下,主从装置在各自脉冲后沿到达时分别开始干扰,两者无相干性。 图4 全脉冲分时转发干扰异步随机假目标 2分布式干扰机在FPGA中的实现 DRFM单元根据干扰决策与控制单元发来的指令和参数,完成对信号的采样、存储、延时和转发,其组成部分如图5所示。 图5 DRFM组成结构 通过DRFM可实现假目标间隔时间、个数及干扰方式。在FPGA中可以级联FIFO来实现这种延迟叠加单元的结构,设每一级的延迟时间对应每一级FIFO的深度,每一级的开关控制由控制模块解析的命令决定。DRFM中存储延时及转发部分的结构图如图6所示。 图6 DRFM中存储转发延时单元结构图 如图6所示,当前FIFO的输入为前一级单元的输出,当前FIFO的输出叠加上前一级单元的输出,作为当前单元的输出。当DRFM工作时,在时钟的控制下,雷达信号从存储单元中进入第一级FIFO中。与此同时,第一级FIFO的输出与雷达信号叠加送入下一级FIFO。在FIFO未满时输出0,写满后输出数据,如此经过k级的FIFO缓存后,则最多输出k个假目标。假目标输出个数由Kn个开关电路控制,根据干扰决策控制单元的指令,依次打开或关闭开关,借此达到对假目标输出个数的控制。假目标时间间隔由控制FIFO的读写时钟控制,根据干扰决策控制单元的指令,读写时钟分别延时相应的时间,由此达到对延时的控制[7]。 干扰决策与控制单元由两部分构成,分别为ARM通信模块和指令解析模块。ARM通信模块通过SPI接收ARM发送的设置及控制命令,同时将ARM需读取的信息发送给ARM,如此则可由ARM端的触摸面板完成对整个干扰机的控制,从而实现人机交互[8]。指令解析模块则是读取ARM发送过来的指令和参数,根据预先约定好的协议,进行指令解析,将解析后的指令和参数分别发送给DRFM模块,从而实现对DRFM的设置和控制。 由于分布式干扰机由两套软硬件完全相同的干扰机组成,所以无线链路模块完成两套干扰机之间的信息交互。两套干扰机可分别被设置为主设备和从设备,但同一时间只能有一套干扰机为主设备,此时另一套则为从设备。当两套干扰机同时为从设备时,无线链路模块不进行数据交互,两套干扰机独立工作,互不影响。当一套干扰机为主设备,另一套干扰机为从设备时,主设备可将自身的配置及参数,通过无线链路发送给从设备,完成对从设备的配置及控制;同时从设备也可独立的设置自身的工作模式及参数。这种自由性较高的配置方式可实现多种模式的分布式干扰,在实际使用中具有重要意义[9]。 3仿真结果及对比 对分布式干扰机产生机理的仿真结果分析可知,通过改变假目标数量和改变干扰模式来产生假目标,可以对雷达目标进行干扰。 (1)假目标数量验证。 由图7和图8可知,在触发脉冲沿到来之后,干扰机可产生1~10之间任意个数的假目标。当产生多个假目标时,假目标间隔相同并可调。结合主从两台干扰机,形成分布式多数量干扰。 图7 假目标为1的仿真对比结果 图8 假目标为10的仿真对比结果 (2)全脉冲分时转发同步奇闪烁干扰。 在同步奇闪烁模式中可以看到,当脉冲触发信号沿到达之后,主干扰假目标在延迟一个附加迟延后才开始转发第一个假目标;而从干扰假目标在延迟一个附加迟延后,再延迟一个信号脉冲宽度,然后才开始转发。由图中可看到,主从干扰信号在同一时间只有一个假目标产生,完全符合理论分析。 图9 全脉冲分时转发干扰同步奇闪烁波形图 (3)全脉冲分时转发同步偶闪烁干扰。 信号描述如图9中表示方法,则从图10中可看出,在同步偶闪烁模式下,主从干扰机在脉冲信号沿到达之后,均延迟一个附加迟延之后,同时开始假目标的产生,两者完全统一。图10中主从干扰假目标同时产生与结束,符合理论分析的结果。 图10 全脉冲分时转发干扰同步偶闪烁波形图 (4)全脉冲分时转发异步干扰。 从图11中可看出,在异步干扰模式下,主从干扰机在脉冲信号沿到达之后,无需考虑附加延迟时间,各自立即开始转发假目标,符合理论分析的结果。 图11 全脉冲分时转发异步干扰波形图 4结束语 本文通过对分布式干扰机的理论分析与仿真结果对比,从实际角度验证了分布式干扰机的可行性。针对分布式干扰机的原理进行了详细介绍,对分布式干扰模式做了深入探讨。仿真结果的分析及对比,验证了分布式干扰机设计的正确性。 参考文献 [1]赵国庆.雷达对抗原理[M].西安:西安电子科技大学出版社,1999. [2]田波,张永顺.发展中的分布式干扰技术[J].航天电子对抗,2004,1(1):41-43. [3]高军辉.分布式干扰技术研究[D].成都:电子科技大学,2006. [4]支双双,刘聪峰,朱云鹏,等.分布式干扰下雷达探测区计算与仿真[J].中国电子科学研究所学报,2012,2(1):63-66. [5]SUN Guoying,LI Yunjie,GAO Meiguo.An improved DRFM system based on digital dhannelized receiver[C].Dalian:2nd International Congress of Image and Signal Processing,2009:1-5. [6]张薇,马建峰,杨晓元.分布式存储系统的可靠性研究[J].西安电子科技大学学报:自然科学版,2009,36(3):48l-485. [7]李勇.数字射频存储技术及其应用研究[D].武汉:武汉理工大学,2007. [8]潘松,黄继业.EDA技术与VHDL[M].3版.北京:清华大学出版社,2009. [9]Altera.Stratix II Device Handbook[M].Texa,USA:Altera Conperation,2013.

2.1 DRFM在FPGA中的实现

2.2 干扰决策与控制单元

2.3 无线链路模块