NoC边界扫描测试系统硬件设计

2016-01-12全钊锋

NoC边界扫描测试系统硬件设计

全钊锋

(桂林电子科技大学 电子工程与自动化学院,广西 桂林541004)

摘要为了解决内部结构日益复杂的片上网络系统故障测试的问题,在研究3×3 2D-Mesh体系结构的NoC系统、边界扫描测试技术和资源节点故障类型的基础上,以FPGA为核心器件设计边界扫描测试系统。完成了数据采集、频率计、放大器、SRAM、IEEE1500 Wrapper等资源节点电路以及资源节点边界扫描链路的接口电路设计,并利用测试软件、信号发生器、万用表和数字示波器,通过边界扫描链路完成对整个硬件设计的测试。测试结果表明该设计性能稳定,为研究NoC系统的边界扫描测试技术提供了硬件平台。

关键词片上网络;FPGA;边界扫描;硬件平台

收稿日期:2015-03-09

作者简介:全钊锋(1987—),男,硕士研究生。研究方向:集成电路设计。E-mail:602345825@qq.com

doi:10.16180/j.cnki.issn1007-7820.2015.09.017

中图分类号TN47

Hardware Design of NoC Boundary Scan Test System

QUAN Zhaofeng

(School of Electronic Engineering and Automatic,Guilin University of Electronic Technology,Guilin 541004,China)

AbstractA boundary scan test system is designed with FPGA as the core for fault testing of complex network on chip systems based on 3×3 2D-Mesh structure of NoC system,the boundary scan test technology and the resource node fault types.The frequency meter,amplifier,SRAM,IEEE1500 Wrapper and the boundary scanning chains of resource nodes interface are implemented.The test software,signal generator,AVO meter,digital oscilloscope are used to checkout the whole hardware design through boundary chain.The test results show that the design offers stable performance and provides a hardware platform of boundary scan test in the research of NoC systems.

Keywordsnetwork on chip;FPGA;boundary scan;hardware platform

片上网络(Network-on-Chip,NoC)是专门用于芯片内部互连的通信网络,它借鉴了计算机网络中分组交换的通信方法,可以根据应用灵活地采用多种网络拓扑结构互连片上系统或者IP核[1]。随着集成技术的发展,越来越高的集成芯片密集程度使得外部可接触的测试引脚越来越少,NoC测试的难度越来越大,甚至测试的成本比设计系统本身还高。

NoC系统的测试可以分为IP核测试和NoC通信框架的测试,后者则又可以分为路由器和链路的测试[2]。目前在NoC测试方面已经开展了很多研究:文献[2]提出复用NoC传输测试数据的并行内建自(Build-In Self Test,BIST)测试结构,使用路由设置分组实现路由工作模式和测试模式之间的切换并对路由表进行设置,给被测的FIFOs提供了可靠的测试数据传输服务;文献[3]在NoC结构下采用异构IP核的并行测试方法,在测试数据传输的并行性和测试应用的并行性两方面提高NoC测试效率;文献[4]提出基于BIST测试的方法测试NoC路由器内部交换开关的互连线串扰故障;文献[5]在不影响FPGA应用区域的前提下,研究NoC的硬连线作为访问机制的在线测试方法,并对此进行了相关的实验。利用BIST方法测试NoC居多,而应用边界扫描(Boundary Scan)技术测试NoC系统的颇少。边界扫描的主要思想是将边界扫描结构置于器件的每个管脚与内部逻辑之间,通过这些边界扫描单元来控制和观测输入输出管脚的信号值[6]。

为检测NoC系统中资源节点和通信架构的故障,本系统设计基于FPGA的NoC边界扫描测试硬件系统,针对3×3的2D-Mesh网络拓扑结构完成数据采集、频率计、放大器、SRAM、IEEE1500 Wrapper等资源节点电路设计,并且添加边界扫描单元设计NoC边界扫描链路,为研究和实现NoC边讲解扫描技术提供了硬件平台。

1NoC系统

NoC系统由两种基本单元组成:负责处理的资源节点和负责通信的路由节点[7]。图3是NoC系统规则的3×3 2D-Mesh拓扑结构,该结构中主要由9个路由节点,9个资源节点,9个资源网络接口以及若干网络传输线组成。可见,路由节点不但通过资源网络接口与资源节点相连,而且还和与之相连的4个路由节点相连。本文以FPGA为载体,利用Verilog语言设计路由节点,通过例化迅速构造该拓扑结构的路由节点,而且FPGA的可再编程使得改变结构较为简单,对于不便在FPGA内部设计的资源节点,FPGA丰富的I/O资源可满足设计要求。NoC系统故障主要出现在通信架构和资源节点两方面。通信架构故障主要包括链路和路由节点等方面的故障。链路故障主要有固定性故障(SAF)、桥接故障等类型[8]。

图1 基于2D-Mesh的3×3 NoC系统结构模型

2NoC边界扫描测试系统电路设计

2.1 NoC系统硬件设计

由于NoC边界扫描测试系统电路是在NoC系统硬件的基础上添加边界扫描链设计而成的,因此首先需要设计NoC系统的硬件电路。如图2所示,NoC系统的硬件结构主要包括核心器件FPGA和9个资源节点电路。核心器件选用EP4CE115F29C7型号的FPGA,该器件具有115KLE,432个M9K存储块,4个锁相环,20个全局同步时钟网络,780管脚的BGA封装内提供528个用户I/O端口;9个资源节点电路设计如下:(1)SRAM资源节点。(2)数字I/O资源节点。(3)频率计资源节点。(4)8通道数据采集卡。(5)小信号模拟放大器资源节点。(6)全加器资源节点。(7)设计通信口资源节点。(8)支持IEEE1500测试标准的IP核。(9)以内嵌有1149.1标准的边界扫描单元的8路D触发器电路资源节点。

图2 NoC硬件结构

2.2 NoC系统边界扫描链路设计

边界扫描硬件单元主要由测试存取通道、TAP控制器、指令寄存器(IR)和测试数据寄存器(TDR)4部分组成[9]。测试数据输入(TDI)、测试数据输出(TDO)、测试方式选择端(TMS)、测试时钟(TCK)和复位信号(TRST)允许外部访问。图3是在NoC体系的结构中为路由节点和资源节点添加边界扫描单元构成的TDI和TDO链路。

图3 NoC系统的TDI和TDO链路

其中,每个路由节点和资源节点均具有被外部访问的TDI、TDO、TMS、TCK和TRST信号端口,通过具有串行级联、配置灵活、电路简单等特点的菊花链结构将资源节点和路由节点的TDI和TDO,以TDI→TDO→TDI…的方式串联成NoC系统的边界扫描链路。所有的TMS、TCK和TRST信号端口连接在一起,并且利用Verilog HDL语言描述的TAP控制器、指令寄存器和测试数据寄存器实现整个NoC系统的边界扫描测试。

3放大器资源节点设计

由于其他的资源节点功能电路较为简单,其接口设计与本节设计的接口电路设计大致相同,本文主要以放大器资源节点为例介绍资源节点电路设计和接口电路设计。

3.1 放大器资源节点电路设计

本文以放大器芯片为核心实现放大器资源节点硬件设计。电路图如图4所示,主要包括前端处理和放大部分。前端处理部分采用π型网络结构设计75 Ω的阻抗匹配电路使得获取输入信号的功率最大化,选用高增益、低功耗、低噪声的AD8056放大芯片设计滤波器,切除信号干扰噪声获取干净无毛刺的波形信号;放大部分是选用低噪声放大芯片AD8056设计理论值为11倍的模拟小信号放大器。

图4中,TES0、TEST1、TEST2为放大器资源节点测试端口,用于获取端口信息,判断该资源节点故障及分析故障点位置。

图4 放大器电路

3.2 接口电路设计

边界扫描测试系统运用菊花链结构串联路由节点和资源节点间的TDI和TDO链路。当测试矢量从TDI链路到资源节点或测试响应从资源节点到TDO链路时,需接口电路对资源节点的测试矢量和测试响应处理。

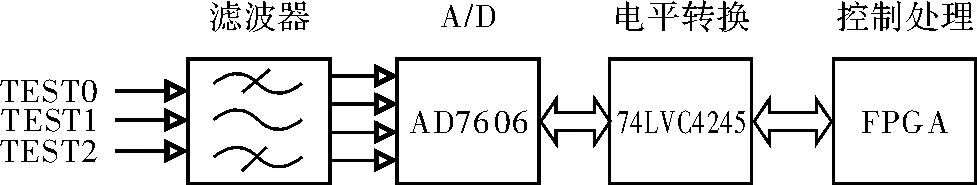

放大器资源节点以测试端口为对象设计接口电路,由放大器TES0、TEST1、TEST2测试端口分析,TES0、TEST1、TEST2的信号属性是模拟量。

综上分析,得出放大器资源节点接口电路框图,如图5所示。图中主要分为两大部分:A/D模块和控制处理模块(FPGA内部Verilog HDL语言描述)。其中,TES0、TEST1、TEST2测试端口与A/D模块的3个输入通道相连。控制处理模块执行TDI扫描链传输的测试命令;控制启动A/D模块采集通道模拟量和电平转换,得出的测试响应通过TDO扫描链路移位输出,完成一次边界扫描技术对放大器资源节点端口的测试。最后,分析、处理测试矢量和测试响应,以判断放大器资源节点故障及分析故障点位置。

图5 接口电路框图

4电气分析与电路板设计

4.1 叠层设计

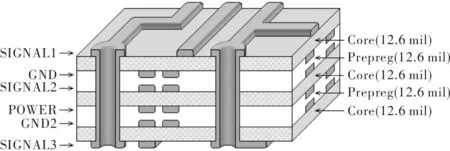

信号层、电源层、地层的规划、走线宽度与密度直接影响电路板设计的层数及整个系统的稳定性。由于FPGA的型号器件具有528个用户I/O口,且封装是29×29型号的BGA,通过计算,如果线宽和安全距离均>5 mil(1 mil=0.025 4 mm),则要将所有I/O口以及配置管脚扇出,至少需要总层数为8层。考虑现有工艺、干扰和性价比等问题,以PCB层数为6进行设计。总体的叠层方案是:信号1→地层2→信号3→电源4→地层5→信号6,如图6所示。两地层将信号层与电源层隔开,以减少干扰。

图6 叠层分布

4.2 电源设计

整个系统电压需求为1.2 V、2.5 V、3.3 V、+5 V和-5 V。本设计的输入电源电压是+5 V和-5 V,需要设计1.2 V、2.5 V、3.3 V的稳压电源模块。以低损耗、线性高的稳压芯片为核心,采用滤波网络电路,设计纹波电压小、精确度高的电源模块。

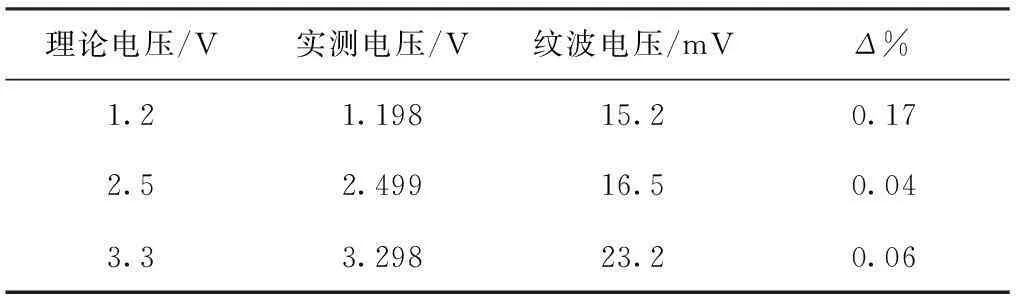

采用1.2 V、2.5 V、3.3 V的稳压集成芯片型号依次为SPX3819、AMS11117-3.3、LP38692MP-ADJ。为了给FPGA输送纹波电压小的电源,在靠近FPGA电源输入端增加电感、电容和0 Ω电阻组成的低通滤波网络电路,保障电源的电压纹波系数在FGPA可接受的范围内。同时为了尽量减少同一个电源电压给FPGA不同电压组之间供电产生的影响,在FPGA不同电压组之间增加的电阻隔离。表1是分别使用Agilent六位半万用表、泰克数字示波器对电路板实际工作电压的电压和纹波测量的结果,实测电压的有效位只保留3位,其中Δ%=(理论电压-实测电压)/理论电压。测量结果表明电源模块的电压纹波小、精度高。

表1 电源模块参数

5结果与分析

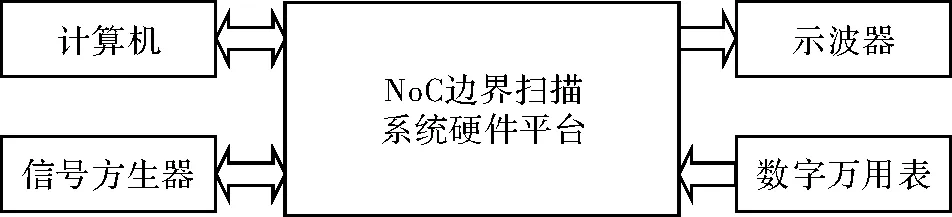

本文以FPGA为核心器件设计了9个资源节点电路的NoC边界扫描测试系统,使用Agilent六位半万用表和泰克的数字示波器对整个硬件功能进行测试。测试组成结构包括测试软件、信号发生器、示波器和万用表,如图7所示。

图7 测试组成结构

测试结果表明,所有的资源节点电路和边界扫描链路功能正常,在设置故障的情况下,利用边界扫描技术将故障诊断出来。本文以放大器资源节点为例阐述具体的测试结果。

图8在没有设置故障的情况下输入正弦波幅值为100 mV频率为1 kHz的放大器源节点输入波形。

图8 模拟放大器资源节点输入波形

图9在没有设置故障的情况下,输入正弦波幅值为100 mV,频率为1 kHz的放大器源节点响应波形。

图9 模拟放大器资源节点输出波形

经测量响应波形的电压幅值是1.05 V,输入波形电压幅值为1.00 V,计算电压实际放大倍数为Av=10.5。结果表明模拟放大器在信号波形无明显失真的情况下正常工作。

在设置放大器资源节点故障时,100 mV频率为1 kHz或者2 kHz的放大器源节点响应的波形不是设计所需要的波形。表2是针对发生故障时选择60 mV标准直流电压输入,利用边界扫描技术检测放大器TEST0、TEST1、TEST2的端口电压。由端口测试数据可知放大器资源节点电路中放大电路的短路和开路故障。

表2 获取的测试端口电压

对所有资源节点的测试表明,NoC边界扫描测试系统硬件设计的各模块功能正常,可准确地找到故障点,达到预期的设计效果。

6结束语

本文以FPGA为核心器件实现了2D-Mesh网络结构的NoC边界扫描测试系统的电路设计。该设计在具有通用性好和性价比高的情况下,利用较少的管脚实现故障诊断和定位,为研究NoC系统的边界扫描技术提供了良好的硬件平台。

参考文献

[1]许川佩,唐海,胡聪.基于FPGA的NoC硬件系统设计[J].电子技术应用,2012,38(2):118-123.

[2]赵建武,师奕兵,王志刚.片上网络FIFOs的内自建测试方法研究[J].仪器仪表学报,2009,30(8):1768-1772.

[3]欧阳一鸣,贺超,梁华国.NoC架构下异构IP核的并行测试方法[J].电子学报,2013,41(12):2391-2396.

[4]Reza N P,Nafiseh M.A fully parallel BIST-based method to test the crosstalk defects on the inter-switch links in NoC [J].Microelectronics Journal,2013,44(3):248-257.

[5]Muhammad A W,Kees G.TeMNOT:A test methodology for the non-instrusive online testing of FPGA with hardwired network on chip [J].Microprocessors and Microsystems,2012,37(2):129-146.

[6]陈寿宏,颜学龙,黄新.基于网络的混合信号边界扫描测试系统的设计与实现[J].计算机测量与控制,2012,20(5):1168-1182.

[7]李惠民,沈海斌.不规则Mesh NoC上基于路由表的路由[J].计算机工程,2013,39(10):279-286.

[8]许川佩,任智新.基于FPGA的NoC路由节点的设计[J].微电子学与计算机,2012,29(8):53-57.

[9]李鑫,刘伟.支持边界扫描测试的电路设计[J].无线电通讯技术,2009,35(6):41-44.