可编程逻辑器件CPLD和FPGA的特点和应用

2015-12-30田生宏田培成

田生宏 田培成

(西安理工大学高等技术学院,陕西 西安710082)

目前,大量使用的可编程逻辑器件是CPLD和FPGA,产品种类很多,均可实现任何数字逻辑功能。设计者可以利用CPLD和FPGA,通过原理图输入法或硬件描述语言设计一个数字系统,使之完成特定的功能,并且能运用软件仿真的方法来验证设计的正确性。CPLD和FPGA用于开发数字逻辑电路,可以缩短设计时间,减少集成电路数目和降低成本,极大地提高系统的可靠性。近年来,诞生了一些新型的CPLD和FPGA器件,集成度高,可以替代几十甚至几千块通用IC芯片,其单片逻辑门数已达到上百万门,可实现的逻辑功能也越来越强。

在可编程逻辑器件的发展过程中,不同厂家对新型PLD器件的叫法不尽相同,对CPLD和FPGA的分类标准也有差异,人们通常把基于乘积项技术和EEPROM工艺或Flash Memory工艺的器件称为CPLD,把基于查找表技术和SRAM工艺的器件称为FPGA(也有些资料将这两种器件都称为CPLD或都称为FPGA)。这样给使用和选择带来了不便甚至困惑,本文按一般的分类方法,分别介绍这两种可编程逻辑器件各自的特点,以期给使用者以帮助。

1 复杂可编程逻辑器件CPLD

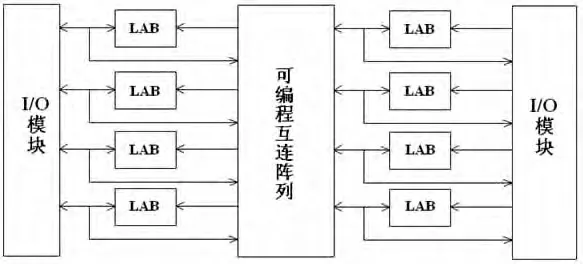

CPLD是从SPLD发展而来的高密度PLD产品,目前CPLD的产品种类繁多,各具特色,但其构成基本相同。如图1所示为CPLD的结构示意图,它由若干个逻辑阵列块(LAB)、可编程互连阵列(PIA)和可编程的输入/输出模块(IOB)组成。

图1 CPLD的结构示意图

CPLD大都采用分区阵列结构,即将整个器件分成若干个逻辑阵列块(Logic Array Block,LAB),每一个LAB实际上就是许多PAL/GAL阵列组成的SPLD组合,这些PAL/GAL阵列常被称为宏单元(macro cell)。在通常情况下,每个宏单元包括可编程的与门阵列、乘积项选择矩阵、或门阵列以及一个可编程的寄存器。根据器件类型的不同,CPLD中可以包含2~64个相同的LAB,可以容纳上万个等效的宏单元。

这些LAB经过内部的可编程互连阵列(Programmable Interconnect Array,PIA)进行互连,从而实现比较复杂的逻辑功能。

可编程的输入/输出模块(Input/Output Block,IOB)允许每个I/O引脚单独配置成输入、输出或双向工作方式。所有I/O引脚都有一个三态缓冲器,它可以由某个全局输出使能信号控制,也可以把使能端直接连接到地或电源上。

CPLD一般采用CMOS工艺和EEPROM或Flash Memory等先进技术、具有密度高、速度快和功耗低等性能。采用CPLD设计数字系统,可以使系统性能更优越。

2 现场可编程门阵列FPGA

现场可编程门阵列(FPGA)是另一种重要的可编程逻辑器件。FPGA在原理上与CPLD不同,FPGA的内部不使用PAL/GAL类型的逻辑,许多FPGA都使用查找表(Look-Up Table,LUT)这种存储器型的逻辑块,并包括小规模的门阵列和触发器电路,代替了CPLD中的与或逻辑结构,同时,因为FPGA含有更多的逻辑块,含有更多的互连单元,它使用与CPLD不同的可编程互连工艺,从而提供更灵活的布线功能,因而FPGA显得更为灵活。

查找表本质上就是一个RAM。目前FPGA中多使用四输入的LUT,所以每一个LUT可以看成一个有4位地址线的16×1的RAM。当用户通过原理图或HDL语言描述了一个逻辑电路以后,FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM。这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

FPGA主要由可配置逻辑块(Configurable Logic Block,CLB)、输入/输出模块(Input/Output Block,IOB)和可编程互连线(Programmable Interconnect,PI)组成。

可配置逻辑块(CLB)是FPGA的基本结构单元,能够实现逻辑函数。CLB一般由函数发生器、数据选择器、触发器和信号变换电路等部分组成。例如,在Xilinx公司的Spartan-Ⅱ型号的FPGA中,一个CLB包括两个SLICE(SLICE是组成CLB的基本单元),每个SLICE包括两个LUT、两个触发器和相关逻辑。SLICE可以看成是Spartan-Ⅱ实现逻辑的最基本的结构。在通常情况下,FPGA中的逻辑单元通过查找表的功能来实现组合逻辑函数,查找表实际上取代了CPLD中与门/或门阵列。

输入/输出模块(IOB)分布于器件四周,提供内部逻辑与外围引脚间的连接。

可编程互连线(PI)由许多金属线构成,以提供高速可靠的内部连接,将CLB之间、CLB和IOB之间连接起来构成复杂逻辑。

实际的FPGA中有很多个查找表用来配置可编程互连线的连接以及控制I/O引脚的连接。

3 CPLD和FPGA的比较

CPLD和FPGA的产品种类较多,均能实现各种逻辑功能,用于开发各类数字系统,但它们又有各自的特点:

1)CPLD更适合完成各种算法和组合逻辑,FPGA更适合于完成时序逻辑。

2)在编程上FPGA比CPLD具有更大的灵活性。CPLD通过修改具有固定内连电路的逻辑功能来编程,FPGA主要通过改变内部连线的布线来编程;FPGA可在逻辑门上编程,而CPLD是在逻辑块上编程。

3)FPGA的集成度比CPLD高,具有更复杂的布线结构,能实现更复杂的逻辑功能。

4)CPLD比FPGA使用起来更方便。CPLD的编程采用EEPROM或FLASH技术,无需外部存储器芯片,使用简单。而FPGA的编程信息需存放在外部存储器上,使用方法复杂。

5)CPLD的速度比FPGA快,并且其传输时间具有较大的可预测性。这是由于FPGA是门级编程,并且基本逻辑单元之间采用分布式互联;而CPLD是逻辑块级编程,其内连电路是固定的。

6)在编程方式上,CPLD主要是基于EEPROM或FLASH存储器编程,编程次数可达上万次,优点是系统断电时编程信息也不丢失。FPGA大部分是基于SRAM编程,编程信息在系统断电时丢失,每次上电时,需从器件外部将编程数据重新写入SRAM中。其优点是可以编程任意次,并可在工作中快速编程。

7)CPLD保密性好,FPGA保密性差。

因为CPLD和FPGA具有各自的特点,用CPLD和FPGA设计数字系统时需要不同的逻辑设计技巧。FPGA是细粒器件,其基本单元和路由结构都比CPLD的小,FPGA是“寄存器丰富”型器件(即其寄存器与逻辑门的比例高),而CPLD正好相反,它是“逻辑丰富”型的,很多设计人员偏爱CPLD是因为它简单易用和高速的优点。CPLD更适合逻辑密集型应用,而FPGA则更适用于寄存器密集型设计。

数字系统的设计人员可以采用各种结构的芯片来完成同一逻辑功能,设计时需要在设计规模、速度、芯片价格及系统性能要求等方面进行平衡,选择最佳结果。设计者选定CPLD或FPGA器件、确定硬件方案后,再根据设计要求,采用硬件描述语言VHDL对系统的逻辑功能进行描述与编程,然后利用专用软件平台进行编译、仿真和测试,直至实现预期功能,完成设计。最后利用专用设备将编程代码下载至器件中,即完成了系统样机的制作。如何使用硬件描述语言进行PLD器件的设计,可查阅其它资料及有关书籍。