一种极低功耗自偏置CMOS带隙基准源

2015-12-29黑龙江大学电子工程学院王春雷邱成军

黑龙江大学电子工程学院 吕 阳 王春雷 朱 杰 邱成军

一种极低功耗自偏置CMOS带隙基准源

黑龙江大学电子工程学院 吕 阳 王春雷 朱 杰 邱成军

基于CMSC 0.18um CMOS工艺,设计了一种自偏置结构带隙基准源,利用自偏置结构能够省略启动电路。所有MOS管工作在亚阈值范围,电路总功耗能够降低到nA级。利用华大九天Aether软件验证平台,仿真结果表明,电路最低工作电源电压为0.8V,在-40-80度之间,温度系数27ppm/℃。在温度27℃、电源电压0.8V时,输出基准电压为543mV,低频电源电压抑制比为90dB,高频为46dB,功耗仅为4.2nW,电路面积为0.05mm。

带隙基准源;低功耗;自偏置

0 引言

在模拟电路、射频电路和数字系统中,带隙基准电路是一个基本的电路模块,被广泛应用于A/D转换器、电压比较器、LDO、PLL等电路中[1]。而且随着便携式电子产品的迅速发展,功耗成为现代集成电路产品的关键性能之一,所以设计一种低功耗带隙基准电路具有重要意义。相对于传统带隙,电路中存在运放,很难使带隙电路的功耗降低到nA级,所以本文基于Oscar E.Mattia和Hamilton Klimach[5]等人所设计的自偏置带隙基准电路的基础上,利用NMOS管和PMOS管构成的两个自偏置结构[2],提出了一种新的电路结构,本课题带隙基准电路的功耗可以低至4.2nW,同时也具有很高的电源电压抑制比。

图1 带隙基准整体电路图

1 带隙基准电路结构和原理

我们采用的低功耗自偏置CMOS带隙基准源结构[5]如图1所示,在该电路结构中,双极型晶体管的结电压由两个NMOS管M1、M2栅源电压钳制,流经双极型晶体管的发射极电流由M9和M8形成的电流镜结构决定。因此,可以适当设计M8、M9管的电流比例,以及M1管和M2管的宽长比,就能够得到一个 非零的平衡点,从而可以对具有负温度系数的 BJT和具有正温度系数的MOSFET 进行线性叠加,来产生一个与温度无关的基准输出电压。M13、M14管为dummy管,为了后续版图的匹配。

1.1 PTAT电压

根据ACM MOSFET的模型,工作在亚阈值区域的MOS管漏极电流可以表示为:

如电路图1所示,PTAT电压由两对self-cascode (SC)结构产生,这两对SC结构由M2、M4、M6和M3、M5、M7晶体管组成。所以可以得到:

因此,利用公式(1)和公式(2)可以得到公式(3):

从公式中我们可以看出,PTAT电压为对数函数关系,相对变化比较小,如果要需要一个高温度梯度,应需串联多个SC结构,总PTAT电压是由M2、M4和M6漏源电压的总和提供。如公式(4)所示:

根据实际情况,通过调整流经每个器件的电流和尺寸比适当地设计公式里面的比例常数。

1.2 VE分压电路和BJ T偏置电路

晶体管的发射极电流IE由公式(7)给出:

其中ISE是反向饱和电流,VE是发射极-基极电压,m是坡度因子。

从公式(7)中可以看出,发射极电压依靠工艺参数,这个参数设置了电路的平衡点,即MOSFET的阈值电压VT0和电流密度ISQ和结反向饱和电流ISE。

1.3 基准电压源

所以根据公式(6)和公式(4)就可以得到基准电压公式(9):

2 仿真结果

采用CSMC 0.18um工艺库,利用华大九天公司Aether工具对电路进行功耗、线性度、温度系数和电源抑制比仿真。电路功耗和输出电压的仿真结果如图2所示,由图2可知,带隙的最低开启电压为0.8V,此时的输出电压为0.545V,当电源电压为1.8V时,输出0.550V,所以线性度为3683ppm/°V,消耗总电流仅为5.26nA。

图2 功耗和线性度仿真图

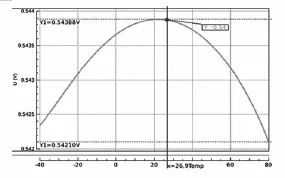

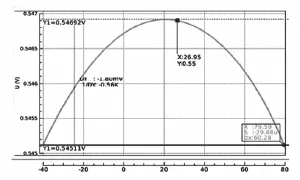

当温度在-40℃-80℃范围内变化,输出电压随温度变化的情况分别如图3和图4所示,图3和图4的电源电压分别为0.8V和1.8V,因此可计算出温度系数都为27ppm/℃。

图3 0.8V电源电压下温度系数仿真图

图4 1.8V电源电压下温度系数仿真图

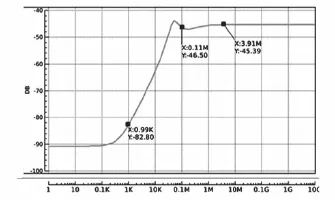

对电路进行交流仿真,可以得到带隙的电源电压抑制比仿真结果图,如图5和图6所示,对于一般的带隙基准电路,电源抑制比要求在60dB以上就满足要求。图5为0.8V电源电压下,温度系数的仿真图,低频时,可以达到-90dB,高频时,-44dB。当电源电压增大到1.8V时,电源抑制比基本不变。本文设计的带隙在功耗上小于其他文献,如表1所示。图7是本文带隙基准电路的版图。

图5 0.8V电源电压下电源抑制比仿真图

图6 1.8V电源电压下电源抑制比仿真图

表1 于其他文献对比

图7 版图

3 结论

设计了一种适用于低功耗SOC系统和移动电子产品的带隙基准模块,基于CSMC 0.18um工艺库。使电路的所有MOS管都工作在亚阈值区域来降低功耗,采用华大九天Aether模数验证平台,结果证明,电源电压0.8V时,整个电路的功耗仅为4.26nW,而且低频电源电压抑制比能达到-90dB。

[1]邹勤丽,汤晔.一种低功耗无运放的带隙基准电压源设计[J].电子与封装,2015,02:22-24+32.

[2]Lee,E K F.Low voltage CMOS bandgap references with temperature compensated reference current output[J].Circuits and Systems (ISCAS),Proceedings of 2010 IEEE International Symposium on,2010.1643-1646.

[3]Dalton Colombo, Felipe Werle, Gilson Wirth,Sergio Bampi.A CMOS 25.3×10-6℃-1 Bandgap Voltage Reference using Self-Cascode Composite Transistor[J].IEEE. 2012.

[4]李燕霞,龚敏,高博.基于0.18um的无电阻无运放低功耗带隙基准源设计[J].电子与封装,2015,01:24-27.

[5]Oscar E Mattia, Hamilton Klimach.0.7V,8 nW,9 ppm/℃ Resistorless Sub-Bandgap Voltage Reference in 0.18 μmCMOS [J].2014.

[6]Leung K.N.,Mok P.K.T., “A Sub-1-V 15 ppm/℃CMOS Bandgap VoltageReference Without Requiring Low Threshold Voltage Device.”[J]IEEE Journal of Solid-State Circuit. 2002;37(4):526-530.

吕阳(1991-),黑龙江黑河人,黑龙江大学,硕士。

王春雷(1992-),黑龙江肇东人,黑龙江大学,硕士。

朱杰(1992-),女,黑龙江大庆人,黑龙江大学,硕士。

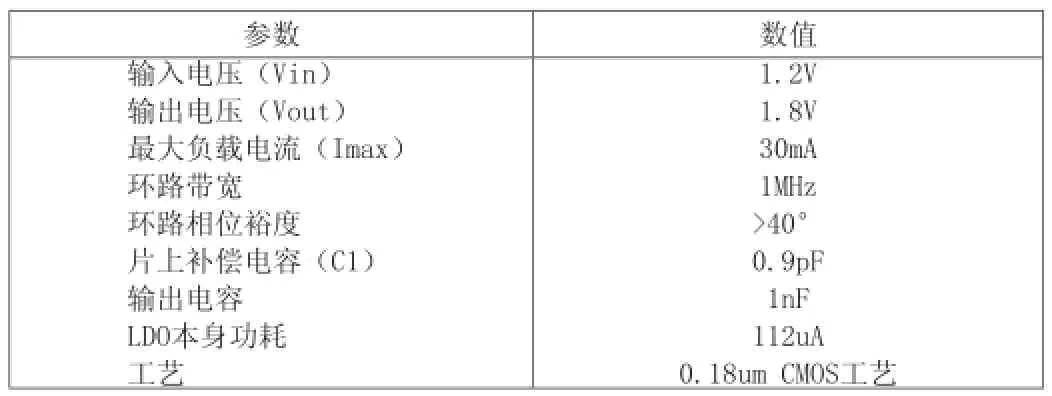

表1 LDO的性能参数

3 结论

VCCS模块采用极小的片内电容(本设计采用的是0.9pF电容)产生零点,从而稳定整个LDO反馈回路。本设计的LDO输入电压为1.2V,输出电压为1.8V,最大负载电流30mA,环路带宽1MHz,相位裕度大于40°,片上补偿电容为0.9pF,输出电容为1nF,LDO本身功耗为112μA。本方法有效的减小了版图面积,降低了生产成本。

参考文献

[1]C.Simpson.Linear and Switching VoltageRegulator Fundamentals.National Semiconductor Application Note,1999.

[2]范华,冯全源.基于LDO稳压器的运放设计[J].半导体学报,2005,26(10):354-360.

[3]F.Good enough.Low dropout linear regulators. Electronic Design,1998,5(3):65-77.

作者简介:

胡冰妍(1991—),女,吉林四平人,工作单位吉林大学电子科学与工程学院,硕士研究生在读。

常玉春(1973—),男,吉林长春人,工作单位吉林大学电子科学与工程学院,职称教授,博士生导师。

李海彬(1991—),男,安徽界首人,吉林大学电子科学与工程学院,硕士研究生在读。

邱成军(1965-),男,黑龙江哈尔滨人,黑龙江大学教授、博士。